# **CM**5

# NI Programmer's Handbook

NI Version 2.2 (CM-5E)

Thinking Machines Corporation

The Connection Machine System

# NI Programmer's Handbook

NI Version 2.2 (CM-5E), June 1994

**Thinking Machines Corporation**

The information in this document is subject to change without notice and should not be construed as a commitment by Thinking Machines Corporation. Thinking Machines reserves the right to make changes to any product described herein.

Although the information in this document has been reviewed and is believed to be reliable, Thinking Machines Corporation assumes no liability for errors in this document. Thinking Machines does not assume any liability arising from the application or use of any information or product described herein.

Connection Machine<sup>®</sup> is a registered trademark of Thinking Machines Corporation. CM, CM-2, CM-200, CM-5, and CM-5e are trademarks of Thinking Machines Corporation. CM-5 Scale 3, and DataVault are trademarks of Thinking Machines Corporation. CMOST, CMAX, and Prism are trademarks of Thinking Machines Corporation. C<sup>\*®</sup> is a registered trademark of Thinking Machines Corporation. C<sup>\*®</sup> is a registered trademark of Thinking Machines Corporation. Paris, \*Lisp, and CM Fortran are trademarks of Thinking Machines Corporation. CMHFB, CMMD, CMSSL, and CMX11 are trademarks of Thinking Machines Corporation. CMview is a trademark of Thinking Machines Corporation. Scalable Computing (SC) is a trademark of Thinking Machines Corporation. Scalable Disk Array (SDA) is a trademark of Thinking Machines Corporation. Thinking Machines<sup>®</sup> is a registered trademark of Thinking Machines Corporation. SPARC and SPARCstation are trademarks of SPARC International, Inc. Sun, Sun-4, and Sun Workstation are trademarks of Sun Microsystems, Inc. UNIX is a trademark of UNIX System Laboratories, Inc. The X Window System is a trademark of the Massachusetts Institute of Technology.

Copyright © 1994 by Thinking Machines Corporation. All rights reserved.

Thinking Machines Corporation 245 First Street Cambridge, Massachusetts 02142-1264 (617) 234-1000

# Contents

¥

~

| Figures       xv         About This Manual       xvii         Customer Support       xxi |                                                   |   |  |

|------------------------------------------------------------------------------------------|---------------------------------------------------|---|--|

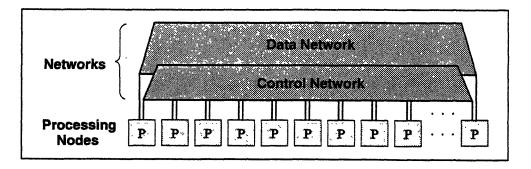

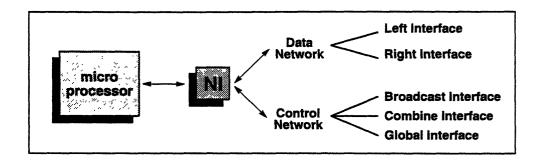

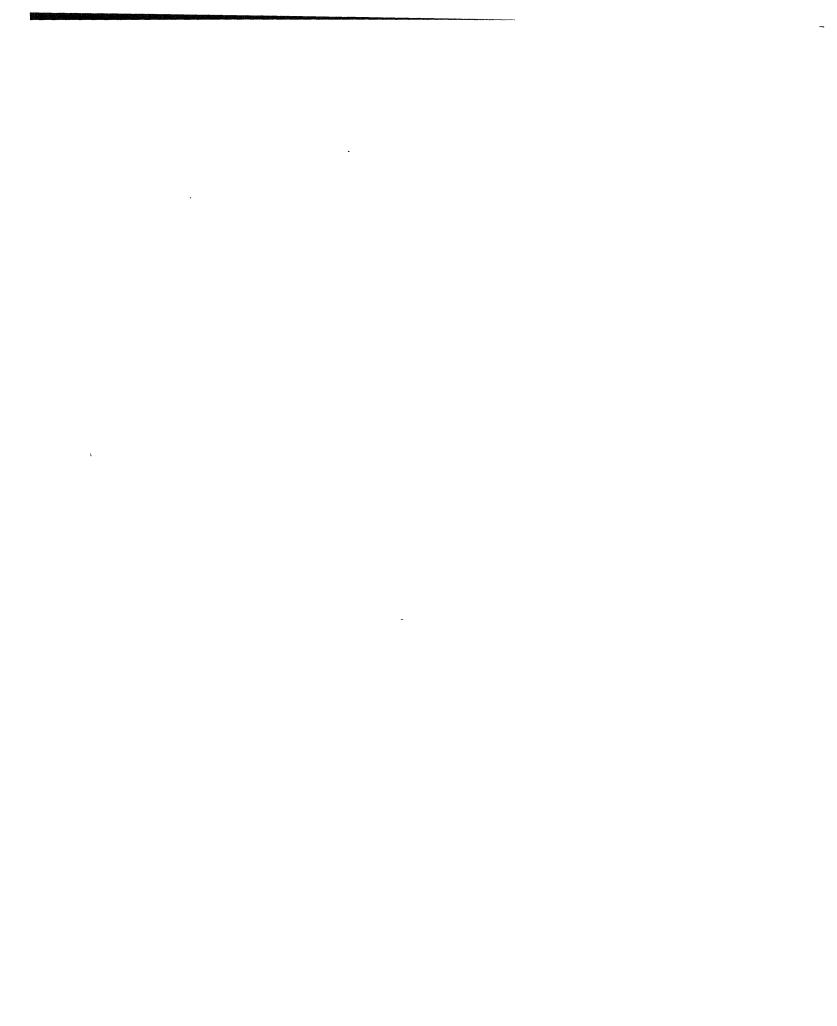

| Chapter 1                                                                                | The CM-5 Network Interface   3                    | • |  |

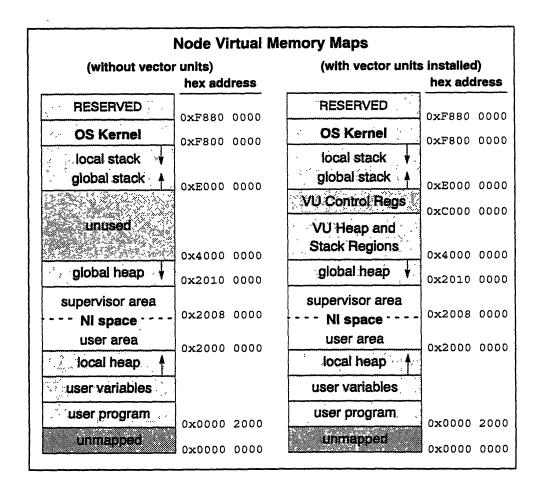

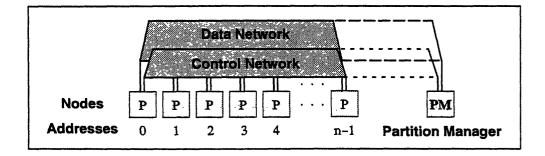

| 1.1                                                                                      | The CM-5 System: Nodes and Networks 4             | ļ |  |

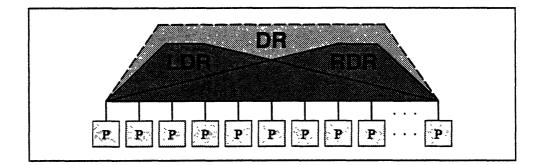

|                                                                                          | 1.1.1 The CM-5 Networks 4                         | ŀ |  |

|                                                                                          | The Data Network 4                                | ŀ |  |

|                                                                                          | The Control Network 5                             | ; |  |

|                                                                                          | For the Curious: The Diagnostic Network           | ; |  |

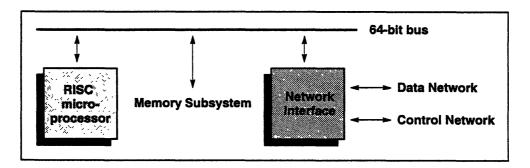

|                                                                                          | 1.1.2 Processing Nodes 5                          | ; |  |

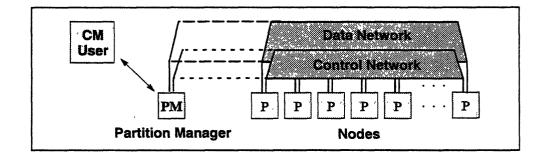

|                                                                                          | 1.1.3 Partitions and Partition Managers           | 5 |  |

|                                                                                          | 1.1.4 Programming Models 7                        | 7 |  |

|                                                                                          | User Programming Model                            | 7 |  |

|                                                                                          | OS Programming Model                              | 1 |  |

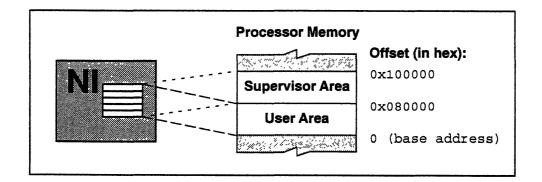

| 1.2                                                                                      | The NI Chip                                       | 3 |  |

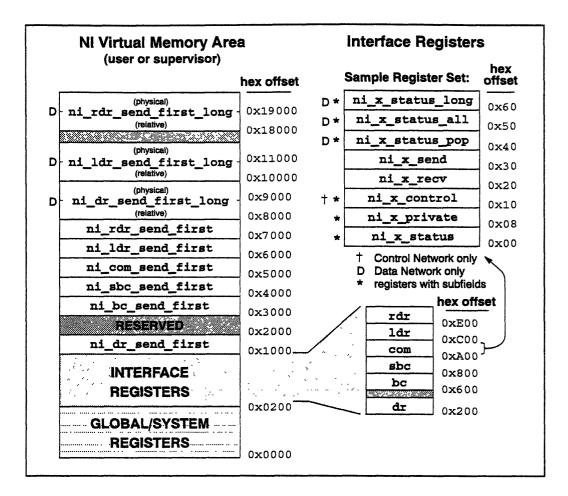

| 1.3                                                                                      | The NI Registers                                  | 3 |  |

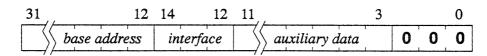

|                                                                                          | 1.3.1 For the Curious: The NI Base Address        | ) |  |

|                                                                                          | 1.3.2 NI Register Types 11                        | L |  |

|                                                                                          | 1.3.3 NI Register and Field Names 12              | 2 |  |

|                                                                                          | 1.3.4 NI Register and Field Programming Constants | 5 |  |

|                                                                                          | Finding the Constant You Need 13                  | 3 |  |

|                                                                                          | Register Constants 13                             | 3 |  |

|                                                                                          | Field Constants 14                                | ŀ |  |

|                                                                                          | NI Base Address Constant 14                       | ŀ |  |

|                                                                                          | 1.3.5 C Macros Useful for Writing NI Code 14      | ŀ |  |

|                                                                                          | Finding the C Macro You Need 15                   | 5 |  |

| 1.4                                                                                      | Interrupts 15                                     | ; |  |

| 1.5                                                                                      | NI Reset                                          | 5 |  |

| 1.6                                                                                      | Using This Manual Effectively 16                  | 5 |  |

| 1.7                                                                                      | WARNING: Experiment at Your Own Risk              | 7 |  |

| Chapter 2 | A Generic Network Interface                                                                                                                            | 19       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1       | Network Interface Registers                                                                                                                            | 19       |

| 2.2       | Network Messages                                                                                                                                       | 20       |

|           | 2.2.1 Performance Note — Using Doubleword Operations                                                                                                   | 21       |

| 2.3       | Sending a Message                                                                                                                                      | 21       |

|           | 2.3.1 Message Discarding         2.3.2 Auxiliary Information                                                                                           | 22<br>22 |

|           | 2.3.3 Calculating ni_interface_send_first Addresses                                                                                                    | 23       |

|           | Send First Address Constants                                                                                                                           | 23       |

|           | 2.3.4 C Macros for Writing a Message                                                                                                                   | 24       |

| 2.4       | Receiving a Message                                                                                                                                    | 25       |

|           | 2.4.1 C Macros for Reading a Message                                                                                                                   | 25       |

|           | 2.4.2 Detecting Arrival of a Message                                                                                                                   | 26       |

|           | 2.4.3 Simulating the Arrival of a Message                                                                                                              | 26       |

| 2.5       | The Status Register                                                                                                                                    | 27       |

|           | 2.5.1 The "Send OK" Flag                                                                                                                               | 27       |

|           | <ul><li>2.5.2 The "Send Space" Field and "Send Empty" Flag</li><li>2.5.3 The "Receive OK" Flag and "Receive Length" Fields</li></ul>                   | 28<br>28 |

|           | 2.5.4 Reading the Status Register Fields                                                                                                               | 28       |

| 2.6       | Abstaining from an Interface — The Control Register                                                                                                    | 29       |

|           | 2.6.1 Effect of Abstain Flags                                                                                                                          | 30       |

|           | 2.6.2 Combine Interface Abstain Flags                                                                                                                  | 30       |

|           | 2.6.3 Reading and Writing the Abstain Flag                                                                                                             | 30       |

|           | 2.6.4 Use the Abstain Flags Safely                                                                                                                     | 31       |

|           | 2.6.5 Being a Good Neighbor                                                                                                                            | 31       |

| 2.7       | The Private Register                                                                                                                                   | 32       |

|           | <ul> <li>2.7.1 Message Receipt Interrupts — The Rec Interrupt Enable Flag</li> <li>2.7.2 Clearing the Interface's Send FIFO — The Lock Flag</li> </ul> |          |

|           | 2.7.2 Cleaning the Interface's Send FIFO — The Lock Flag<br>2.7.3 Grabbing the Receive FIFO Registers — The Rec Stop Flag.                             | 33<br>33 |

|           | 2.7.4 Blocking Unsent Broadcast Messages — The Send Stop Flag                                                                                          | 34       |

|           | 2.7.5 Detecting a Full Receive FIFO — The Receive Full Flag                                                                                            | 34       |

| 2.8       | Using a Generic Network Interface                                                                                                                      | 34       |

| 2.9       | From the Generic to the Specific                                                                                                                       | 35       |

|           |                                                                                                                                                        |          |

| Chapter 3 | The Data Network                                                                                                                                       | 37       |

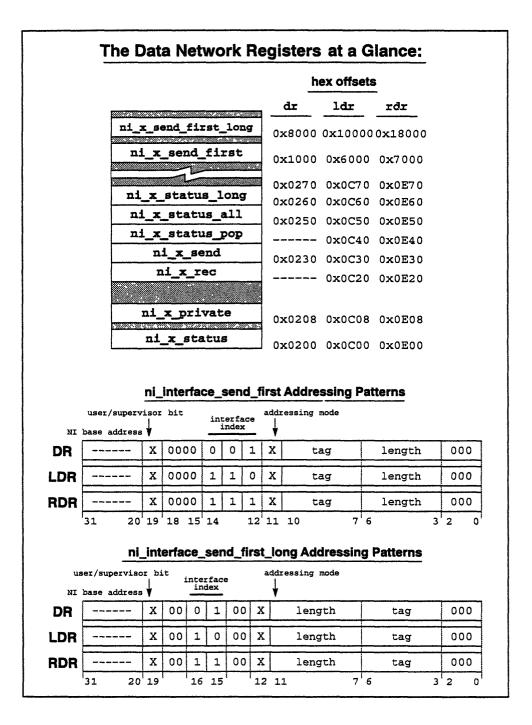

| 3.1       | The Data Network Register Interfaces                                                                                                                   | 38       |

| 3.2       | Data Network Messages                                                                                                                                  | 40       |

|           | 3.2.1 Short and Long Data Network Messages                                                                                                             | 40       |

#### Contents Nation with the contraction of the second second to the second structure and the second s

|     |           |                                                                                                                                                                                                                                                                                                    | 41<br>41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3 |           |                                                                                                                                                                                                                                                                                                    | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |           | -                                                                                                                                                                                                                                                                                                  | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.4 | Sending a | and Receiving Messages                                                                                                                                                                                                                                                                             | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 3.4.1     |                                                                                                                                                                                                                                                                                                    | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |           |                                                                                                                                                                                                                                                                                                    | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 3.4.2     |                                                                                                                                                                                                                                                                                                    | 45<br>45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |           |                                                                                                                                                                                                                                                                                                    | 45<br>46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 3.4.3     |                                                                                                                                                                                                                                                                                                    | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.5 | The Stati |                                                                                                                                                                                                                                                                                                    | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 3.5.1     | The Standard Status Registers                                                                                                                                                                                                                                                                      | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 3.5.2     | The "Status All" Alternate Status Register                                                                                                                                                                                                                                                         | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 3.5.3     | The "Status Pop" Register                                                                                                                                                                                                                                                                          | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 3.5.4     |                                                                                                                                                                                                                                                                                                    | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |           |                                                                                                                                                                                                                                                                                                    | 50<br>50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |           |                                                                                                                                                                                                                                                                                                    | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |           |                                                                                                                                                                                                                                                                                                    | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |           | Tag Fields and the Message-Counting Registers                                                                                                                                                                                                                                                      | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |           | Message Count Disabling                                                                                                                                                                                                                                                                            | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |           |                                                                                                                                                                                                                                                                                                    | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |           |                                                                                                                                                                                                                                                                                                    | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| •   |           | -                                                                                                                                                                                                                                                                                                  | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |           | -                                                                                                                                                                                                                                                                                                  | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.7 |           |                                                                                                                                                                                                                                                                                                    | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |           |                                                                                                                                                                                                                                                                                                    | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |           |                                                                                                                                                                                                                                                                                                    | 57<br>58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 38  |           |                                                                                                                                                                                                                                                                                                    | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |           |                                                                                                                                                                                                                                                                                                    | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |           | -                                                                                                                                                                                                                                                                                                  | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| .10 | -         |                                                                                                                                                                                                                                                                                                    | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |           |                                                                                                                                                                                                                                                                                                    | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

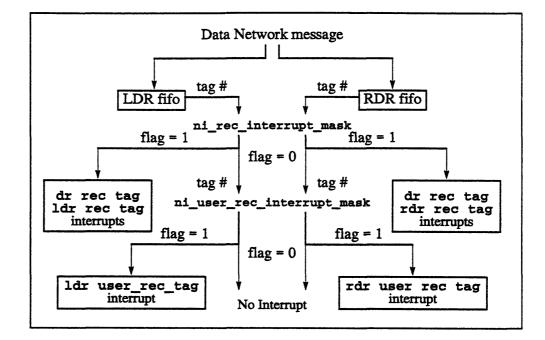

|     | Inter     | rupt-Driven Message Retrieval                                                                                                                                                                                                                                                                      | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | Send      | ing via LDR and RDR Simultaneously                                                                                                                                                                                                                                                                 | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 3.4       | 3.2.3<br>3.3 Data Net<br>3.3.1<br>3.4 Sending a<br>3.4.1<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.3<br>3.5 The State<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.4<br>3.5.5<br>3.5.6<br>3.6 The Priva<br>3.7.1<br>3.7.2<br>3.7.3<br>3.8 Interrupt<br>3.9 Data Net<br>.10 Examples<br>Send<br>Send<br>Inter | 3.3.1 Physical and Relative Addressing Modes         3.4 Sending and Receiving Messages         3.4.1 Sending Short Messages         3.4.2 Sending Long Messages         3.4.3 Receiving Long Messages         3.4.4 Sending Long Messages         3.4.5 Sending Long Messages         3.4.6 Sending Long Messages         3.4.7 Sending Long Messages         3.4.8 Receiving Messages         3.5 The Status Registers         3.5.1 The Standard Status Registers         3.5.2 The "Status All" Alternate Status Register         3.5.3 The "Status Pop" Register         3.5.4 Message Tags         User/Supervisor Tag Reservation         Tag Fields and Interrupts         Using CMOST Commands         to Set Up NI Interrupt Handlers         Tag Fields and the Message-Counting Registers         Message Count Disabling         Negative Message Count Interrupts         3.5.5 The Send and Receive State Fields         3.5.6 The Network-Done Flag         3.6 The Private Register         3.7.1 Triggering All Fall Down Mode         3.7.2 Detecting All Fall Down Mode         3.7.3 Resending All Fall Down Mode Messages         3.7.3 Resending All Fall Down Mode Messages         3.7.3 Resending All Fall Down Mode Messages         3.7.3 Resending All |

| Chapter 4 | The Con  | trol Network                                               | 65         |

|-----------|----------|------------------------------------------------------------|------------|

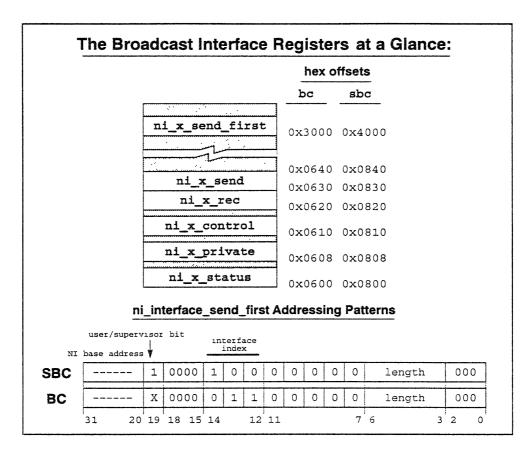

| 4.1       | The Broa | dcast Interface                                            | 66         |

|           | 4.1.1    | Broadcast Register Interfaces                              | 66         |

|           | 4.1.2    | Broadcast Messages                                         | 67         |

|           | 4.1.3    | Sending Broadcast Messages                                 | 68         |

|           | 4.1.4    | Auxiliary Information                                      | 69         |

|           | 4.1.5    | Receiving Broadcast Messages                               | 69         |

|           | 4.1.6    | The Broadcast Status Register                              | 70         |

|           | 4.1.7    | Abstaining from the Broadcast Interface                    | 71         |

|           | 4.1.8    | The Broadcast Private Register                             | 71         |

|           | 4.1.9    | Broadcast Interface Examples                               | 72         |

|           |          | Sending and Receiving a Message                            | 72         |

| 4.2       | The Com  | bine Interface                                             | 73         |

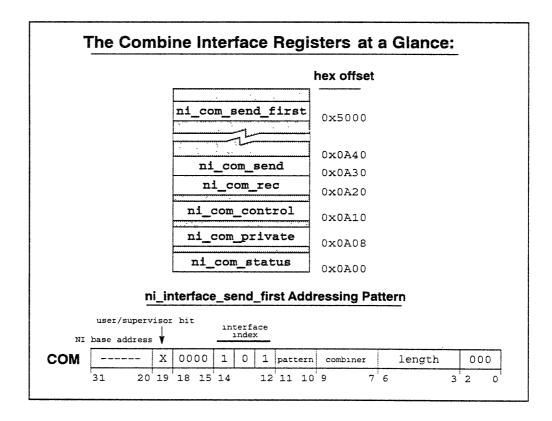

|           | 4.2.1    | The Combine Register Interface                             | 74         |

|           | 4.2.2    | Combine Messages                                           | 75         |

|           | 4.2.3    | Sending Combine Messages                                   | 75         |

|           | 4.2.4    | Auxiliary Information                                      | 76         |

|           | 4.2.5    | Legal Combiner and Pattern Values                          | 77         |

|           | 4.2.6    | Receiving Combine Message                                  | 78         |

|           | 4.2.7    | The Combine Status Register                                | 78         |

|           | 4.2.8    | Scanning (Parallel Prefix) and Reduction Operations        | 79         |

|           |          | Scanning with Segments                                     | 80         |

|           |          | Addition Scan Overflow                                     | 80         |

|           | 4.2.9    | Network-Done Messages                                      | 81         |

|           |          | How Network-Done Works                                     | 82         |

|           |          | And Why You Should Care                                    | 83         |

|           | 4.2.10   | 5                                                          | 83         |

|           | 4.2.11   | The Combine Private Register                               | 85         |

|           |          | Empty Receive FIFO Interrupt                               | 85         |

|           |          | Clearing the Combine Send FIFO                             | 86         |

|           | 4.2.12   | Combine Interface Examples                                 |            |

|           |          | Sending and Receiving a Combine Message                    |            |

|           |          | Executing Scans and Reduction Scans                        | 88         |

|           |          | Executing a Network-Done Operation                         | 89         |

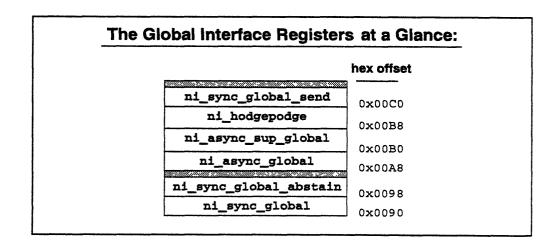

| 4.3       |          | bal Interface                                              | <b>9</b> 0 |

|           | 4.3.1    | The Three Global Register Interfaces                       | 91         |

|           | 4.3.2    | The Synchronous Global Interface                           | 91         |

|           |          | Sending and Receiving Messages                             | 92         |

|           |          | Abstaining from Synchronous Global Messages                | 92         |

|           |          | Synchronous Global Receive Interrupt                       | 93         |

|           |          | Supervisor Operations for the Synchronous Global Interface | 93         |

# Contents

|           | 4.3.3 The Asynchronous Global Interface       93         Sending and Receiving Messages       94         Asynchronous Global Receive Interrupt       95 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 4.3.4 The Supervisor Asynchronous Global Interface       95         Sending and Receiving Messages       95                                             |

|           | Supervisor Asynchronous Global Receive Interrupt 95                                                                                                     |

|           | 4.3.5 Global Interface Examples                                                                                                                         |

|           | Using the Asynchronous Global Interface                                                                                                                 |

|           |                                                                                                                                                         |

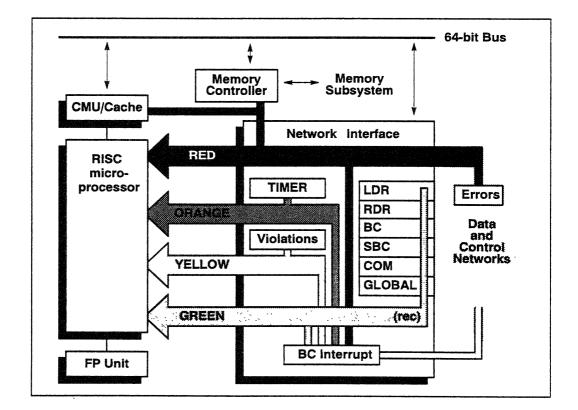

| Chapter 5 | NI Interrupts                                                                                                                                           |

| 5.1       | Interrupt Classes975.1.1 Disabling Bus Errors100                                                                                                        |

| 5.2       | Interrupt Pathways                                                                                                                                      |

|           | 5.2.1 Red Interrupts                                                                                                                                    |

|           | 5.2.2       Orange Interrupts       102         5.2.3       Yellow Interrupts       102                                                                 |

|           | 5.2.4 Green Interrupts                                                                                                                                  |

| 5.3       | The Interrupt Cause and Clear Registers                                                                                                                 |

| 5.4       | Interrupt Levels                                                                                                                                        |

| 5.5       | Broadcast Interrupts 106                                                                                                                                |

| 5.6       | Recovering from Interrupts 107                                                                                                                          |

| Chapter 6 | Other NI Interfaces and Features                                                                                                                        |

| 6.1       | The "Hodgepodge" Register 109                                                                                                                           |

| 6.2       | Node Address Registers                                                                                                                                  |

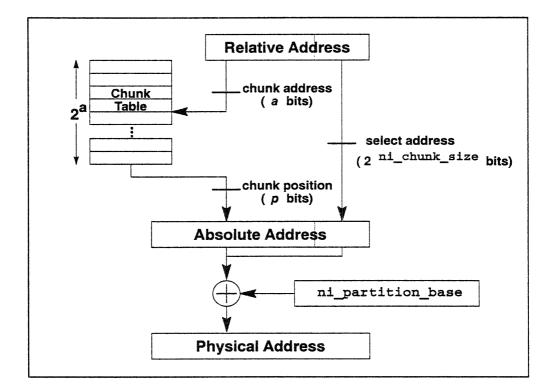

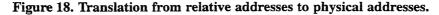

| 6.3       | NI Chunk Table and Address Translation                                                                                                                  |

|           | 6.3.1 Node Address Translation 110                                                                                                                      |

|           | 6.3.2 Chunk Sizes and Address Allocation                                                                                                                |

| 6.4       | 6.3.3 Modifying the Chunk Table 114<br>Combine Interface Flush 114                                                                                      |

| 6.5       | The NI Timer                                                                                                                                            |

| 6.6       | The Bad Address Register                                                                                                                                |

| 6.7       | NI Partition Configuration                                                                                                                              |

| 6.8       | Disabling the Control Network                                                                                                                           |

| 6.9       | NI Serial Number                                                                                                                                        |

| 6.10      | NI Reset                                                                                                                                                |

N. N

| Writing NI Programs 121                                                                                                                                                                                                                                                                                                                                                                |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Transferring Data between Nodes and the PM1217.1.1Sending Messages from the PM to Nodes1227.1.2Sending Messages from Nodes to the PM1237.1.3Signaling the PM1247.1.4For the Curious: Using the Data Network124                                                                                                                                                                         |  |  |

| Setting the Abstain Flags 124                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Broadcast Enabling 12                                                                                                                                                                                                                                                                                                                                                                  |  |  |

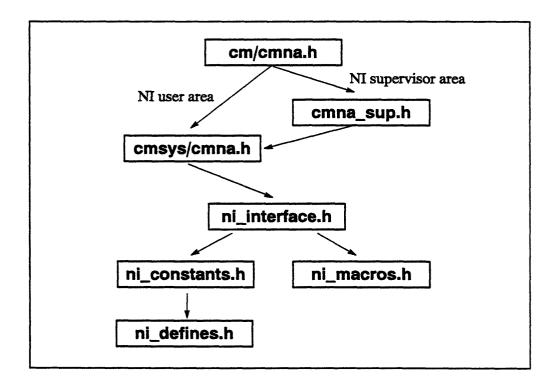

| NI Program Structure1277.4.1 The cmna.h Header File1277.4.2 Partition Manager Code1277.4.3 Node Code128The Node's "Main" Routine1287.4.4 Interface Code129                                                                                                                                                                                                                             |  |  |