## Introduction to iWarp

#### DISCLAIMER

The information provided in this manual describes the concepts and systems of the iWarp technology development program and is subject to change without notice. No representation or announcement of Intel products is expressed or implied.

The view, opinions, and/or findings contained in this manual should not be interpreted as representing the official policies, either expressed or implied, of the Defense Advanced Research Projects Agency or the Department of the Navy, Space and Naval Warfare Systems Command, or the position of Carnegie Mellon University.

#### ACKNOWLEDGEMENT

The work resulting in the concepts and systems described in this manual is supported, in part, by Defense Advanced Projects Agency (DoD), ARPA Order No. 4864, monitored by the Space and Naval Warfare Systems Command under Contract number 00039-C-0134 and Contract Number 00039-87-C-0254 and, in part, by Intel Corporation.

We particularly acknowledge the efforts of the Carnegie Mellon University, School of Computer Science, Warp team. This team included, Dr. H.T. Kung, his associates, and his students who provided the primary technical direction for iWarp technology.

#### TRADEMARKS

VMS is a registered trademark of Digital Equipment Corporation.

UNIX is a registered trademark of AT&T Bell Labortories.

Sun is a registered trademark of Sun Microsystems, Inc.

## CONTENTS

## 1 Introducing iWarp

| iWarp: System Building Blocks for High Performance Systems | 1-1  |

|------------------------------------------------------------|------|

| The Development Partnership                                | 1-1  |

| The Need                                                   | 1–2  |

| Computation and Communication Requirements                 | 1-4  |

| Comparing Requirements                                     | 1-5  |

| Communication Needs                                        | 1–6  |

| Application Examples                                       | 1-6  |

| A Sonar Example                                            | 1-7  |

| Implementing the Sonar Application on an iWarp Array       | 1-8  |

| Synergy between Communication Models                       | 1-8  |

| Fine-Grain Systolic Communication                          | 1-9  |

| Performance Analysis                                       | 1-9  |

| Advantages of the Systolic Model                           | 1–10 |

| Fundamental iWarp Concepts                                 | 1-11 |

| Integrated Communication and Computation                   | 1-11 |

| Balanced Communication to Computation                      | 1-11 |

| Independent Communication and Computation Elements         | 1-11 |

| Scalar and Vector Performance                              | 1–12 |

| iWarp Architecture Overview                                | 1-12 |

| iWarp Communication and Computation Models                 | 1-14 |

| Logical Connections                                        | 1–17 |

| iWarp Systems                                              | 1-18 |

| Configurations                                             | 1-19 |

| Single Board Array                                         | 1-20 |

| The Significance of iWarp                                  | 1–21 |

## 2 iWarp Hardware

| The iWarp Component    | 2-1 |

|------------------------|-----|

| Component Architecture | 2-1 |

| Computation Agent      | 2-3 |

| Register File Unit     | 2-3 |

| Local Memory Unit      | 2-4 |

| Program Store Unit     | 2-5 |

| Instruction Sequencing Unit | 2-6  |

|-----------------------------|------|

| Integer Logic Unit          | 2-6  |

| Floating-point Unit         | 2-7  |

| Streaming/Spooling Unit     | 2-8  |

| Communication Agent         | 2-9  |

| Instruction Formats         | 2–10 |

| The iWarp Boards            | 2-12 |

| Quad Cell Board             | 2-13 |

| Single Cell Board           | 2-14 |

| Single Board Array          | 2-15 |

| Local Memory                | 2-16 |

| The iWarp Cardcage Assembly | 2–17 |

| The iWarp System            | 2–19 |

| Diagnostics                 | 2-20 |

## 3 iWarp Software

| iWarp Software Architecture              | 3-1  |

|------------------------------------------|------|

| iWarp Host Environment                   | 3-3  |

| iWarp Program Development Tools          | 3–3  |

| iWarp Runtime Environment                | 3-6  |

| iWarp Runtime Libraries                  | 3-7  |

| iWarp System Support                     | 3-7  |

| Programming an iWarp System              | 3-8  |

| Apply: for Image Processing Applications | 3-10 |

| WEB Library Routines                     | 3-14 |

## **Appendix: Computational Models**

## Bibliography

## Glossary

## Index

## FIGURES

| FIGURE                                                                      | PAGE |

|-----------------------------------------------------------------------------|------|

| 1-1: An example of a two-dimensional iWarp torus array                      | 1–1  |

| 1-2: Applications with different computation and communication requirements | 1–5  |

| 1-3: Sonar application                                                      | 1–7  |

| 1-4: Sonar application on a 16-cell iWarp array                             | 1–8  |

| 1-5: Matrix multiply example                                                | 1–9  |

| 1-6: Time line of performance peak in matrix multiply example               | 1–10 |

| 1-7: iWarp system architecture                                              | 1–13 |

| 1-8: iWarp cell I/O capacity                                                | 1–14 |

| 1-9: Data pathways                                                          | 1–15 |

| 1-9 a and b : Express messages and systolic computation                     | 1–16 |

| 1-9 c and d: Spooling and streaming and memory-to-memory messages           | 1–16 |

| 1-9 e and f: Memory computation and combination                             | 1–17 |

| 1-10: Physical and logical buses                                            | 1–17 |

| 1-11: Logical buses support sharing of physical resources                   | 1-18 |

| 1-12: iWarp system configuration concept                                    | 1–19 |

| 1-13: iWarp system building blocks                                          | 1–20 |

| 1-14: iWarp Single Board Arrays and development systems                     | 1–21 |

| 2-1: iWarp cell                                                             | 2–1  |

| 2-2: iWarp component architecture block diagram                             | 2–2  |

| 2-3: Register File Unit                                                     | 2–3  |

| 2-4: Local Memory Unit                                                      | 2–4  |

| 2-5: Program Store Unit                                                     | 2–5  |

| 2-6: Instruction Sequencing Unit                                            | 2–6  |

| 2-7: Integer Logic Unit                                                     | 2–6  |

| 2-8: Floating-point Unit                                                    | 2–7  |

| FIGURE                                                             | PAGE |

|--------------------------------------------------------------------|------|

| 2-9: Streaming/Spooling Unit                                       | 2–8  |

| 2-10: Communication Agent                                          | 2–9  |

| 2-11: iWarp cell links                                             | 2–9  |

| 2-12: Message header                                               | 2–10 |

| 2-13: Compute and access instruction format                        | 2–11 |

| 2-14: iWarp Quad Cell Board                                        | 2–13 |

| 2-15: Quad cell configuration                                      | 2–14 |

| 2-16: iWarp Single Cell Board                                      | 2–14 |

| 2-17: Single cell configuration                                    | 2–15 |

| 2-18: Single Board Array with Quad Cell Board                      | 2–16 |

| 2-19: iWarp Cardcage Assembly                                      | 2–18 |

| 2-20: 4 by 8 array with one external connection                    | 2–18 |

| 2-21: iWarp System Cabinet                                         | 2–19 |

| 3-1: Relationship between iWarp software and hardware architecture | 3–1  |

| 3-2: iWarp host environment                                        | 3–3  |

| 3-3: iWarp runtime environment software                            | 3–7  |

| 3-4: Master cell and cell communication configuration              | 3–9  |

| 3-5: Using Apply for programming                                   | 3-13 |

# Introducing iWarp

## int<sub>e</sub>l

WARP <sup>™</sup> Carnegie Mellon ₩₩

## iWarp: System Building Blocks for High Performance Systems

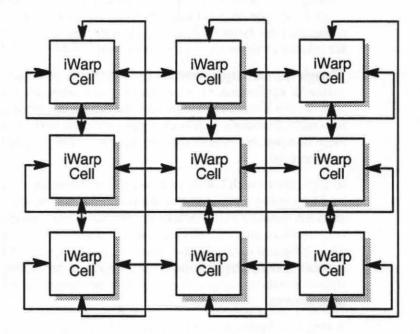

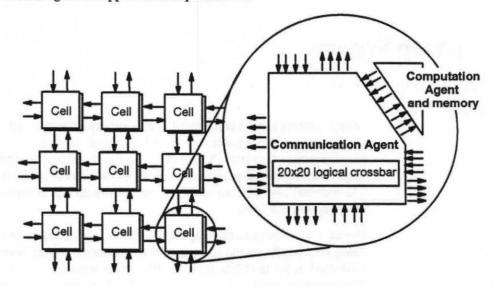

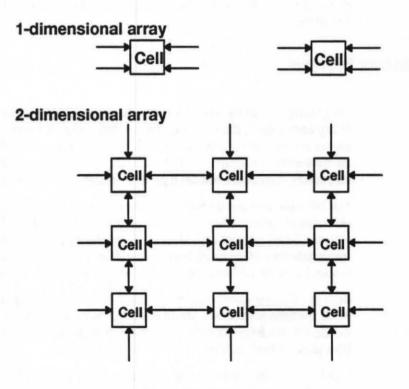

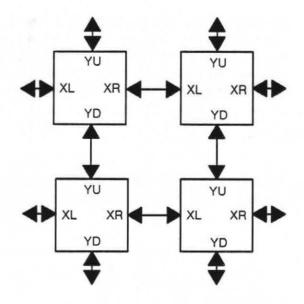

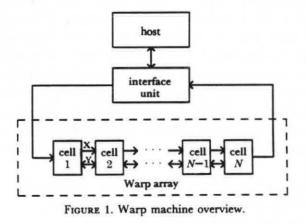

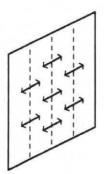

iWarp is a parallel computer system that supports a broad range of high-performance computational algorithms including matrix operations and signal and image processing. The system architecture is modular, using a single VLSI component plus memory as a building block to support a variety of connection topologies. Systems are configured as a two-dimensional array of processors, as in Figure 1-1, with performance that scales from 20 to 20,000 millions of floating-point operations per second (MFLOPS). Each iWarp cell consists of an iWarp component and its local memory. Cells communicate by passing messages over the communication channels that connect them, and the I/O capacity for the system scales with the computation power.

Figure 1-1: An example of a two-dimensional iWarp torus array

#### The Development Partnership

Intel has developed the iWarp system with Carnegie Mellon University under a four-year cost shared development contract sponsored by the Defense Advanced Research Projects Agency (DARPA). The iWarp system is a substantial advancement in high-performance computer technology created through the partnership of industry, academia, and government. Industry provided VLSI development and systems and production technology, academia provided

research basis and conceptual insight, and government provided the vision and support of sponsorship.

The iWarp program is supported under DARPA's Strategic Computing Program for the development of programmable systems that use systolic array technology. The systolic architectural concept is a fine-grain (few calculations per I/O operation) computational technique pioneered by Professor H.T. Kung and his students at Carnegie Mellon University. Systolic architectures achieve high computational efficiency and performance for large arrays of processors and are particularly well suited to the computational needs of signal, image, and matrix processing.

#### The Need

Historically, high-performance signal and image processing applications users have been forced to use special-purpose system designs to obtain the billions of floating-point operations per second (GFLOPS) performance required. Typical applications like adaptive beam-forming for sonar, image analysis and recognition for factory automation systems, and elastic wave equation modeling for seismic analysis all require performance in the 1-10 GFLOPS range.

Though special-purpose systems can effectively meet specific requirements for a particular application, they are generally not adaptable to other needs. Fielded systems can be obsolete by the time they reach operational status. More important, in today's rapidly changing, complex environment, these systems must often be adaptable to both dynamic operational needs and changing requirements.

In applications with lower performance requirements, the use of commercial VLSI microcomputer components has been a real benefit. This benefit is derived from the maturity of the technology, the economies gained by large-scale, cost-sensitive manufacturing, and the extensive software support that comes from a broad base of users. Further, these systems also benefit from the evolutionary enhancements of market-driven microprocessor technology. System enhancements and upgrades can often be accomplished with simple board replacements.

A similar infrastructure is provided by the iWarp VLSI component for high-performance systems. Signal and image processing applications are most dramatically benefited.

iWarp meets these needs with the following capabilities:

Communication level

high communication performance and I/O capability

iWarp communication capability scales with increasing computational power to meet the needs of I/O intensive applications.

#### low overhead,course-grain, message-based, communication

iWarp's cut-through and worm-hole routing mechanisms provide efficient point-to-point data message delivery to any destination in the array without intervention by intermediate processing elements.

#### multiple logical connections on each physical I/O bus

A number of logical connections can be maintained on each physical bus connecting two iWarp cells. This substantially expands the set of intercell communication models that an iWarp array can support.

#### low overhead, fine-grain systolic communication

iWarp is the first commercial processor to support fine-grain systolic communication. By using data directly from the communication pathway, computational algorithms avoid memory bottlenecks, latency is reduced, and large parallel systems perform closer to peak performance expectations.

#### support for multi-functional systems

iWarp's combination of fine-grain systolic and coarse-grain message-based communication allow the array to be divided into independent functional sub-arrays that interact asynchronously for applications with high complexity.

#### **Computation level**

high computational power at low cost

iWarp computational power scales to 20 GFLOPS, and high capacity VLSI production technology brings new economics to high performance computing.

#### high computational density

iWarp supports a computational density of 1 to 3 GFLOPS per cubic foot, opening up general purpose functionality to application-specific systems.

low latency, high performance scalar computations

iWarp floating-point arithmetic elements in each processor optimize scalar performance by executing a complete arithmetic operation in a single instruction. The single-cycle long instruction word architecture allows iWarp to achieve high performance without vectorization.

#### System level

modularity

iWarp's single component requires only memory chips to form a complete processing element that can be combined to form a variety of general-purpose processor arrays of various sizes. System building blocks provide flexibility for rapid prototyping and feasibility demonstration.

#### broad applicability and flexibility

iWarp's balance between low-latency communication and high-speed computational performance gives it applicability over a broad range of computational algorithms. These features also provide the architectural basis for optimized compilers and development tools for array-level programming.

#### high-level programming environment

iWarp provides a high-level programming environment using C and FORTRAN languages, with parallel application development tools to speed development and minimize life cycle support and maintenance costs.

#### immunity to fault and failure

iWarp's on-chip error detection and reporting, logical connections, and source-routed communication allows isolation of faults and supports the development of reconfigurable systems with fault tolerance and graceful degradation properties.

## **Computation and Communication Requirements**

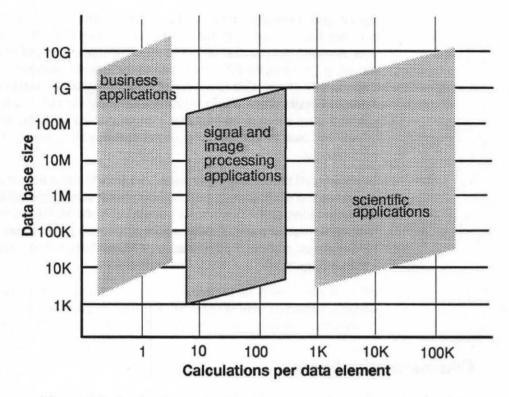

Signal and image processing algorithms are characterized by relatively few computations per data element, as compared with scientific algorithms. This relationship is illustrated in Figure 1-2, where the number of arithmetic calculations per data element is compared to data base sizes for business applications, signal and image processing applications, and scientific applications.

Figure 1-2: Applications with different computation and communication requirements

#### **Comparing Requirements**

The number of calculations per data element is a primary design issue that impacts the architecture of all computer systems. For instance, business applications, like transaction processing, perform relatively little computation but are dominated by I/O operations. Systems must support a large number of I/O channels with many peripheral devices. Thus, the principal design goals are maximizing I/O capacity and providing the ability to handle many independent tasks.

Conversely, scientific applications, particularly those of the supercomputer class, require thousands of calculations per data element. Additionally, the number of calculations per data element increases rapidly with the size of the problem. For example, there is a 30-fold increase in the number of calculations per data element between an order 32 Gaussian Elimination problem containing 1024 data elements and an order 1000 problem (one million data elements). Architectures for scientific computers are, therefore, focused on raw computational performance and memory capacity. The highest level of performance and greatest efficiency are obtained when the entire problem is resident, and the machine can operate for hours or days until the problem is completed.

Signal and image processing systems differ in that a typical algorithm requires only 10 to 100 calculations per data element. The calculations per data element

remain nearly constant with the size of the problem. For example, a 1024-point complex Fast Fourier Transform (FFT) requires only about 20 calculations per data element. An increase in problem size by three orders of magnitude to a one million-point complex FFT only doubles the required number of calculations per data element to 40. This low reuse of data for signal and image processing systems dictates that scalable systems must be capable of matching increases in compute power with corresponding increases in I/O capacity. High performance computing must be supported by a corresponding I/O capacity with the external environment.

Typical signal processing applications require I/O performance that exceeds by several orders of magnitude the requirements of scientific machines having similar performance. This need is coupled with the additional real-time interactive requirements of many signal processing applications. These requirements amplify the importance of I/O architecture to signal and image processing systems.

iWarp systems meet these needs by supporting an I/O performance of 320 MBytes/s between two iWarp cells. For interfacing with the outside world, an iWarp array can have a number of 40 MBytes/s external I/O interfaces.

#### **Communication Needs**

iWarp supports both the coarse-grain message-based communication model of traditional parallel systems and a new fine-grain systolic communication model that is particularly well suited to high performance signal and image processing applications. The systolic model allows the computational element of each processor to use data directly from any of the four communication pathways without sacrificing memory access bandwidth. The term systolic illustrates the concept that data from external sensors can flow, or be pumped, through the array of processors as it is used simultaneously in cell computations.

The coexistence of these two forms of communication is essential for building efficient and flexible high-performance real-time systems. The coarse-grain message-based communication provides the means for interaction between independent heterogeneous tasks and cooperating elements in practical systems. The fine-grain systolic model provides the most efficient use of system resources for tightly coupled compute-intensive tasks.

## **Application Examples**

iWarp's ability to simultaneously handle fine-grain and coarse-grain communication is fundamental for supporting a broad application base and for achieving high utilization from the cells in an iWarp array. The sections that follow illustrate these concepts.

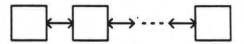

#### A Sonar Example

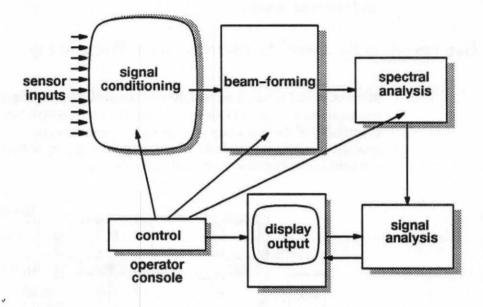

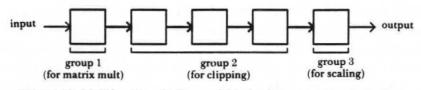

A simple sonar application illustrates the benefits of iWarp fine-grain and coarse-grain communication models. Figure 1-3 shows a functional breakdown of the example.

Figure 1-3: Sonar application

The processing task divides into several functional blocks that are performed in a multi-function pipelined fashion. The sensor inputs are signals that might be derived from an array of hydrophones being towed behind a ship. For the first stage of processing, these signals are filtered and digitized by the signal conditioning section of the system and sent to the beam-forming section.

The beam-forming section can use a variety of computational algorithms for forming steerable acoustic monitoring beams. Sophisticated techniques can account for the changing shape of the array as the ship maneuvers and adapt to the noise environment by nulling out undesired signals while enhancing other regions of interest. These techniques depend heavily on matrix linear algebra using QR decomposition and singular value decomposition as the basic computational algorithms.

The output of the beam-forming section is passed to the spectral analysis section. This section computes a spectrum for each of the beams. The rotating machinery of ships, submarines, and other marine devices produces acoustic energy that has characteristic spectral patterns, which help to detect and identify the source. Typically, the FFT and related signal processing algorithms are the core functions for this task.

The spectral output then passes to the signal analysis section where analysis of the spectral data is performed. Detection of a suspect event can be used to alert an operator or generate control functions that change the operational parameters for the other sections of the processor. For example, detection of energy in a

specific area of interest might trigger a high resolution mode for the spectral analysis section so the structure of the signal can be more accurately evaluated. Additionally, it could direct the beam-former to lay a tight beam on the region of interest for improved noise immunity. Computational requirements vary depending on operational mode and signals being analyzed. The ability to dynamically adapt computational resources to operational needs is a fundamental need of modern systems.

#### Implementing the Sonar Application on an iWarp Array

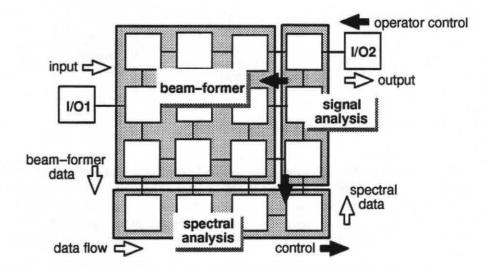

In conventional systems, each of the functional elements of Figure 1-3 is implemented as a separate hardware element. This configuration constrains the adaptability of the system for new operational scenarios, new algorithms, and processing requirements. In an iWarp array, the mapping of the functional elements is configured as illustrated in Figure 1-4.

Figure 1-4: Sonar application on a 16-cell iWarp array

#### Synergy between Communication Models

Processors in each of the functional groups use fine-grain systolic communication to achieve the greatest efficiency and performance for the computational task. Processors, in effect, work together as a single high-performance functional element. Data and control signals that pass between the functional elements use coarse-grain message-based communication. This loosely coupled, asynchronous form of communication allows each functional element of the array to work independently of other functional elements and still interact in a timely fashion required for real-time applications.

#### **Fine-Grain Systolic Communication**

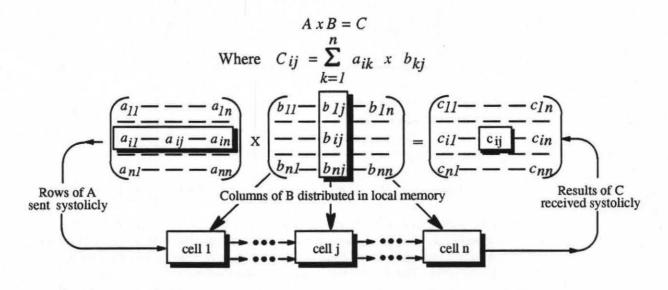

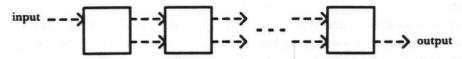

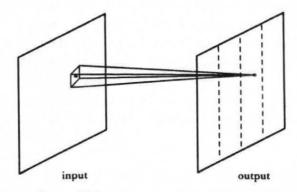

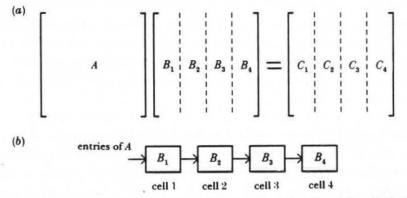

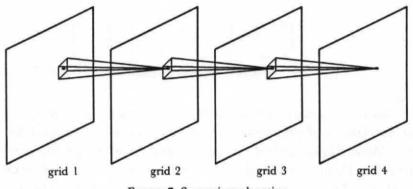

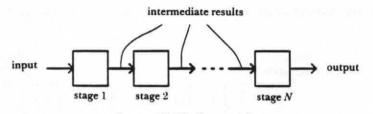

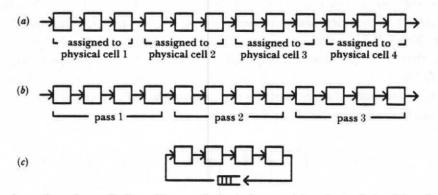

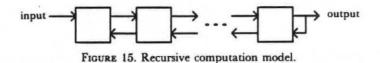

To illustrate the benefits of fine-grain systolic communication, consider the matrix multiply example of Figure 1-5. Two matrices, A and B, are multiplied to form the matrix C. The familiar dot product method is used, which requires that we take the dot product of each row of A against each column of B. The entire calculation requires  $n^3$  multiply-accumulate operations.

Figure 1-5: Matrix multiply example

Consider a linear array of *n* iWarp cells into which the *n* columns of matrix *B* are distributed so that each cell has a column of *B*. Since each row of matrix *A* is applied against each column of *B*, we can pass each row of *A* down the array and perform the corresponding dot product operation as elements flow past the cells. Thus, each cell j performs the computation,  $a_{ik} \times b_{kj} + c_{ij}$ , as each  $a_{ik}$  value flows through the array. The first result,  $c_{11}$ , is complete and can flow out of the array when the dot product between  $a_{1n}$  and  $b_{n1}$  has completed in cell 1. Other results of matrix *C* are completed in turn as the rows of *A* proceed through the iWarp array.

#### **Performance Analysis**

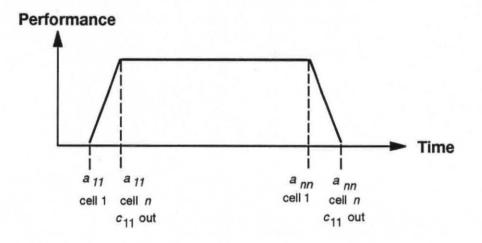

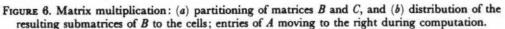

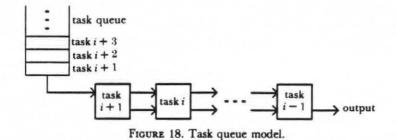

As a general rule, parallel algorithms go through a three stage process of initialization, computation, and cleanup. The initialization process distributes data to processors and gets the computation going. The computation stage occurs when all processors are involved in the process and the peak performance of the system is achieved. The clean-up stage completes the computational process and collects the results at the final destination.

Systolic architectures have a performance advantage over other parallel architectures because the initialization and clean up stages occur as fast as data

can flow through the network of processors. This process can be illustrated by viewing performance of the matrix multiply application as a function of time, as in Figure 1-6.

Figure 1-6: Time line of performance peak in matrix multiply example

The computation starts when  $a_{11}$  reaches cell 1. The initialization phase is complete as soon as  $a_{11}$  completes its path through the array and reaches cell n. At this point, all cells are fully involved in the calculation, and the first result,  $c_{11}$ , is complete. The iWarp array runs at full performance until  $a_{nn}$  reaches cell 1. Then the clean-up phase begins. As  $a_{nn}$  continues down the array, each cell in turn completes its computation, and the performance drops as these cells send out their results and become idle.

#### Advantages of the Systolic Model

The matrix multiply example illustrates another benefit of systolic computing overcoming memory bottlenecks of Von Neumann and Harvard architectures. iWarp addresses these limitations by augmenting memory bandwidth with comparable I/O bandwidth to sustain peak performance of arithmetic elements. The benefits are twofold. First, operands used in common by all cells are broadcast over the I/O path as was done for the rows of matrix A. Second, more effective use is made of memory because intermediate storage accesses are avoided. Using matrix A directly from the communication pathway avoids four memory accesses that would be required by conventional memory-to-memory message-passing techniques.

## **Fundamental iWarp Concepts**

The following concepts are central to the iWarp system design:

- Integrated communication and computation elements for minimizing communication latency, maximizing communication bandwidth, and maximizing computational performance.

- Balanced ratio between communication and computation for supporting fine-grain systolic computation models.

- Independent communication and computation elements for supporting coarse-grain heterogeneous computation models.

- Scalar computational capability to minimize latency, improve the efficiency of compiled code, and broaden the base for supported applications without impacting vector performance.

#### **Integrated Communication and Computation**

The iWarp architecture supports tightly coupled integrated communication and computation elements that provide high-level hardware support for low-latency and high bandwidth sophisticated communications operations. Examples of these operations include word level, intercell, flow control synchronization, automatic spooling and streaming of message data, buffer management, and logical connections that interleave multiple message streams over the finite physical buses.

#### **Balanced Communication to Computation**

iWarp supports the one-to-one communication to computation ratio that is an essential element of fine-grain systolic computing concepts. During a single floating-point multiply-add cycle, two operands can be used from the communication pathways, and two operands can be sent to other cells. This capability broadens the range of algorithms and applications that can benefit from iWarp technology by supporting algorithms that require very few computations per data element. Additionally, the systolic computation model provides near linear speedup for scalable systems, to the limit of the parallelism in the application, by making more effective use of memory bandwidth and I/O capacity.

#### Independent Communication and Computation Elements

Independent communication and computation elements provide support for heterogeneous computation models. This ability allows individual processors or groups of processors to communicate asynchronously and supports transparent

overlapping of computation with communication in hardware. Practical applications require a combination of communication capability: fine-grain for high performance and efficiency, and coarse-grain for interaction between loosely coupled processes and external events.

#### Scalar and Vector Performance

A design goal for iWarp was to reduce latency at all levels of the cell architecture. For the arithmetic elements of the processor, this goal resulted in exceptional scalar performance while maintaining excellent vector performance. The benefit was greater computational efficiency from high-level language compilers and broader applicability of iWarp in a wide range of algorithms and applications. Reduced latency also yields benefits in the handling of exception conditions and external events. In a tightly coupled parallel system, large delays in one processor caused by an exception condition can affect all other processors in the array.

## iWarp Architecture Overview

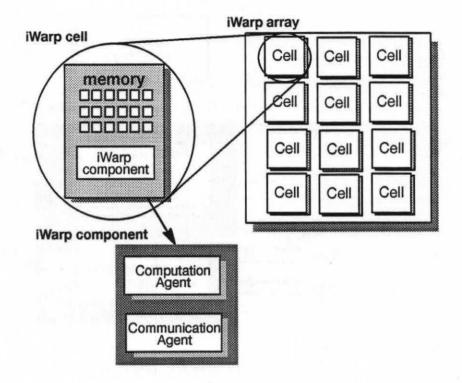

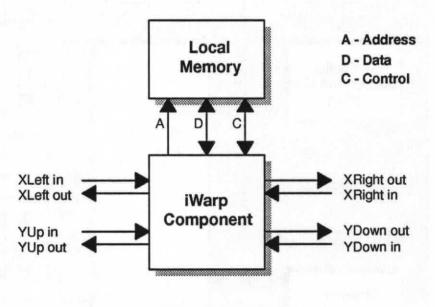

Let us consider how these features are reflected in the iWarp communication architecture. An iWarp system is made up of an array of iWarp cells connected by communication pathways. Each iWarp cell consists of an iWarp component plus memory. As shown in Figure 1-7, the iWarp component contains independent communication and computation agents. Closely coupled yet independently controlled agents make it possible to efficiently overlap communication and computation, and provide greater efficiency for random communication. Nonadjacent cells in the array communicate without disturbing the computation on intermediate cells.

Figure 1-7: iWarp system architecture

The use of source cell routing and logical connection mechanisms provides the capability of reconfiguring the array for fault tolerance and graceful degradation on complex systems. Dead or suspect cell segments can be routed around, and tasks can be redistributed to meet the needs of demanding operational scenarios.

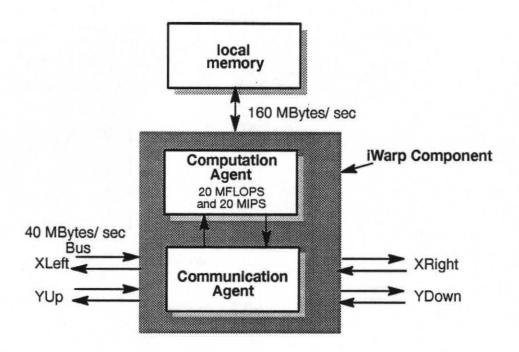

As shown in Figure 1-8, each iWarp cell supports four full duplex I/O channels. Each I/O channel is labelled with a unique name XLeft, YUp, XRight, or YDown. Each channel input or output bus has a sustained performance of 40 MBytes/s. This configuration gives a combined input data bandwidth of 160 MBytes/s plus an output bandwidth of 160 MBytes/s per iWarp cell. The Computation Agent can use half of this bandwidth, 80 MBytes input and 80 MBytes output, while sustaining a similar 160 MBytes/s data I/O capacity with local memory.

Figure 1-8: iWarp cell I/O capacity

Each cell has a peak performance of 20 MFLOPS for 32-bit single precision and . 10 MFLOPS for 64-bit double precision. The iWarp component contains 600,000 transistors on a 540 mil square die and is packaged in a 280-pin, pin grid array (PGA) package. The component and its local memory (typically 18 static RAM components) take up the space of a 3"x5" index card (7.6 cm x 12.7 cm), approximately 15 square inches (96 square cm) of circuit board space.

#### iWarp Communication and Computation Models

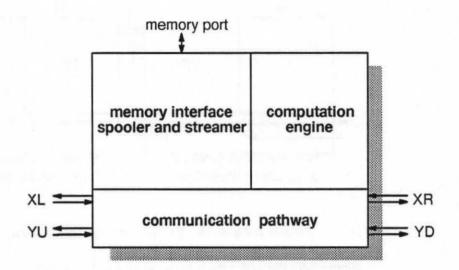

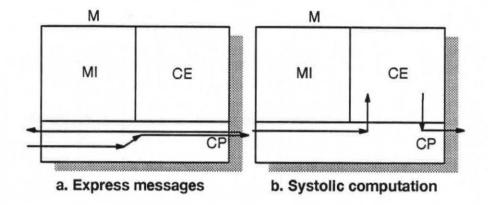

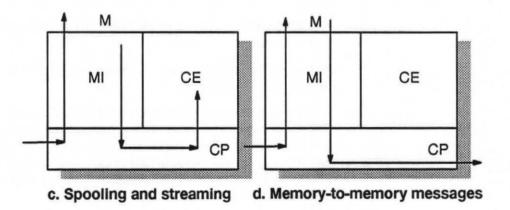

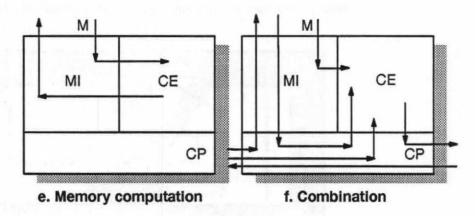

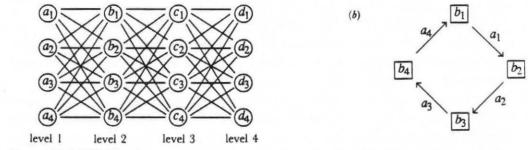

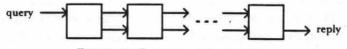

Figure 1-9 shows the primary functional elements of the iWarp component architecture. The computation engine performs the computation and control tasks and is essentially serviced by the other functional elements. The communication pathway provides the interface to other cells in the array and handles message traffic between cells. The memory interface and spooler/streamer elements provide the interface between memory and both the computation engine and communication pathway. The XL channel of a cell's Communication Agent connects to the XR channel of a neighboring cell and vice versa. YU and YD connections are used in the same way.

Figure 1-9: Data pathways

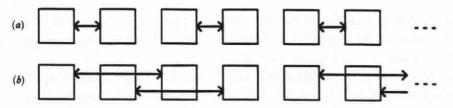

These functional units work together to perform a variety of sophisticated communication/computation functions that are classified as follows:

- Express messages Messages that route directly through a cell.

- Systolic computation Computation uses operands directly off the pathway.

- Spooling DMA between memory and pathway.

- Streaming Buffering systolic data through memory.

- Memory-to-memory message passing Standard message-based communication.

- Memory-based computation Conventional method of computation with operands in memory.

Figure 1-9a illustrates the movement of messages that are not intended for the current cell and pass through unhindered. The cell pathway hardware automatically expresses them through the communication pathway and on to an adjacent cell. Routing information provided at the message level supports corner-turning or transfer of the message from an X connection to a Y connection, in effect, a ninety-degree turn.

Figures 1-9 a and b : Express messages and systolic computation

Figure 1-9b illustrates the movement of data for systolic computation. Data is taken by the computation engine directly off the pathway, used by the computational task, and results sent back on the pathway to another processor in the array.

Figure 1-9c illustrates a variation on systolic computing that supports buffering messages in memory. If the computation engine is busy, and a systolic message is received, the spooler can perform a DMA transfer of the data directly into a preassigned buffer in memory, holding it until the processor is available to respond. The data is then streamed out of memory and presented to the processor by the streamer as if it had been received over the communication pathway. This feature ensures consistency in software, even though the data has been treated differently in hardware.

Figures 1-9 c and d: Spooling and streaming and memory-to-memory messages

Figure 1-9d indicates the movement of data for standard memory-to-memory message passing. In this case, the received message automatically goes into memory to be used by the processor at a later time, and messages sent from memory are spooled out in a like manner. The cell runtime system software supports spooling directly between process data spaces without using intermediate buffering.

Figure 1-9e shows standard memory-based computation. A combination of communication activity is shown in Figure 1-9f. Express operations, memory-to-memory message passing, spooling, memory access, systolic, and so on, are all shown. Note that iWarp component hardware supports all of these communication/computation models simultaneously.

Figures 1-9 e and f: Memory computation and combination

#### Logical Connections

The physical buses that connect iWarp cells are time multiplexed into logical buses that allow several connections to share the same physical pathway. This division improves the use of physical buses, avoids deadlock, and minimizes data starvation problems for unbalanced tasks. As shown in Figure 1-10, logical buses can be viewed as a 20 x 20 crossbar. Logical buses are statically allocated to physical buses under software control. In both Figures 1-10 and 1-11, logical buses have been evenly distributed among the four physical channels and the Computation Agent. Different logical-to-physical mappings can be supported according to the application requirements.

Figure 1-10: Physical and logical buses

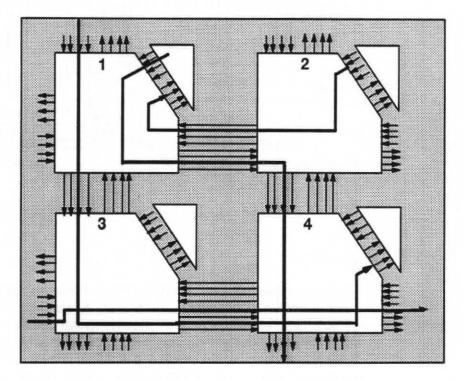

Figure 1-11 illustrates the use of logical connections for an isolated segment of a two-dimensional iWarp array. Note the sharing of the physical bus between cells 3 and 4 using two independent logical connections. Logical connections share the physical communication path in a time multiplexing manner. Priority is given on a round-robin word-level basis, taking into account active logical buses only. Physical bus bandwidth is not consumed by idle logical buses.

Figure 1-11: Logical buses support sharing of physical resources

## iWarp Systems

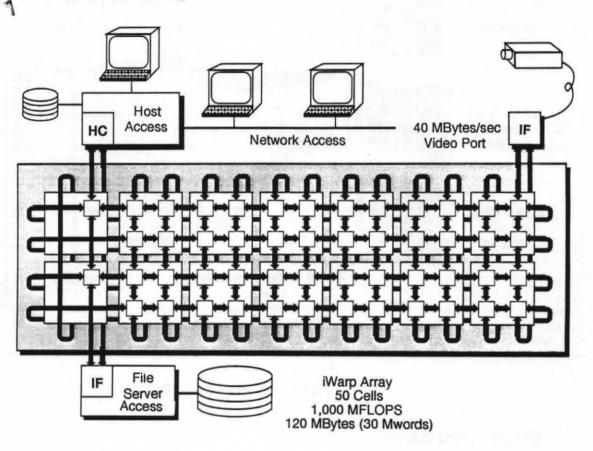

iWarp systems can be configured in a linear array or in a two-dimensional array with a mesh or torus topology. Each iWarp cell consists of an iWarp component plus memory. External I/O interfaces to iWarp cells can be provided by implementing a dual-ported memory block within the memory space of a cell. The external interface accesses one port of the dual-port memory, and the iWarp cell accesses the other.

Figure 1-12 illustrates this approach. In this model, interfaces are connected using iWarp cells on the loop-around connections. iWarp interface cells are contained in the host interface, the file server interface, and the video interface. The system is configured using Quad Cell Boards for the main processing array. Single Cell Boards, with their large memory capacity, are used for staging data

between external interfaces. Network access is provided to multiple users via the host local area network. Both Quad Cell Boards and Single Cell Boards are discussed in Chapter 2.

Figure 1-12: iWarp system configuration concept

#### Configurations

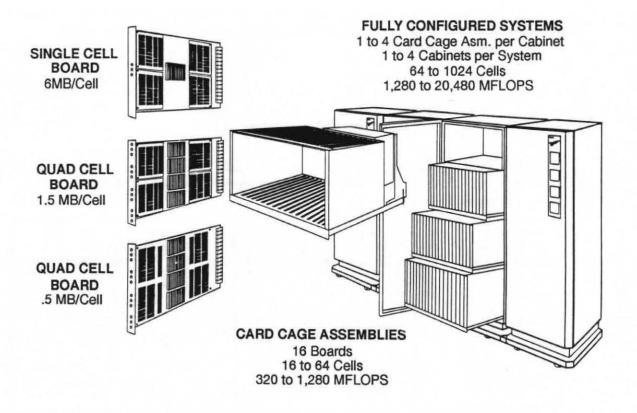

Configurable iWarp systems and system building blocks can be used for applications research, system development, and rapid prototyping. These systems provide a wide range of configuration options, using boards, Cardcage Assemblies, and System Cabinets, as shown in Figure 1-13. Quad Cell Boards support four iWarp cells with .5 to 1.5 MBytes of memory per cell, and Single Cell Boards support 6 MBytes of memory per cell. Boards can be used in custom systems or configured in the standard iWarp Cardcage Assembly.

Cardcage Assemblies are self-contained chassis, including a power supply, fans and a clock distribution board. Using the loop-around cables and interconnects, a wide range of system configurations are supported. System enclosures are 19inch RETMA racks. iWarp configured systems comply with UL, FCC, VDE, CSA, IEC, and GS regulations for safety and emissions.

Figure 1-13: iWarp system building blocks

#### **Single Board Array**

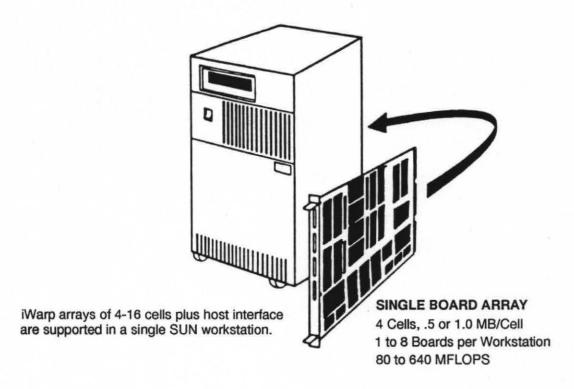

A Single Board Array is provided for Sun workstations. This system provides an effective development environment for use throughout a development group or as an application accelerator for dedicated systems, as shown in Figure 1-14.

iWarp Single Cell and Quad Cell Boards are supported in Single Board Array systems. Each Single Board Array supports one or four iWarp cells configured as a linear or 2x2 array, respectively. Up to eight boards can be configured in a 32-cell array within a workstation.

Figure 1-14: iWarp Single Board Arrays and development systems

## The Significance of iWarp

iWarp represents a major step forward in high-performance computer architectures and will have its greatest impact on the broad base of signal and image processing applications. For these applications, performance beyond the GFLOPS plus range has historically been accomplished only through special-purpose systems. iWarp provides for the first time a programmable system architecture that can be configured to meet both the computational needs and the I/O needs of these signal and image processing applications. iWarp's building block approach to construct very reprogrammable, high-performance, general-purpose systems, as well as special-purpose systems introduces a new era in parallel computing technology.

## 2 iWarp Hardware

9

System Board Component Cardcage

# The iWarp Component

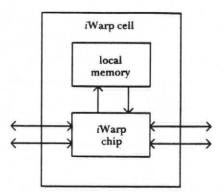

The iWarp component is the basic building block of the iWarp system. Each iWarp component is a complete computer that includes I/O interfaces to connect many devices in a large array of processors. The iWarp component, combined with local memory, forms the iWarp cell, as shown in Figure 2-1.

Figure 2-1: iWarp cell

The initial iWarp component package is a pin-grid array.

# **Component Architecture**

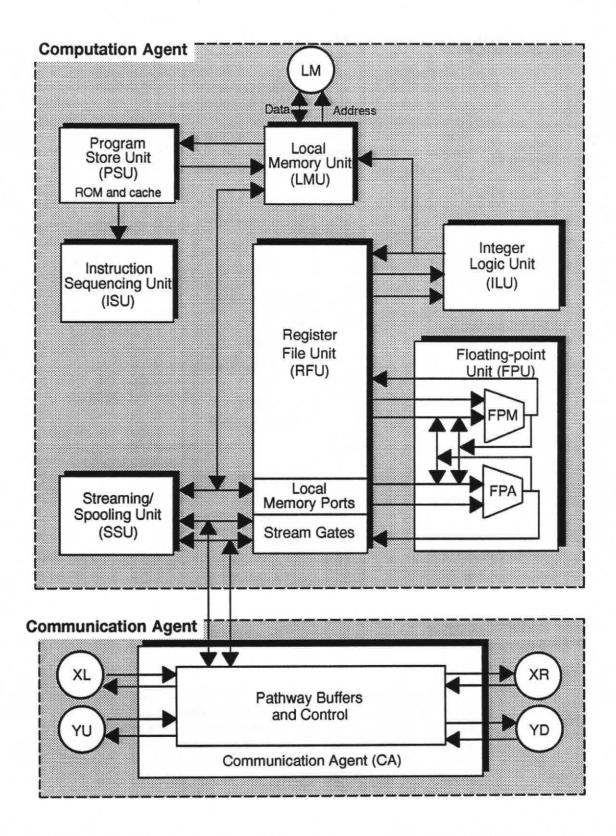

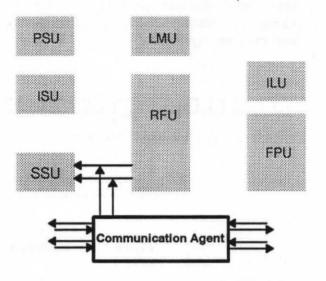

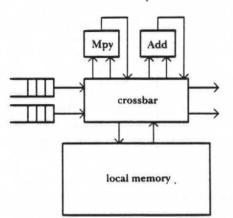

The iWarp component architecture is divided into a Computation Agent and a Communication Agent. The Computation Agent and the Communication Agent function independently, so the processor does not have to participate in the communication process. This allows the communication activities of a cell to proceed without disturbing computation. Figure 2-2 shows a block diagram of the iWarp component architecture.

Figure 2-2: iWarp component architecture block diagram

# **Computation Agent**

The Computation Agent executes an individual cell's portion of an algorithm that has been distributed over an iWarp array of cells. The Computation Agent consists of the following functional units:

- Register File Unit

- Local Memory Unit

- Instruction Sequencing Unit

- Program Store Unit

- Integer Logic Unit

- Floating-point Unit

- Streaming/Spooling Unit

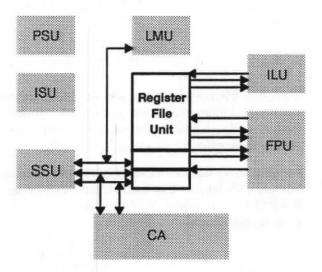

## **Register File Unit**

Figure 2-3: Register File Unit

The 15-port Register File is the central element of the iWarp component architecture, routing data between functional units. The Register File is a general-purpose, multi-ported shared RAM containing 128 32-bit locations. Register File access is by bytes, half-words, words, or double words, depending on the instruction used.

The Register File Unit supports nine read and six write operations in a single 50ns clock cycle. The Register File has nine standard ports, three each to the Integer Logic Unit, the Floating-point Adder, and the Floating-point Multiplier. The Register File also has two local memory ports and four special-purpose ports, or gates, that allow data from memory or the pathway to be placed in

predetermined locations in the Register File. This process of using a programmable gate to access the communication pathways is called streaming and is discussed further in the description of the Streaming/Spooling Unit.

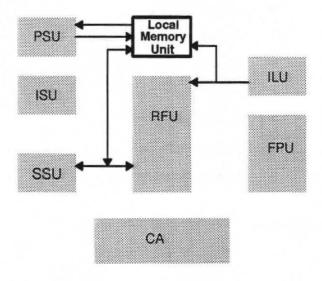

## Local Memory Unit

Figure 2-4: Local Memory Unit

The Local Memory Unit provides the interface between the iWarp component and its local memory. The local memory contains both data and instructions, so the Local Memory Unit provides a direct interface to both the Register File Unit and the instruction cache in the Program Store Unit.

Local memory has two separate buses to maximize performance: a 24-bit address bus and a 64-bit data bus. Local memory can support up to 64 Mbytes in RAM and ROM and provides 20 MHz performance with up to 20 million memory accesses per second.

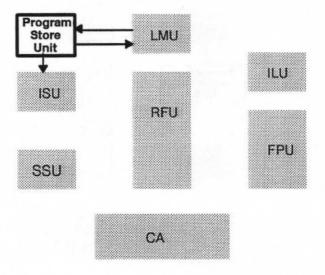

## **Program Store Unit**

Figure 2-5: Program Store Unit

The Program Store Unit fetches instructions from Local Memory, stores them in an instruction cache, and provides them to the Instruction Sequencing Unit. The Program Store Unit contains a 1 Kbyte instruction cache and an 8 Kbyte instruction ROM.

The instruction cache is divided into four sectors, with each sector containing four 64-byte blocks. The mapping of sectors is fully associative, but blocks within a sector contain contiguous addresses. Management of the instruction cache is transparent once it is initialized.

The instruction ROM is divided into eight 1 Kbyte sections. The ROM contains initialization and start-up programs, as well as system routines.

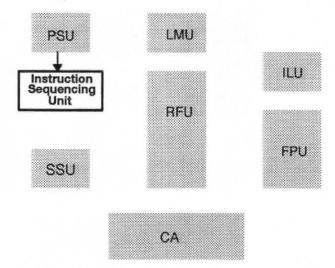

## **Instruction Sequencing Unit**

Figure 2-6: Instruction Sequencing Unit

The Instruction Sequencing Unit controls the flow of program execution by decoding all instructions, producing and distributing control signals to other functional units, evaluating their responses, and scheduling execution. The Instruction Sequencing Unit receives instructions from the Program Store Unit.

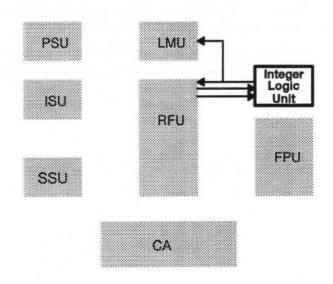

## **Integer Logic Unit**

Figure 2-7: Integer Logic Unit

The Integer Logic Unit is a full 32-bit processor, providing integer arithmetic and logical operations on 8, 16, and 32-bit data, and generating addresses for data access to local memory. The Integer Logic Unit runs at 20 million instructions

per second (MIPS). In a single 50-nanosecond instruction cycle, the Integer Logic Unit accesses two operands, performs a computation, and writes the result back into the Register File Unit. The long instruction word architecture of the iWarp processor allows the Integer Logic Unit to operate in parallel with the Floating-point Unit, generating a peak computing rate of 20 MFLOPS and 20 MIPS for the iWarp cell.

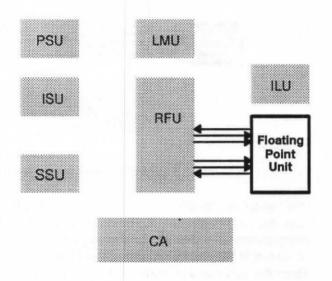

## **Floating-point** Unit

Figure 2-8: Floating-point Unit

The Floating-point Unit contains a non-pipelined Floating-point Adder and Floating-point Multiplier. The Floating-point Adder and Multiplier each provide a peak performance of 10 MFLOPS on 32-bit operations and 5 MFLOPS on 64-bit operations. The Adder and Multiplier run on a two-clock instruction cycle, each producing a result every 100 nanoseconds. In this time, the Adder and Multiplier can each access two operands from the Register File Unit, perform a computation, and write the result back to the Register File Unit. Double precision operations require a four-clock (200 ns) instruction cycle. The Floating-point Unit also contains bypass paths, so the result of a computation can be used as an operand in the next instruction, eliminating the need for an intermediate store and read of the result.

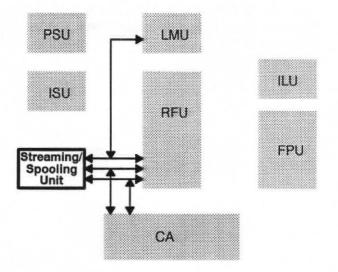

## Streaming/Spooling Unit

Figure 2-9: Streaming/Spooling Unit

The Streaming/Spooling Unit is a sophisticated DMA controller that spools data from the Communication Agent to memory and streams data from memory to the computation units through the stream gates of the Register File Unit. If the processor is busy and it receives a message, the Streaming/Spooling Unit can direct the data into a preassigned buffer in memory, holding it until the processor is available. When the processor becomes available, the data streams out of memory to the processor.

By removing blocked messages from the pathways and allowing unblocked messages behind them to proceed, spooling helps to relieve pathway congestion and improve overall performance.

# **Communication Agent**

Figure 2-10: Communication Agent

The Communication Agent provides communication between cells in an iWarp array by controlling the transfer of data over the physical links between cells. Each cell in an iWarp array connects to its neighbors through four physical links, as shown in Figure 2-11.

Figure 2-11: iWarp cell links

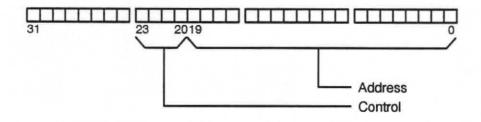

Each of the physical links has two unidirectional buses, one to transmit data and the other to receive data. Data is transmitted between cells in units called messages. Each message contains a header that has address and control information for that message. Bits 0-19 of the header contain the destination address for the message, and bits 20-23 contain control information. Figure 2-12 illustrates a message header.

Figure 2-12: Message header

If an incoming message is addressed for the local cell, the Communication Agent delivers the message to the proper destination. If the message is addressed for another cell, the Communication Agent routes the message through to the next cell.

In a two-dimensional array, it may be necessary for a message to change from an X to a Y, or from a Y to an X direction. If a change in direction is required, the appropriate control bit in the message header is set, and the Communication Agent performs the corner-turning operation that allows a message to change direction.

## **Instruction Formats**

For greater flexibility and efficiency in controlling the functional units of the iWarp component, there are two iWarp instruction formats: a 96-bit compute and access instruction format, and a 32-bit general-purpose instruction format. The 96-bit instruction format includes all frequently used operations, while the 32-bit instruction format constitutes a general-purpose RISC instruction set.

The compute and access instruction has the benefits of a long instruction word architecture, which allows multiple operations in parallel. This instruction can perform floating-point add, floating-point multiply, two memory address computations and memory access operations, plus loop decrement and branch evaluation in two 50 ns clock cycles for single precision data.

Both the floating-point add and floating-point multiply operations support 7-bit fields for their source and destination operands, allowing random access to any location in the Register File Unit. Reserved register locations in the Register File Unit provide high efficiency access to the pathways.

Word three of the 96-bit instruction can specify either a 32-bit general-purpose instruction or two memory operations. The 32-bit instruction option is useful

when a general-purpose operation is needed during a compute and access cycle. Figure 2-13 illustrates the compute and access instruction format.

| - | Nord 1 |           |       |               |               |               |

|---|--------|-----------|-------|---------------|---------------|---------------|

|   | -(2)-  | -(4)-     | -(4)- | -(7)-         | -(7)-         | -(7)-         |

| D | 11     | Data Mode | FADD  | B operand reg | A operand reg | K operand reg |

Word 2

| -(9)-          | -(2)- | -(7)-         | -(7)-         | -(7)-         |

|----------------|-------|---------------|---------------|---------------|

| Memory Control | FMUL  | M operand reg | N operand reg | R operand reg |

Word 3 (Option 1)

| -(16)-                      | -(16)-                            |

|-----------------------------|-----------------------------------|

| Operand for 1st Read Access | Operand for 2nd Read/Write Access |

Word 3 (Option 2)

| -(32)-                      |  |

|-----------------------------|--|

| General-purpose Instruction |  |

#### Figure 2-13: Compute and access instruction format

The general-purpose instruction format supports general control functions such as timer operations, pathway control, and event handling flow control.

The floating-point adder supports operations in hardware, including add, subtract, compare, maximum, minimum, and binary log. Similarly, the floating-point multiplier supports multiply, divide, square root, and remainder in hardware. The general-purpose instruction format also supports data conversion operations and a full range of logical operations. This format also supports byte, half-word (16-bit), full-word, and double-word memory operations, as well as automatic read-modify-write in hardware for byte and half-word operations. Table 2-1 summarizes the general-purpose instruction format functions.

| FUNCTION                   | OPERATIONS                                             |                                                              |

|----------------------------|--------------------------------------------------------|--------------------------------------------------------------|

| General Control            | timer operation<br>pointer control<br>pathway control  | event control<br>spool request<br>execute instruction        |

| Flow Control               | call<br>push<br>pop<br>branch                          | return<br>break<br>enter loop<br>stack control               |

| Extended Flow Control      | absolute call/branch<br>indirect call/branch           |                                                              |

| Floating-point Operations  | add<br>subtract<br>compare<br>maximum<br>minimum       | binary log<br>multiply<br>divide<br>square root<br>remainder |

| Data Conversion Operations | integer to floating-point<br>floating-point to integer |                                                              |

| Integer/Logical Operations | logical<br>arithmetic<br>bit                           | rotate<br>find MSB                                           |

| Memory Access Operations   | byte<br>half-word                                      | full-word<br>double-word                                     |

## Table 2-1: general-purpose Instruction Summary

# The iWarp Boards

There are two types of iWarp cell boards, the Quad Cell Board and the Single Cell Board. As their names imply, the Quad Cell Board contains four iWarp cells, and the Single Cell Board contains one iWarp cell. Each cell on an iWarp board consists of an iWarp component and its associated local memory. Both the Quad and Single Cell Boards are approximately 9 by 11 inches, and they operate at a minimum clock rate of 40 MHz, or 20 MFLOPS per cell.

Each cell on the Quad and Single Cell Boards controls three LEDs mounted on its front panel. Two of the LEDs indicate cell status, and the third indicates an error condition. The boards also contain clock circuitry that synchronizes cells to within 5ns of each other in a Cardcage Assembly and within 25ns across multiple Cardcage Assemblies. In addition to the Quad and Single Cell Boards, iWarp offers a Single Board Array that plugs directly into a Sun 3 or Sun 4 system. The Single Board Array is a Quad or Single Cell Board combined with a Sun interface board to form a complete iWarp array. The Single Board Array is approximately 14 by 14 inches for direct fit into the Sun workstation.

## Quad Cell Board

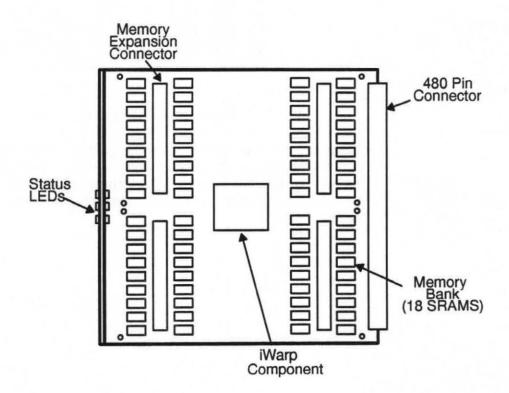

The Quad Cell Board contains four iWarp components and four banks of local memory. Figure 2-14 shows the physical layout of the Quad Cell Board.

Figure 2-14: iWarp Quad Cell Board

The systolic pathways that extend off the Quad Cell Board are connected directly from the appropriate cell to a board edge connector. Each pathway coming off the board is capable of sustaining transfer rates of 80 Mbytes/s (40 MBytes/s in each direction). Figure 2-15 shows the pathway configuration for the Quad Cell Board.

Figure 2-15: Quad cell configuration

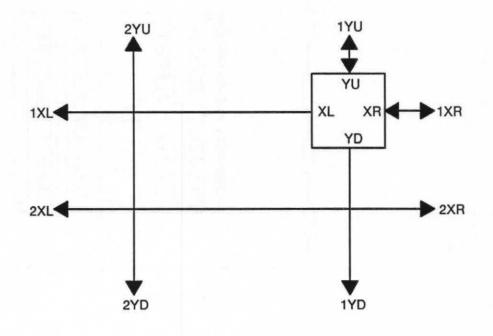

# **Single Cell Board**

The Single Cell Board contains a single iWarp component and four banks of local memory. Figure 2-16 shows the physical layout of the Single Cell Board.

Figure 2-16: iWarp Single Cell Board

As with the Quad Cell Board, the pathways that extend off the Single Cell Board are connected directly from the appropriate cell to a board edge connector. Each pathway coming off the board can sustain transfer rates of 80 MBytes/s (40 MBytes/s in each direction). Figure 2-17 shows the pathway configuration for the Single Cell Board.

Figure 2-17: Single cell configuration

The pathways that are not connected to another cell are bypass connections that directly connect 2XL to 2XR and 2YU to 2YD on the board.

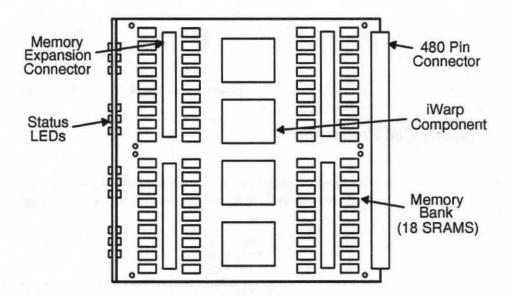

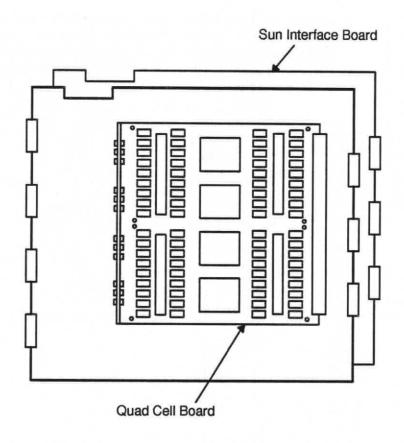

# Single Board Array

The Single Board Array is a Single or Quad Cell Board combined with a Sun interface board to form a complete iWarp array. The Single Board Array plugs directly into a Sun 3 or Sun 4 system, providing a dedicated program development environment or a network performance accelerator. Up to eight Single Board Arrays can be connected in a single workstation to form a 32-cell, 2 by 16 array. Figure 2-18 shows the physical layout of a Single Board Array with a Quad Cell Board.

Figure 2-18: Single Board Array with Quad Cell Board

# Local Memory

Each iWarp board contains four banks of local memory. On the Single Cell Board, the single component has access to all four banks. On the Quad Cell Board, each cell has access to one bank. Each bank of local memory consists of 18 SRAMs.

Local memory can be expanded with the Memory Expansion Module. Memory Expansion Modules connect to a Single or Quad Cell Board through a connector residing on the board. Each Memory Expansion Module contains up to two banks of additional local memory, and up to four Memory Expansion Modules can be connected per board, allowing three times the local memory. In addition, each bank of local memory can be configured using one of two SRAM densities, allowing even greater local memory flexibility. Table 2-2 lists the available memory for each iWarp cell. The maximum amounts represent full use of Memory Expansion Modules.

## Table 2-2: iWarp Cell Memory

| A               | vailable Mem    | nory per iWar | p Cell (byte      | es)     |

|-----------------|-----------------|---------------|-------------------|---------|

|                 | Quad Cell Board |               | Single Cell Board |         |

| SRAM<br>density | minimum         | maximum       | minimum           | maximum |

| 256K            | 512K            | 1.5M          | 2M                | 6M      |

| 1M              | 2M              | 6M            | 8M                | 24M     |

The 1M SRAM density is not available until 1991.

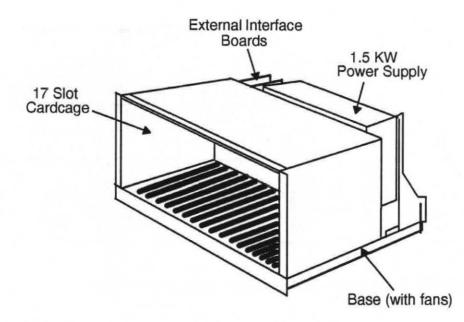

# The iWarp Cardcage Assembly

The iWarp Cardcage Assembly is a standard 19-inch rack-mountable open-frame chassis that combines the following into a single assembly:

- 17-slot cardcage

- backplane

- external device interface

- power supply

- fans

Sixteen of the slots in the Cardcage assembly are available for Single or Quad Cell Boards. A single Cardcage Assembly can hold up to 64 iWarp cells using Quad Cell Boards or up to 16 iWarp cells using Single Cell Boards. Single and Quad Cell Boards can also be mixed within a Cardcage Assembly to allow even greater flexibility.

The remaining slot in the Cardcage Assembly is reserved for the Clock/Sync Board. This board provides the necessary circuitry for synchronizing all cells within an iWarp array, even if the array extends to multiple Cardcage Assemblies. Figure 2-19 shows the iWarp Cardcage Assembly.

Figure 2-19: iWarp Cardcage Assembly

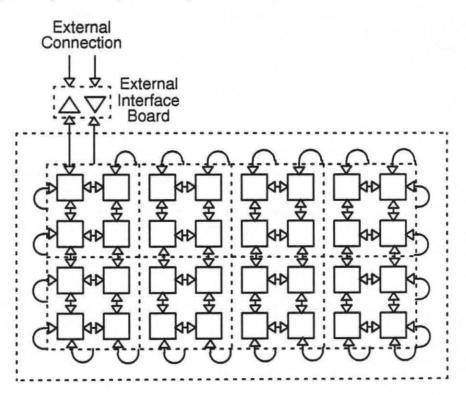

Cardcage Assemblies can be connected to form larger iWarp arrays by using iWarp External Interface Boards. These boards plug directly into the appropriate cell pathways on the backplane. External Interface Boards also allow connection of other external devices to an iWarp array. Figure 2-20 shows an example of a 4 by 8 iWarp torus array with a single external connection.

Figure 2-20: 4 by 8 array with one external connection

The external connection to the iWarp array can be made at any of the loops in either the X or the Y direction.

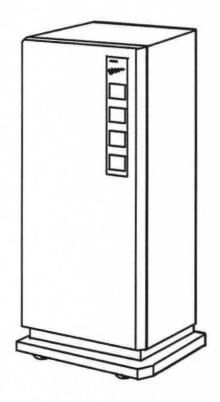

# The iWarp System

Flexibility is the key characteristic of the iWarp system. From one to four iWarp Cardcage Assemblies reside in a single System Cabinet, and up to four cabinets can be connected to form even larger arrays. With a system of four cabinets, an iWarp system can be extended to a 32 by 32 array of 1024 iWarp cells. Figure 2-21 shows the iWarp System Cabinet, which contains up to four Cardcage Assemblies.

Figure 2-21: iWarp System Cabinet

The front door of the System Cabinet contains an LED display that shows status conditions for each iWarp cell housed in the cabinet. The LED display consists of four 8 by 8 LED arrays, with each array corresponding to one of the cardcages in the cabinet. Each pair of LEDs in the array corresponds to the status of a specific cell. There is also an error LED and a power LED for each array.

# Diagnostics

The iWarp diagnostics consist of self-tests for the interface board and a set of tests to ensure the integrity of the entire system. The interface tests are run at power-up or when a system reset is done. These tests ensure that the interface board is functioning correctly. The system test checks the data paths from the host to the interface and from the interface to the processor array. These tests can be run interactively or in batch mode.

# 3 iWarp Software

# iWarp Software Architecture

iWarp software architecture supports high-performance computation in signal and image processing and scientific applications. iWarp's software environment is composed of a program development environment that resides on the host workstation and execution support that resides on the iWarp array. This software, which is closely tied to iWarp's hardware architecture, provides the following:

- a host development environment supported on Sun workstations

- a runtime environment supported on each iWarp cell and the host

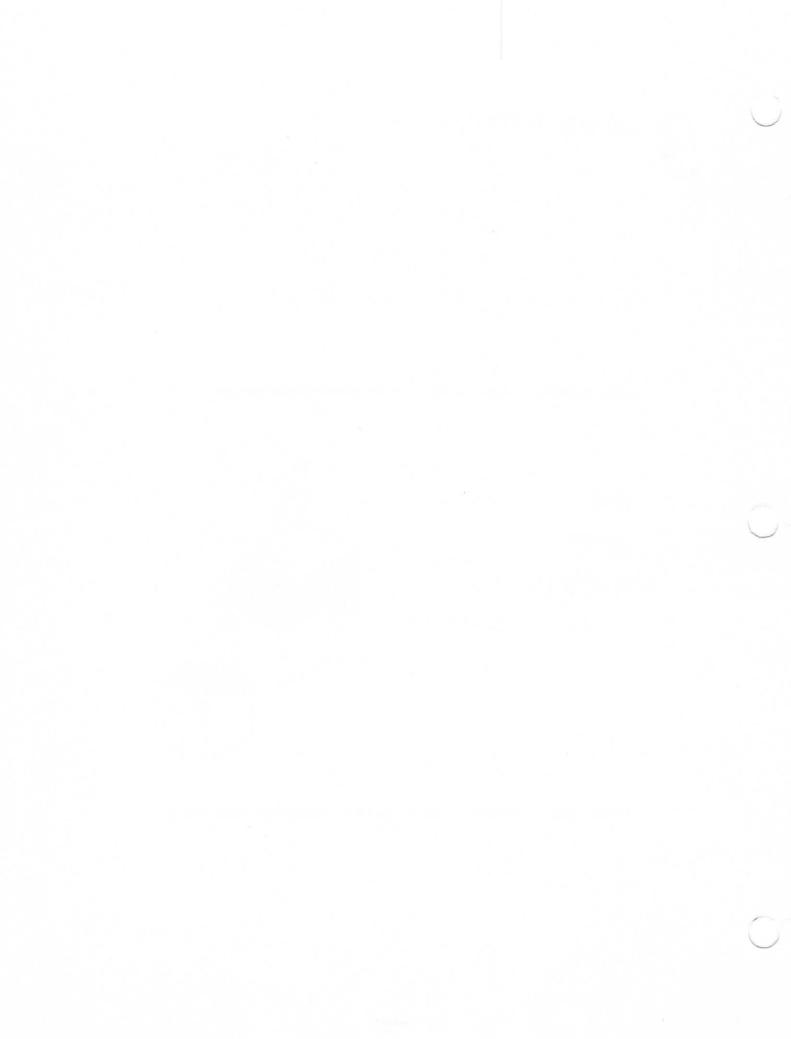

Parallel user code is executed on the array of iWarp cells. Sequential code can either run on the host or on a single iWarp cell. The software for the file server can also run on the I/O subsystem (see figure 1-12) or on the host. Figure 3-1 illustrates the relationship between iWarp's software and hardware architecture.

The following lists summarize the software for the iWarp cell and iWarp array. The software listed is described in the following sections of this chapter.

## iWarp cell software

compilers:

- C

- FORTRAN

- symbolic debugger

utilities:

- linker/combiner

- loader

- librarian

communication software:

- blocking and non-blocking message passing using a mailbox paradigm

- inter-cell communication mechanisms can be used to communicate between processes on a single cell

- remote UNIX I/O

libraries:

- math libraries

- subset of UNIX Sys V Library calls

system functions:

- memory allocation

- user timers

- multi-threaded programs based on Mach C-threads

- priority-based preemptive scheduling

- process (thread) control

## iWarp array software

compilers:

Apply

communication software:

- blocking and non-blocking message passing using a mailbox paradigm

- word-by-word user-programmed systolic communication

- user-programmed spooling

- request-response and RPC protocols

libraries:

WEB

system functions:

- support for UNIX file I/O to be executed on the attached host

- low-level functional access to iWarp communication engine

- remote thread creation and invocation

## iWarp host software

- combiner

- array allocation

- array job management

# iWarp Host Environment

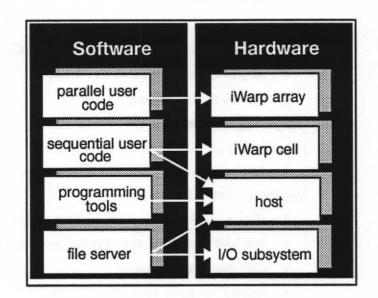

The host environment (the Sun system) includes program development software and software that supports communication between the host and the iWarp array. The host software grants access to the iWarp array and maintains the connection between a user's system and the iWarp system after access is granted. The program development environment for iWarp is supported on Sun workstations using SunOS. This environment provides UNIX-based program development tools such as:

- cross compilers/assembler/linker

- loader

- debugger

- diagnostics

Figure 3-2 illustrates the structure of iWarp's host environment software.

Figure 3-2: iWarp host environment

# iWarp Program Development Tools

iWarp provides tools to develop, manage, link, load, and debug programs in a familiar UNIX environment.

## The single-cell compilers

The iWarp C and FORTRAN compilers are highly optimizing compilers that run on the Sun workstation and generate iWarp object code for individual iWarp cells. The compilers, assembler, linker, and loader have standard UNIX interfaces. The compilers pack multiple operations into each wide instruction word, allowing the iWarp hardware functional units to execute those operations simultaneously. The iWarp C compiler is an industry standard Kernighan and Ritchie C language compiler with iWarp-specific extensions that provide access to the systolic pathway. The iWarp FORTRAN compiler accepts standard FORTRAN77 source with VMS extensions and iWarp-specific extensions.

The iWarp extensions for C and FORTRAN support:

- systolic communication support (send and receive primitives)

- iWarp condition code checking support

- sophisticated assembly code inlining capability

- pragma support for inlining specification

## Getting better performance

To make a program run faster and take less space, the iWarp compilers employ a variety of optimizations to fully use the multiple functional units of iWarp cells. Two of these optimizations important to iWarp users are software pipelining and local code compaction. These code scheduling techniques allow the compilers to generate code with multiple operations in the same machine instruction. The following two examples discuss how pipelining and code compaction, two of the many optimization features of the iWarp compilers, support the iWarp program developer.

With software pipelining, an iteration of a loop in the source program can be initiated before preceding iterations are completed. This technique exploits the repetitive nature of loops to generate efficient code for processors with multiple functional units. At any time, multiple iterations are simultaneously in different stages of the computation. The steady state of this pipeline constitutes the loop body of the object code.

Software pipelining uses multiple functional units to perform the calculations of several iterations of a loop at the same time. The following example shows source code and pseudo assembler output that illustrate software pipelining of a simple loop.

DO I = 1, 10 A(I) = A(I) \* CENDDO

Register  $r_1$  contains the iteration count minus 2 (10 - 2 = 8), and register  $r_2$  contains the constant C. Registers  $r_3$  and  $r_4$  contain intermediate results.

{ load  $a_1, r_3$ { fmul  $r_2, r_3, r_4$ ; load  $a_2, r_3$  }

| loop |      | r <sub>1</sub>                            |                                                         |                                     |   |

|------|------|-------------------------------------------|---------------------------------------------------------|-------------------------------------|---|

|      | el { | store r <sub>4</sub> , a <sub>1-2</sub> ; | fmul r <sub>2</sub> , r <sub>3</sub> , r <sub>4</sub> ; | load a <sub>i</sub> ,r <sub>3</sub> | } |

|      | {    |                                           | store r <sub>4</sub> , a <sub>n-1</sub>                 | fmul r2,r3,r4                       | } |

|      | {    |                                           |                                                         | store $r_4, a_n$                    | } |

In this example, three iterations of the loop are computed simultaneously. The "steady state" of the loop is shown on the line beginning with "el" (for, "end loop"). On the *i*-th iteration, the load of A(I) takes place in parallel with the multiplication of A(I-1) and C, and the store into A(I-2).

Code compaction can be performed anywhere there are enough source level operations to make the optimization worthwhile. The following example shows a sequence of operations typical of complex arithmetic.

REAL = (TEMP1 \* WREAL) - (TEMP2 \* WIMAG) IMAG = (TEMP1 \* WIMAG) - (TEMP2 \* WREAL)

This example shows six operations, but with compaction, two of the operations can be overlapped, resulting in four instructions actually being used. Loading and storing of values can also be overlapped, giving a greater savings than this example implies.

Some additional optimizations include:

- redundant-instruction elimination

- flow-of-control optimizations

- algebraic simplification

- peephole optimizations

- function-preserving transformations

- common subexpression elimination

- copy propagation

- dead-code elimination

- induction variables and reduction in strength

- constant folding

- branch elimination

- variable renaming

- inline renaming

- loop unrolling

## The linker and loader

The iWarp linker acts much like the UNIX linker. It combines multiple, separately compiled modules into one object file ready to be loaded onto the cell. The iWarp linker also supports user-created libraries. The loader places certain linked files into specified cells. In addition, the iWarp loader handles segments of files and acts as an array-level combiner to resolve intercell resource issues.

#### The debugger

The iWarp debugger helps the programmer monitor the behavior of iWarp cell programs and gather information about the programs being run. It is an interactive symbolic debugger that supports application debugging for C, FORTRAN, and iWarp assembly language programs. Debugger breakpoints allow the programmer to suspend and examine cell or array programs and then continue or terminate execution. The debugger displays both high-level and assembly language program text and can be used from a window-based interface.

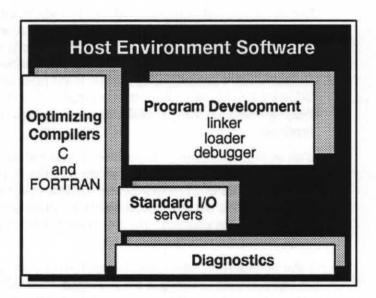

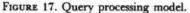

# iWarp Runtime Environment

The runtime system manages the resources of the hardware on which it runs and provides the application programmer with a set of routines that can be called to use these resources. The iWarp runtime environment provides libraries and communication protocols supported on each cell, the host, and the file server. These libraries include runtime libraries such as mathematical and utility functions, I/O libraries, and pathway libraries. The runtime environment works with the hardware to provide several internode communication paradigms for program development. The runtime environment includes:

- C and FORTRAN runtime libraries

- remote I/O runtime libraries

- basic runtime system support

- message passing protocol support

- systolic protocol support

Figure 3-3 illustrates the iWarp runtime environment software.

Figure 3-3: iWarp runtime environment software

## iWarp Runtime Libraries

The runtime libraries include the standard C, FORTRAN, and I/O libraries, as well as special pathway runtime libraries. The pathway runtime libraries provide the programmer with a set of routines for low-level access to the pathway hardware. These routines also provide a high-level interface for opening and debugging ports and connections as well as creating and accepting messages.

## iWarp System Support

iWarp's runtime system software provides a complete, yet low overhead management of the iWarp component's resources. This software has the basic services associated with general-purpose runtime systems plus some special-purpose services to handle the distributed nature of an iWarp array.

iWarp provides a number of communication protocols that can be used to transfer data between cells or between a cell and host. These include high-level communication protocols, such as remote procedure calls and guaranteed arrival streams for the application programmer. Lower-level communication protocols, such as a data link layer, are for the user who intends to build higher-level protocols. In addition, multitasking provides support for asynchronous communication protocols that allow server processes to run in the background and provide service to communication requests as resources become available.

iWarp communication facilities support both memory-to-memory message passing communication and program-to-program word-by-word systolic communication.

- Message-based communication is based on variable length, untyped messages that are sent or received from buffers in cell memory. The user calls send and receive primitives to transfer data, specifying the protocol that should be used to transmit the data. Sends and receives may be blocking or non-blocking, and a task can resynchronize with a non-blocking call to find out when the operation is completed.

- Systolic communication allows the user to perform arbitrary computations on operands taken directly from the pathway without the overhead associated with memory-to-memory communication. Since the iWarp hardware and software are optimized for systolic data transfer, this method provides optimal performance for certain applications.

iWarp facilitates both efficient message passing and flexible systolic communication by providing the required hardware support, discussed in Chapter Two. The hardware supports word-level flow control, logical buses, and streaming and spooling. Message passing communication is a commonly used model for coarse-grain parallel computation. Conversely, systolic communication is typically used for fine-grain parallel computation.

# Programming an iWarp System

So far in this chapter, we have discussed the overall software environment, how it relates to the hardware environment, and the software tools for programming the iWarp system.

The following program gives an example of what the user can do by programming the array in C. This approach requires that the programmer be familiar with the functioning of the cell array, but it offers great programming flexibility. As an alternative, the program developer can use the Apply language, which is specialized for image processing applications. Such programs are fairly easy to write in Apply.

The following simple example shows segments of an iWarp C program that evaluates a polynomial. It demonstrates the solution of an *n*-th order polynomial at *m* data points using an n+1 cell ring array of iWarp cell processors. Each iWarp cell processor is connected to its right neighbor with two paths. Each of *n* cells computes one step of the Horner algorithm and passes the result to the right. The n+1th cell serves as a master cell. The master cell provides data and receives, stores, and prints the results. In this example, we are computing the following 5th order polynomial using 6 cells:

## $P(z)=c_0z^4+c_1z^3+c_2z^2+c_3z+c_4$

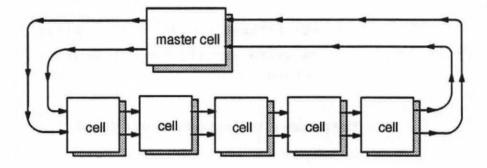

Figure 3-4 illustrates how data flows from the master cell around the array of cells.

## Figure 3-4: Master cell and cell communication configuration

There are two parts to the program: one part that runs on the master cell and one part that runs on each cell. The #include statements and the master cell program segment that reads in the data from the host and writes back the results have been omitted for brevity.

```

static float c[5]; /*coefficients*/

static float z[5]; /*data points*/

static float p[5];/*results*/

static int nc; /*number of coefficients*/

static int nz; /*number of data points*/

main()

£

register int i, tmp, error = 0;

register float ftmp, fzero = 0.0;

/*host input*/

if( pathway_init() ) return(1);

sendi( GATE0, nc );

tmp = receivei( GATE0 );

sendi( GATE0, nz );

tmp = receivei( GATE0 );

/* send coefficients */

for (i = 0; i < nc; i++)

_sendf( GATE0, c[i] );

/* send z and receive p */

for ( i = 0; i < nz; i++ ) {

sendf( GATE0, z[i] );

```

```

_sendf( GATE1, fzero );

ftmp = _receivef( GATE0 );

p[i] = _receivef( GATE1 );

}

if( pathway_close() ) return(1);

/* write results back to host */

return 0;

```

}

This portion of the program runs on each cell.

```

main()

£

register int i, nc, nz;

register float temp, coeff, xin, yin, ans;

register float fzero = 0.0;

if( pathway_init() ) return(1);

nc = receivei( GATE0 );

sendi( GATE0, nc-1 );

nz = _receivei( GATE0 );

sendi( GATE0, nz );

/* capture the first coefficient

* and pass the rest on.

*/

coeff = receivef( GATE0 );

for ( i = 1; i < nc; i++ ) {

temp = receivef( GATE0 );

sendf( GATE0, temp );

}

/* Horner's rule

*/

for ( i = 0; i < nz; i++ ) {

xin = _receivef( GATE0 );

yin = _receivef( GATE1 );

sendf( GATE0, xin );

ans = coeff + yin * xin;

_sendf( GATE1, ans );

}

if( pathway_close() ) return(1);

return 0;

}

```

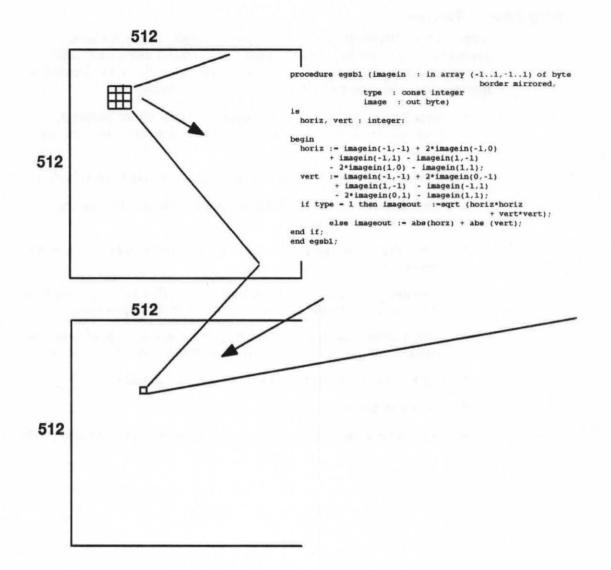

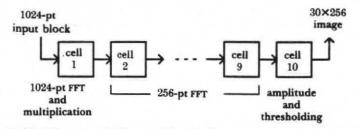

## **Apply: for Image Processing Applications**

Apply is a special-purpose, high-level language for image processing applications that frees the programmer from having to program low-level inter-processor communication.

The Apply language:

- provides per-pixel generation of the output image

- allows a local operation to be written easily; more easily than with serial languages like C

- has special functions for borders, image expansion, and reduction

This language is designed for writing two-dimensional local operator algorithms. Apply generates parallel code that runs on an array of iWarp cells of any size. Apply and its implementation on iWarp is designed for implementing low-level vision algorithms such as:

- edge detection

- smoothing

- contrast enhancement

- thresholding

- point operators

- image addition, subtraction, multiplication, and division

- image reduction and expansion

- color conversion

The Apply language simplifies programming two-dimensional image processing operations. Data objects are scalars and two-dimensional arrays of scalars having various types. These types include byte, integer, real, and double. Apply uses conventional expression syntax to specify computations on these data objects.

Apply procedures are called from FORTRAN or C language main programs in much the same way as other procedures are called. On the calling side, arguments to the Apply procedures are declared according to syntax and semantics of the FORTRAN or C languages. Inside the Apply procedure, arguments are declared in a slightly different way, as required by the syntax and semantics of the Apply language.

Image data from the calling program is transferred from the calling program to the array of computational cells on which the Apply routine is executed. Results are returned to the calling program before control passes back to the calling program. This data transfer is normally invisible to the Apply programmer.