# Specifications for the Four-Instruction Computer (FIC)

Eirik Bakke

## State Transition Table

| state  | I   | carry | Mem/A | Mem/R | MemWR | Α | PC   | R       | carry     | state  |            |

|--------|-----|-------|-------|-------|-------|---|------|---------|-----------|--------|------------|

|        |     |       |       |       |       | Α | PC   | R       | carry     | -      | (defaults) |

|        |     |       |       |       |       |   |      |         |           |        |            |

| fd     | add | Х     | PC    | Mem   | 0     | D | PC+1 | -       | -         | mr_add |            |

| fd     | nor | Х     | PC    | Mem   | 0     | D | PC+1 | -       | -         | mr_nor |            |

| fd     | sav | Х     | PC    | Mem   | 0     | D | PC+1 | -       | -         | mw0    |            |

| fd     | jcz | 0     | PC    | Mem   | 0     | х | D    | -       | -         | fd     |            |

| fd     | jcz | 1     | PC    | Mem   | 0     | х | PC+1 | -       | 0         | fd     |            |

| mw0    | х   | х     | Α     | R     | 0     | _ | -    | -       | -         | mw1    |            |

| mw1    | X   | Х     | Α     | R     | 1     | - | -    | -       | -         | mw2    |            |

| mw2    | X   | х     | Α     | R     | 0     | х | -    | -       | -         | fd     |            |

| mr_add | х   | x     | Α     | Mem   | 0     | х | -    | R+D     | R+D carry | fd     |            |

| mr_nor | Х   | Х     | Α     | Mem   | 0     | х | -    | R nor D | 0         | fd     |            |

### Instructions

| MS Bits | Instruction | Description                                                                              |

|---------|-------------|------------------------------------------------------------------------------------------|

| 00      | add         | add value at address encoded in instruction to R, resetting/setting carry as appropriate |

| 01      | nor         | nor value at address encoded in instruction with R, resetting carry                      |

| 10      | jcz         | jump to address encoded in instruction if carry is not set, resetting carry otherwise    |

| 11      | sav         | save value in R at address encoded in instruction                                        |

#### I/O

Initialization: external loader may take over clock and data bus

Regular I/O: when going from state fd, if PC was 0, R takes value of input register and output register takes value in R

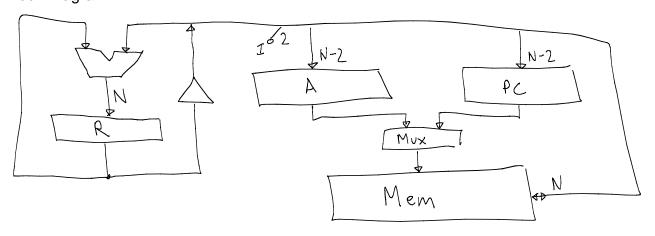

## **Block Diagram**