# LEAP Shared Memories: Automating the Construction of FPGA Coherent Memories

<u>Hsin-Jung Yang</u><sup>†</sup>, Kermin E. Fleming<sup>‡</sup>, Michael Adler<sup>‡</sup>, and Joel Emer<sup>†‡</sup>

<sup>+</sup> Massachusetts Institute of Technology

<sup>‡</sup> Intel Corporation

May 12th, FCCM 2014

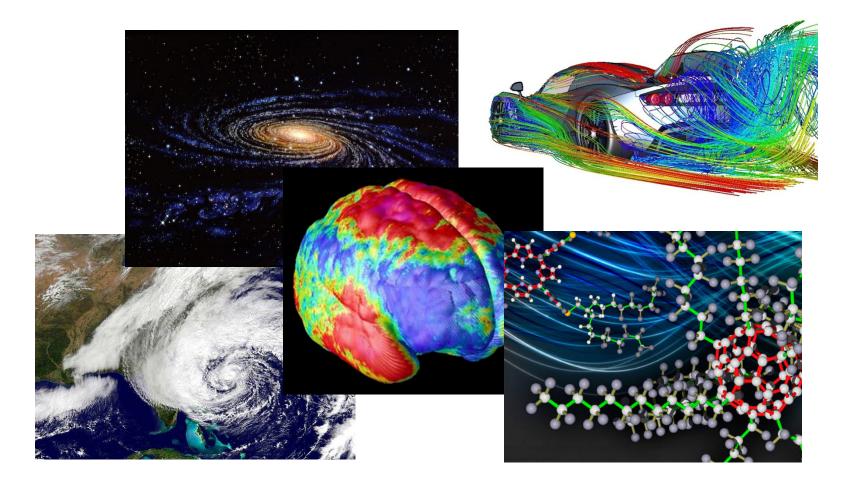

• Goal: simplifying parallel programming on FPGAs

- Goal: simplifying parallel programming on FPGAs

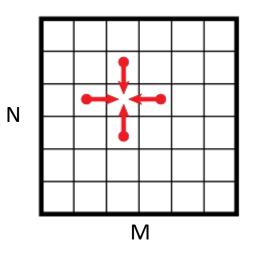

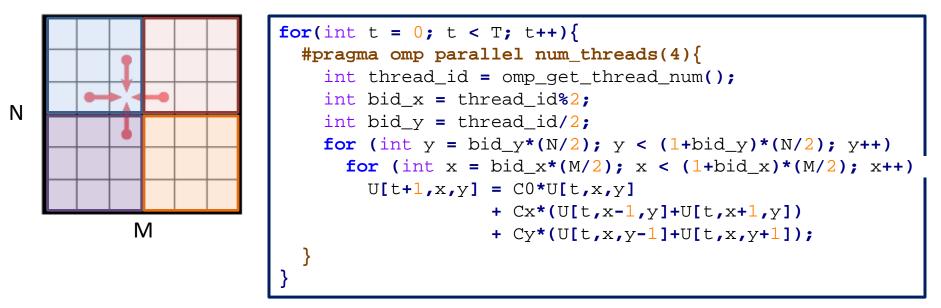

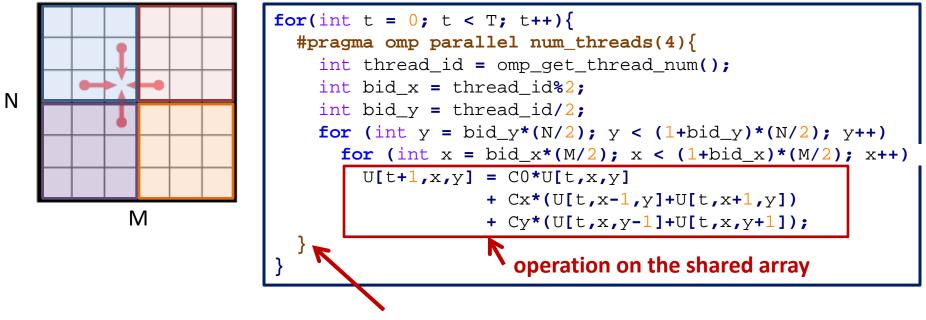

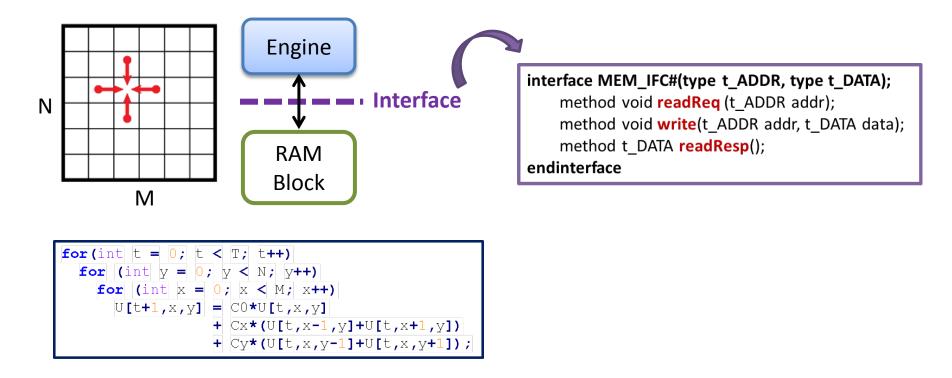

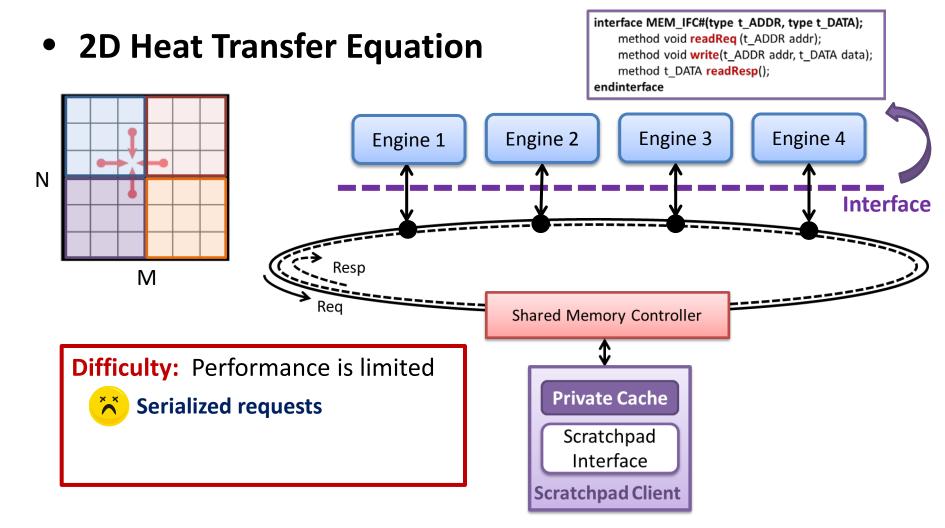

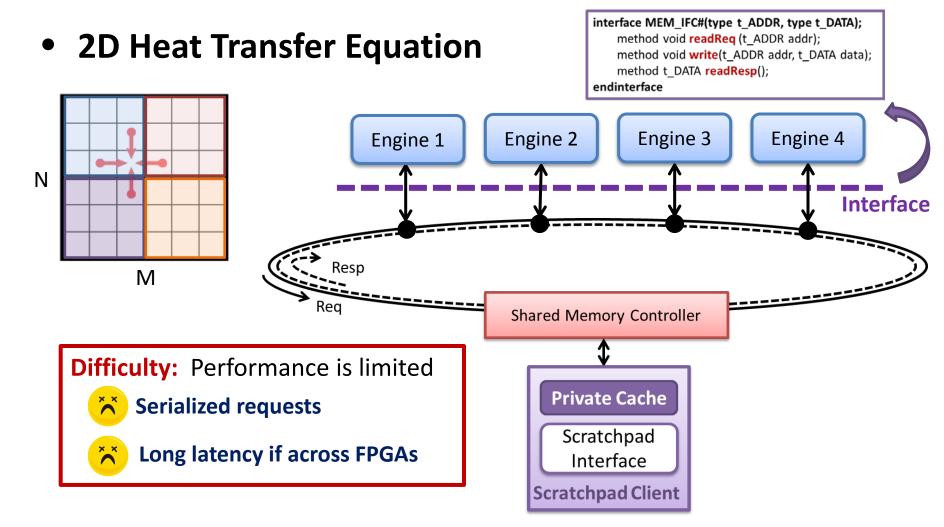

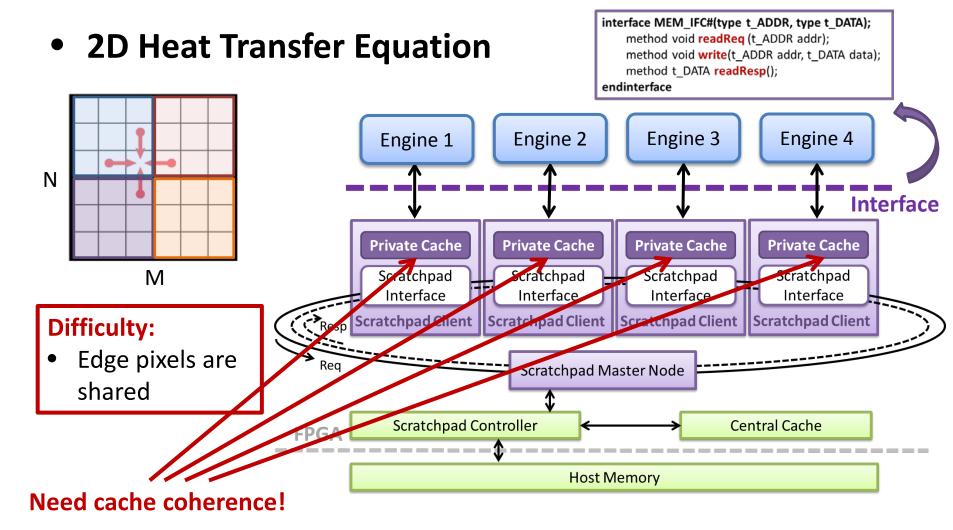

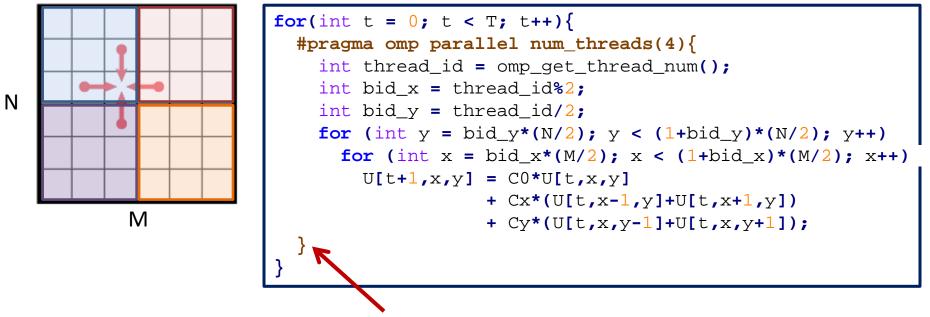

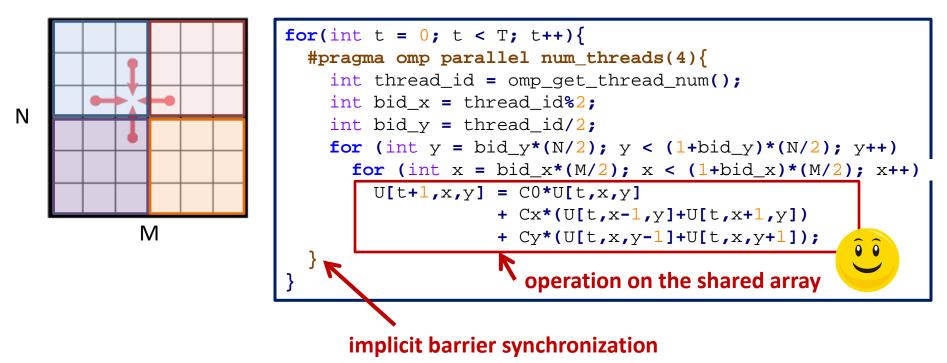

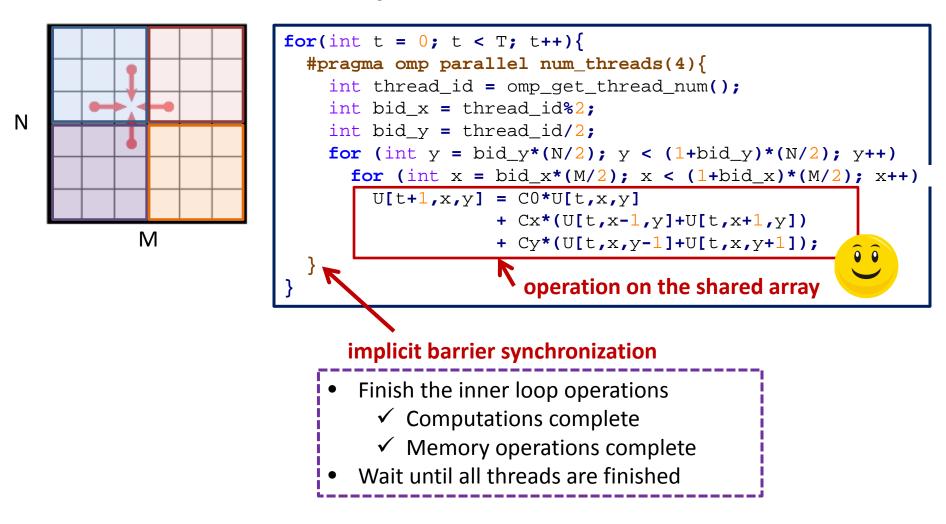

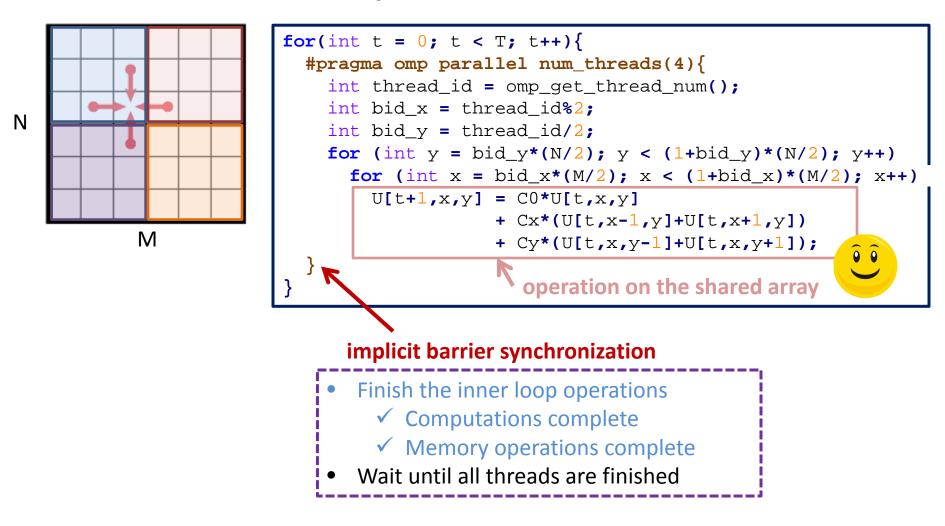

- 2D Heat Transfer Equation

- Goal: simplifying parallel programming on FPGAs

- 2D Heat Transfer Equation

- Goal: simplifying parallel programming on FPGAs

- 2D Heat Transfer Equation

- Goal: simplifying parallel programming on FPGAs

- 2D Heat Transfer Equation

implicit barrier synchronization

for (int t

= 0; t < T; t++) {

- Goal: simplifying parallel programming on FPGAs

- 2D Heat Transfer Equation

Ν

- Goal: simplifying parallel programming on FPGAs

- 2D Heat Transfer Equation

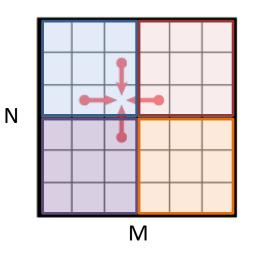

#### How to implement on FPGAs?

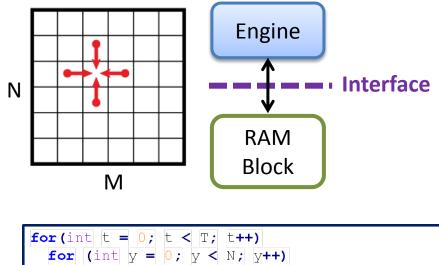

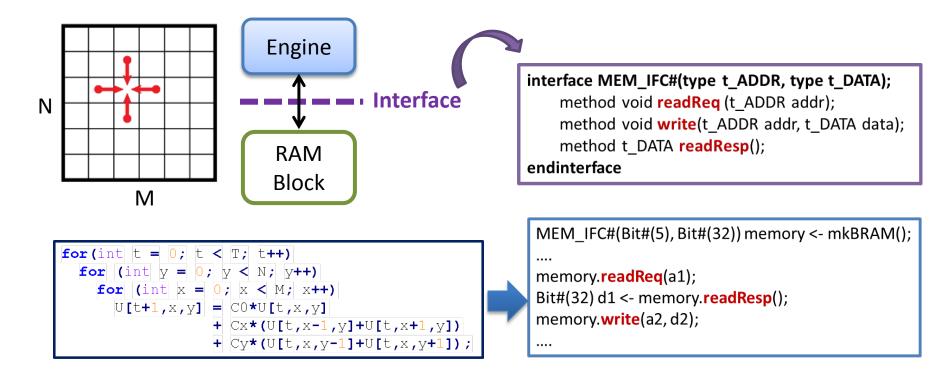

• 2D Heat Transfer Equation (using FPGA Block RAM)

| for (int y = 0, | ; y < N; y++)                 |

|-----------------|-------------------------------|

| for (int x =    | 0; x < M; x++)                |

| U[t+1,x,y]      | = C0*U[t,x,y]                 |

|                 | + Cx*(U[t,x-1,y]+U[t,x+1,y])  |

|                 | + Cy*(U[t,x,y-1]+U[t,x,y+1]); |

• 2D Heat Transfer Equation (using FPGA Block RAM)

• 2D Heat Transfer Equation (using FPGA Block RAM)

• 2D Heat Transfer Equation (using FPGA Block RAM)

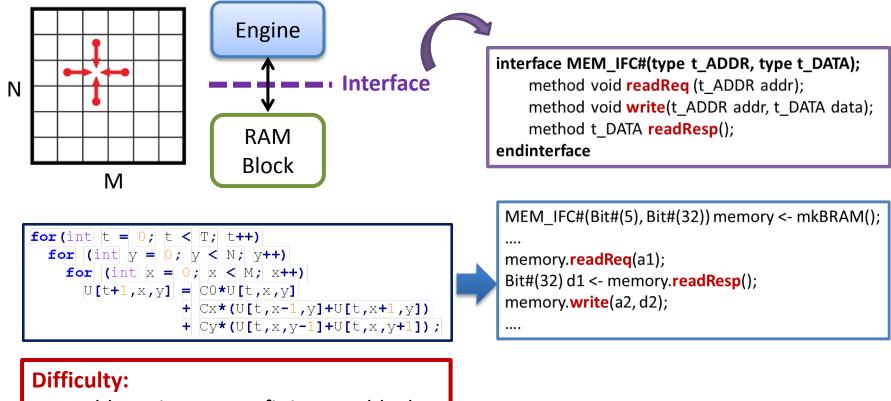

• Problem size cannot fit in RAM block

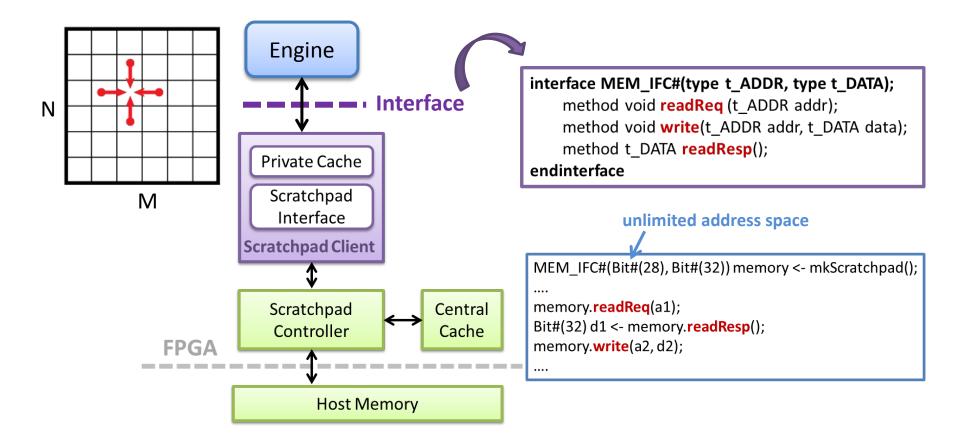

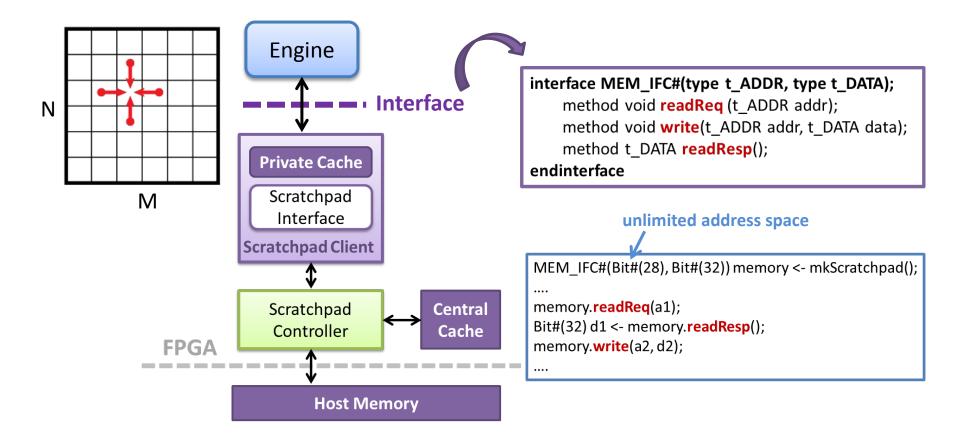

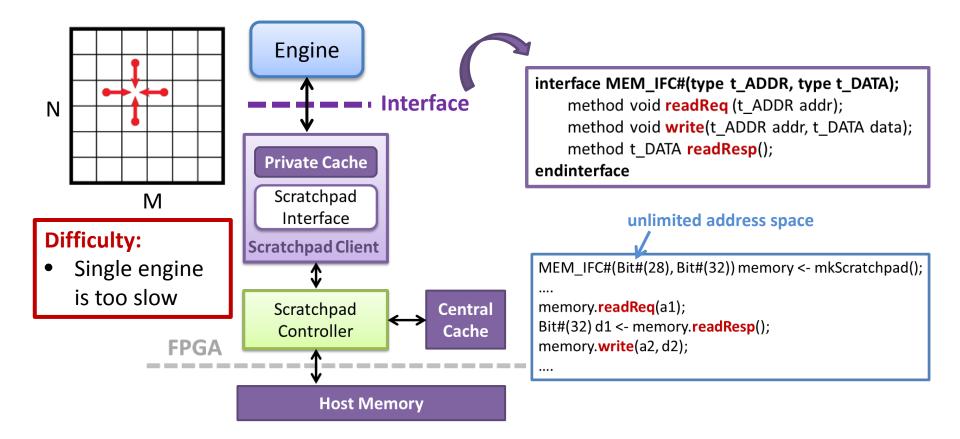

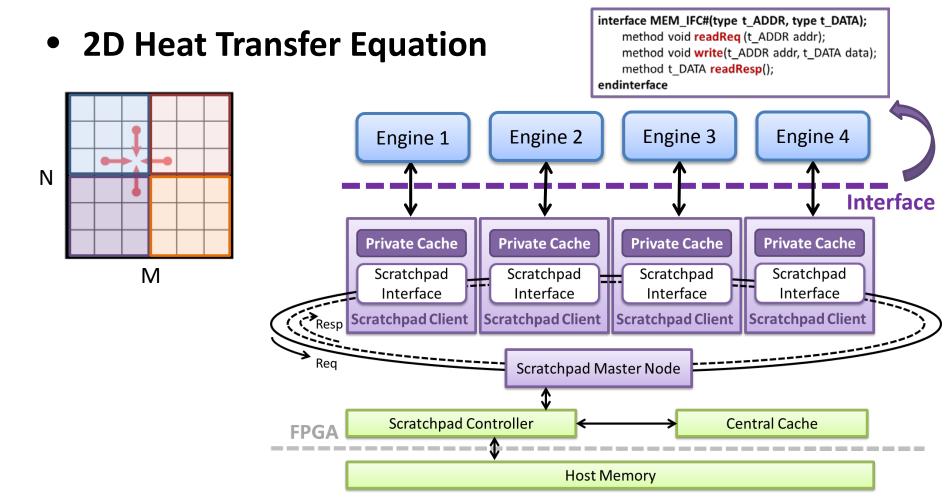

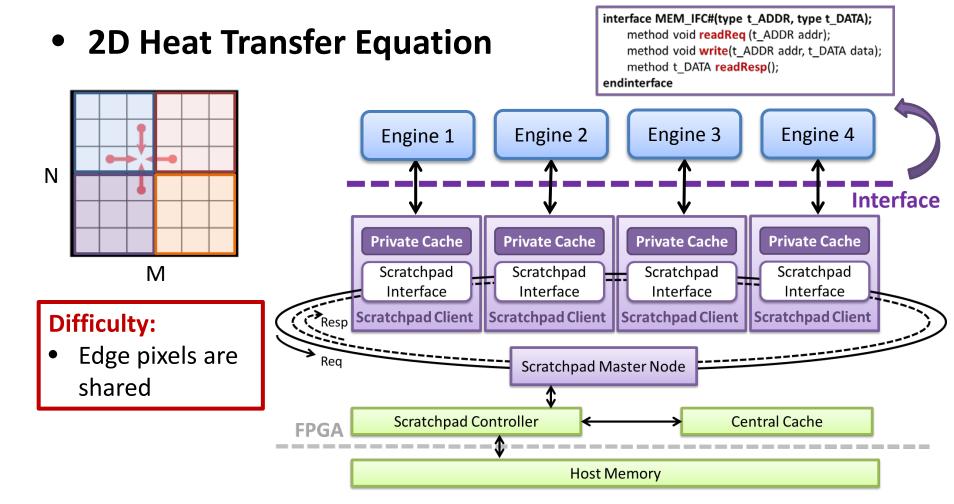

• 2D Heat Transfer Equation (using LEAP Scratchpad)

M. Adler et al., "LEAP Scratchpads," in FPGA, 2011.

• 2D Heat Transfer Equation (using LEAP Scratchpad)

M. Adler et al., "LEAP Scratchpads," in FPGA, 2011.

• 2D Heat Transfer Equation (using LEAP Scratchpad)

M. Adler et al., "LEAP Scratchpads," in FPGA, 2011.

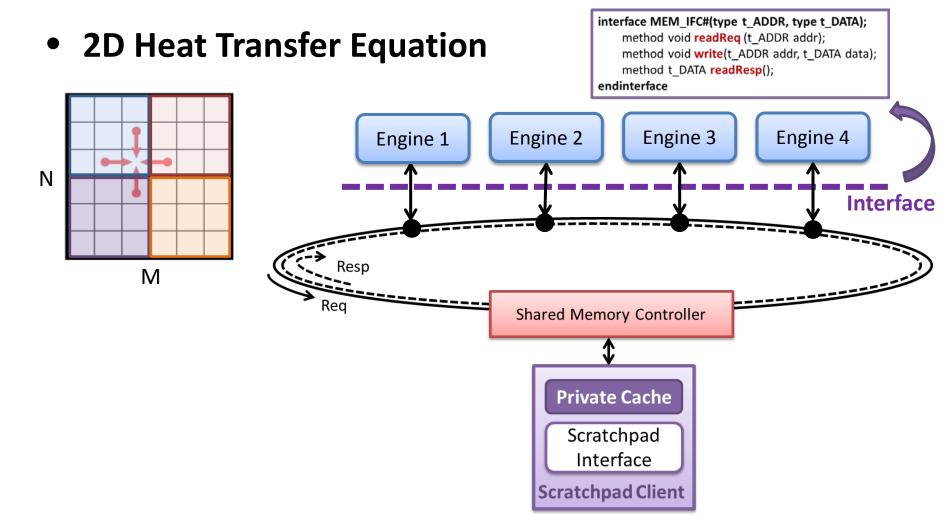

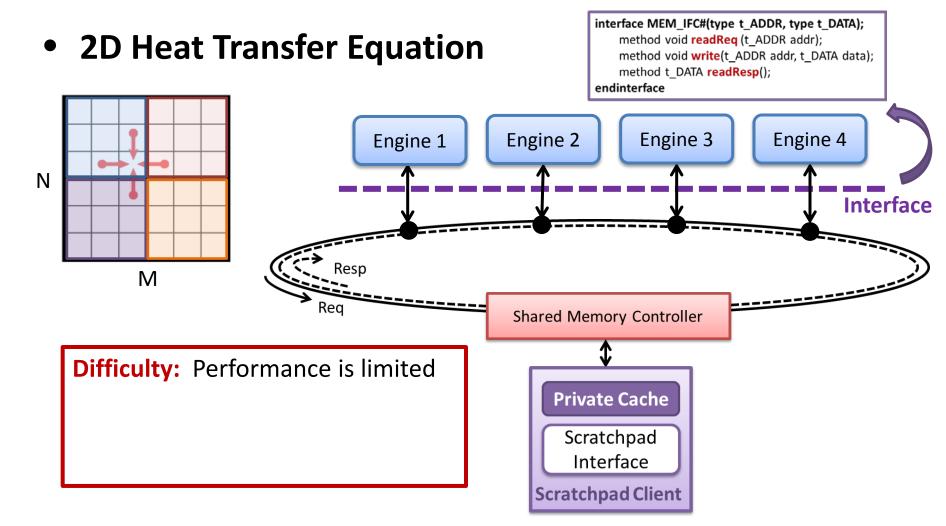

#### • 2D Heat Transfer Equation

implicit barrier synchronization

#### • 2D Heat Transfer Equation

#### • 2D Heat Transfer Equation

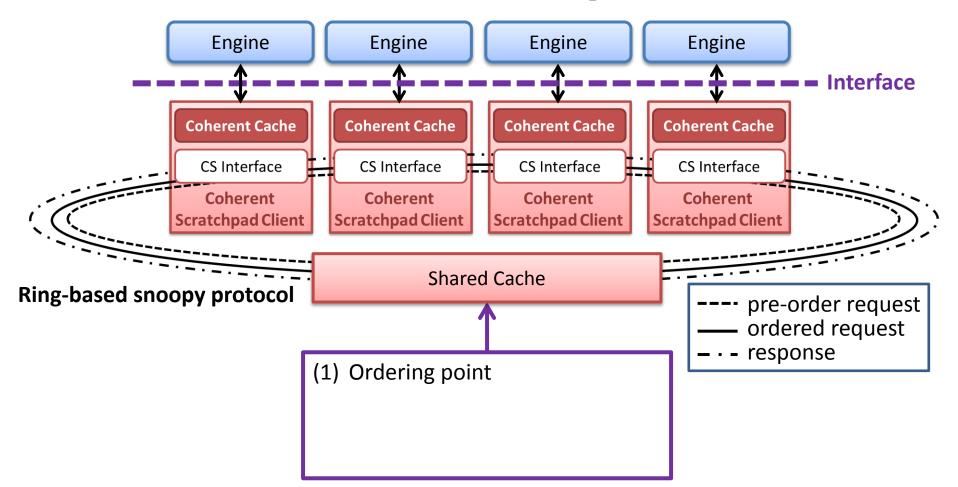

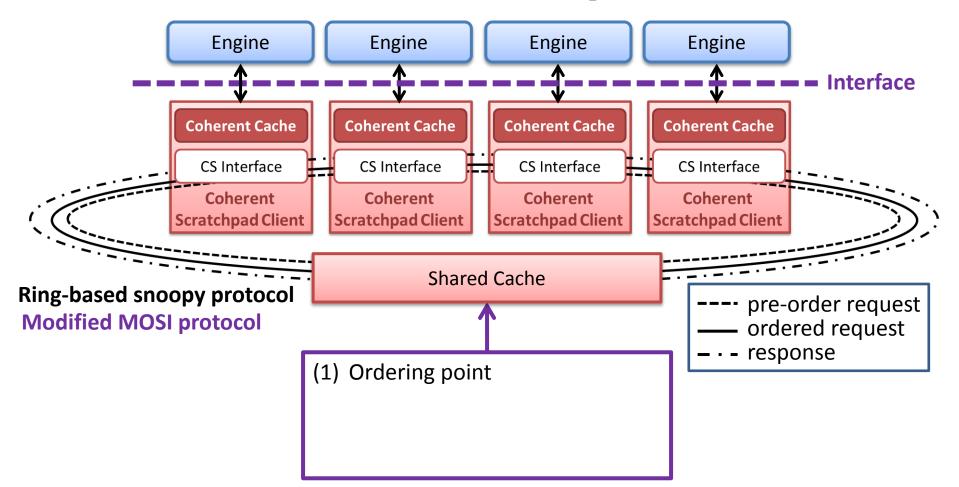

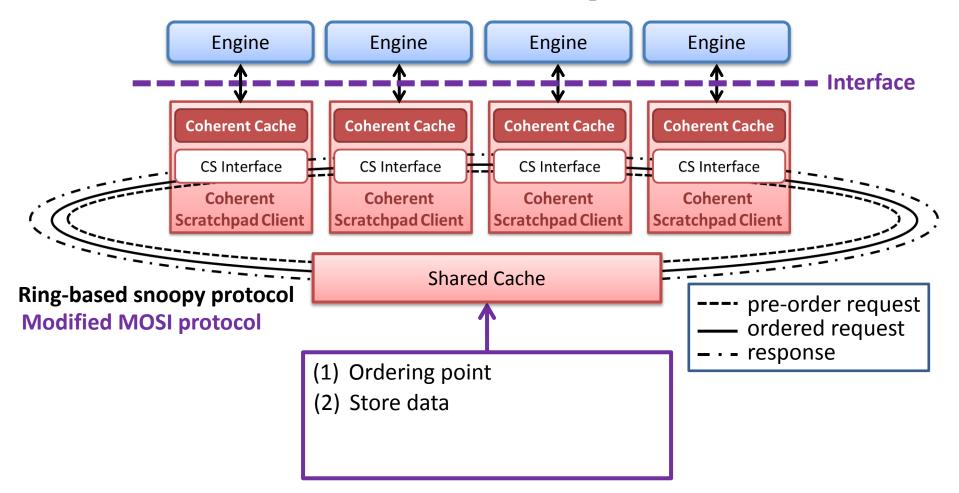

### Shared Memory Services: Memory Consistency

#### • Block RAM/Private Scratchpad Interface

#### interface MEM\_IFC#(type t\_ADDR, type t\_DATA);

method void readReq (t\_ADDR addr); method void write(t\_ADDR addr, t\_DATA data); method t\_DATA readResp();

endinterface

#### • Coherent Scratchpad Interface

interface MEM\_IFC#(type t\_ADDR, type t\_DATA); method void readReq (t\_ADDR addr); method void write(t\_ADDR addr, t\_DATA data); method t\_DATA readResp(); // t\_REQ r := {READ, WRITE, FULL} method Bool requestPending(t\_REQ r); endinterface

### Shared Memory Services: Memory Consistency

#### • Block RAM/Private Scratchpad Interface

#### interface MEM\_IFC#(type t\_ADDR, type t\_DATA);

method void readReq (t\_ADDR addr); method void write(t\_ADDR addr, t\_DATA data); method t\_DATA readResp();

endinterface

#### • Coherent Scratchpad Interface

| interface MEM_IFC#(type t_ADDR, type t_DATA);        |                      |  |

|------------------------------------------------------|----------------------|--|

| method void <b>readReq</b> (t_ADDR addr);            |                      |  |

| method void <b>write</b> (t_ADDR addr, t_DATA data); |                      |  |

| method t_DATA                                        |                      |  |

| // t_REQ r := {READ, WRITE, FULL}                    |                      |  |

| method Bool requestPending(t_REQ r);                 | Fence support        |  |

| endinterface                                         | (memory consistency) |  |

#### • 2D Heat Transfer Equation

### Synchronization Services: Memory Barrier

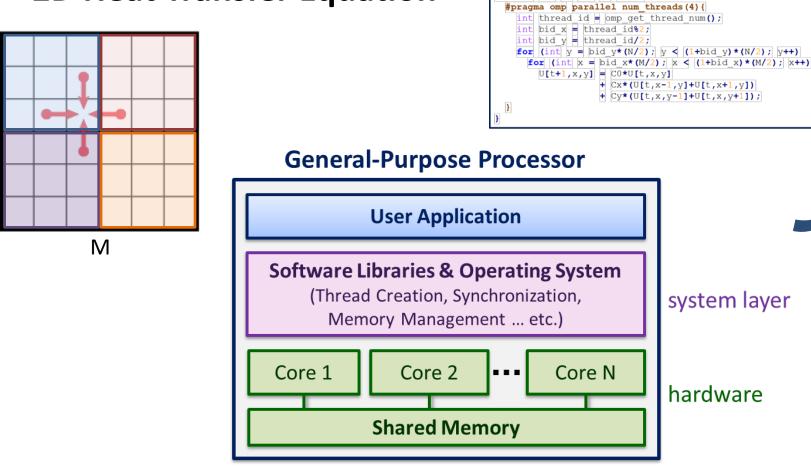

#### • In Processor: software through-memory barriers

- via shared memory & locks

| User Application                                                                                       |               |  |

|--------------------------------------------------------------------------------------------------------|---------------|--|

| Software Libraries & Operating System<br>(Thread Creation, Synchronization,<br>Memory Management etc.) |               |  |

| Core 1                                                                                                 | Core 2 Core N |  |

| Shared Memory                                                                                          |               |  |

```

void barrier(num threads const, lock addr, eflag addr,

lflag_addr, ecounter_addr, lcounter_addr)

while (*eflag_addr);

lock(lock addr);

(*ecounter addr)++;

if ((*ecounter_addr) == num_thread_const){

(*eflag_addr) = 0;

(*lflag_addr) = 1;

unlock(lock addr);

while (*lflag_addr);

lock(lock_addr);

(*lcounter_addr)++;

if ((*lcounter_addr) == num_thread_const){

(*lcounter addr) = 0;

(*ecounter_addr) = 0;

(*eflag_addr) = 1;

(*lflag_addr) = 0;

unlock(lock addr);

```

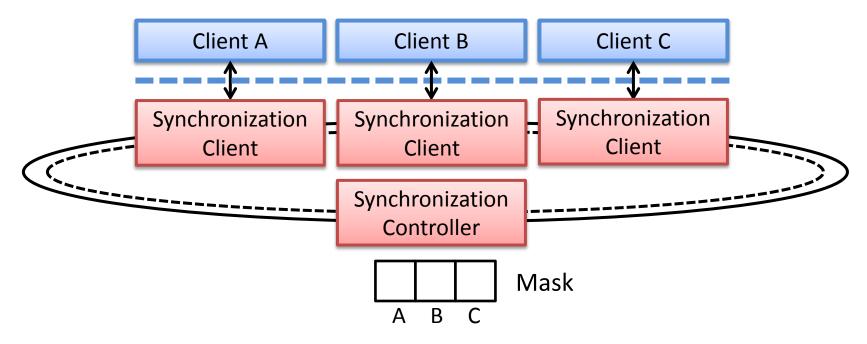

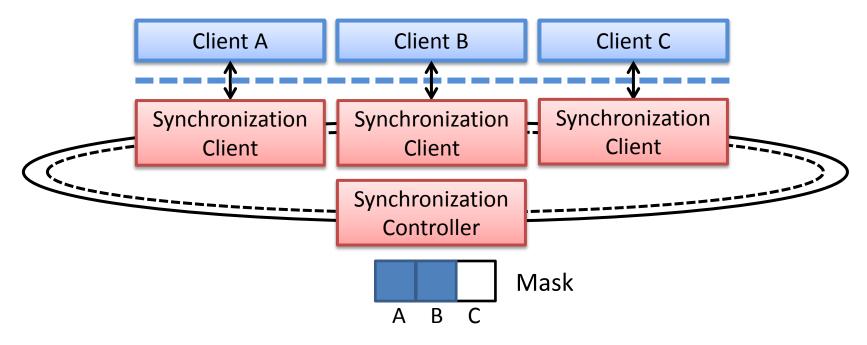

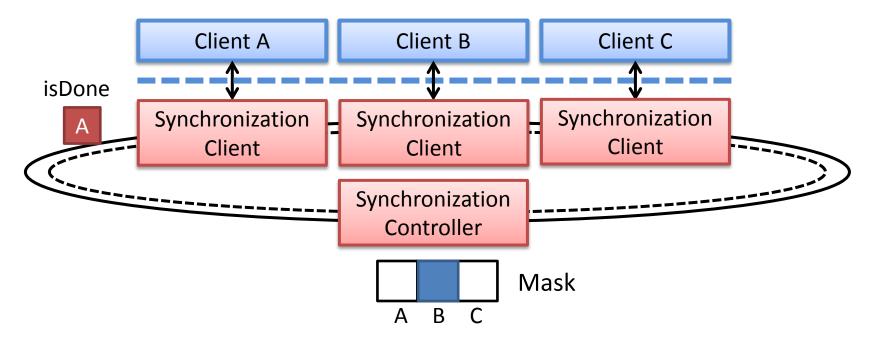

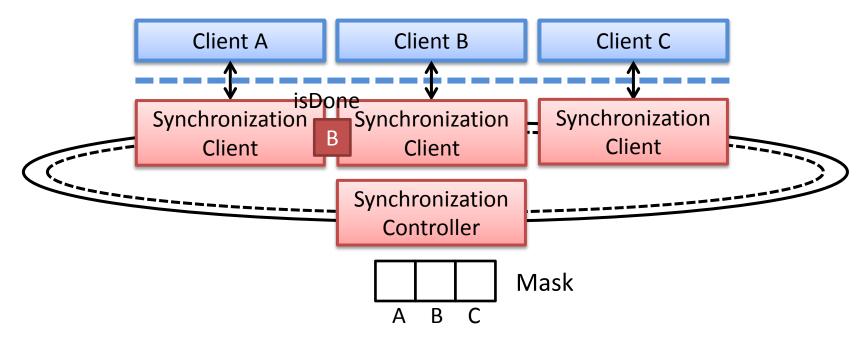

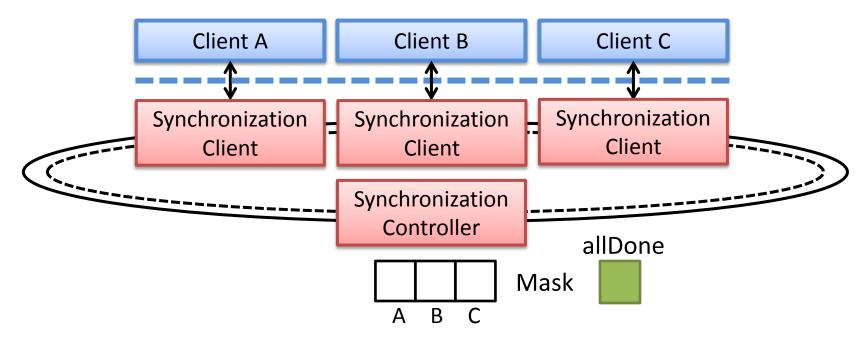

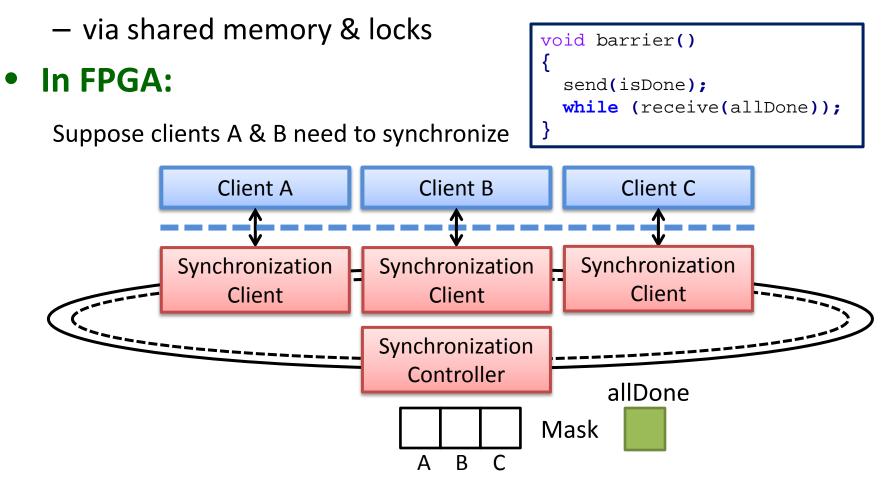

### Synchronization Services: Memory Barrier

- In Processor: software through-memory barriers

- via shared memory & locks

- In FPGA:

### • In Processor: software through-memory barriers

- via shared memory & locks

#### • In FPGA:

### • In Processor: software through-memory barriers

- via shared memory & locks

### • In FPGA:

### • In Processor: software through-memory barriers

- via shared memory & locks

#### • In FPGA:

### • In Processor: software through-memory barriers

- via shared memory & locks

#### • In FPGA:

### • In Processor: software through-memory barriers

- via shared memory & locks

#### • In FPGA:

### • In Processor: software through-memory barriers

- In Processor: software through-memory barriers

- via shared memory & locks

- In FPGA:

- outside of shared memory

- Performance Comparison:

| System                                           | Barriers per<br>Second | Normalized<br>Throughput |

|--------------------------------------------------|------------------------|--------------------------|

| LEAP Barrier Service                             | 7352076                | 342                      |

| Hardware Lock Barrier via<br>Coherent Scratchpad | 85088                  | 4                        |

| Spin-Lock Mutex-Enabled Cache*                   | 21510                  | 1                        |

\* V. Mirian and P. Chow, "Managing mutex variables in a cache-coherent shared-memory system for FPGAs," in FPT, 2012.

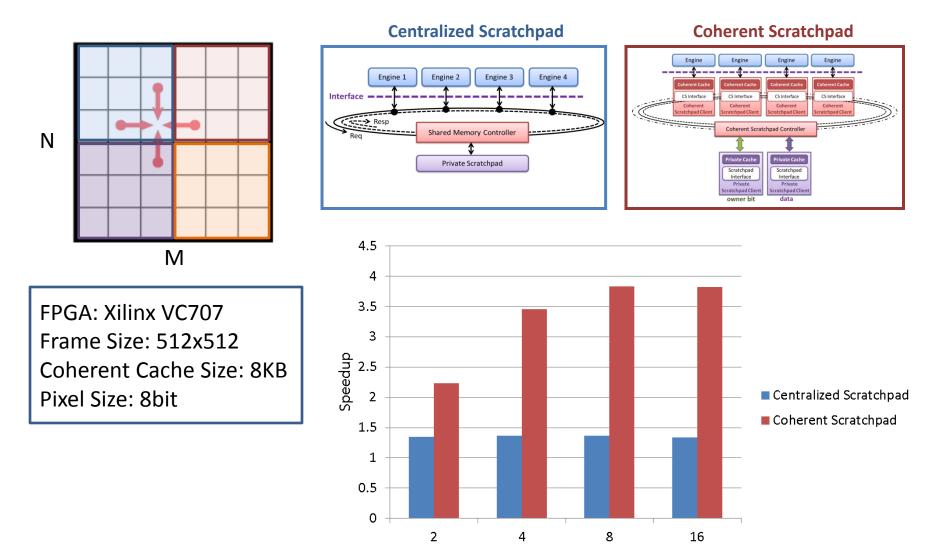

## **Performance on 2D Heat Transfer**

Number of Engines

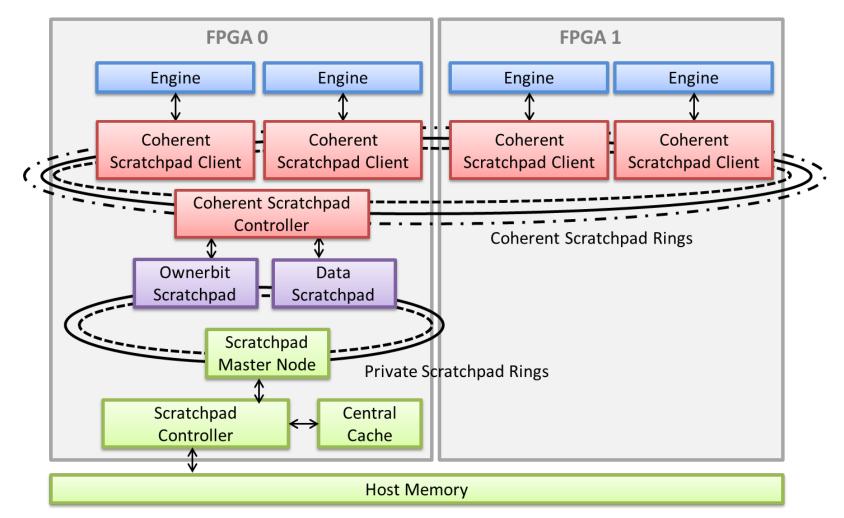

## Coherent Scratchpads on Multiple FPGAs

K. Fleming et al., "Leveraging latency-insensitivity to ease multiple FPGA design," in FPGA, 2012.

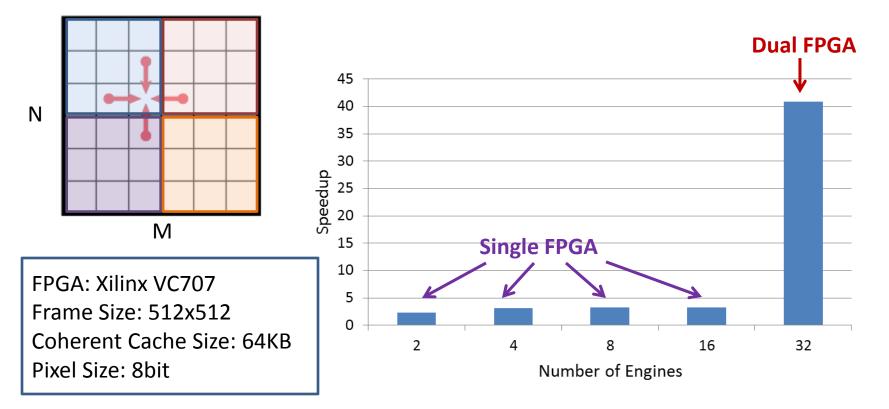

### **Performance of Dual FPGA**

### • 2D Heat Transfer Equation

# Conclusion

- Programming on FPGA is difficult due to the lack of useful abstractions

- We provide a set of FPGA-based shared memory primitives:

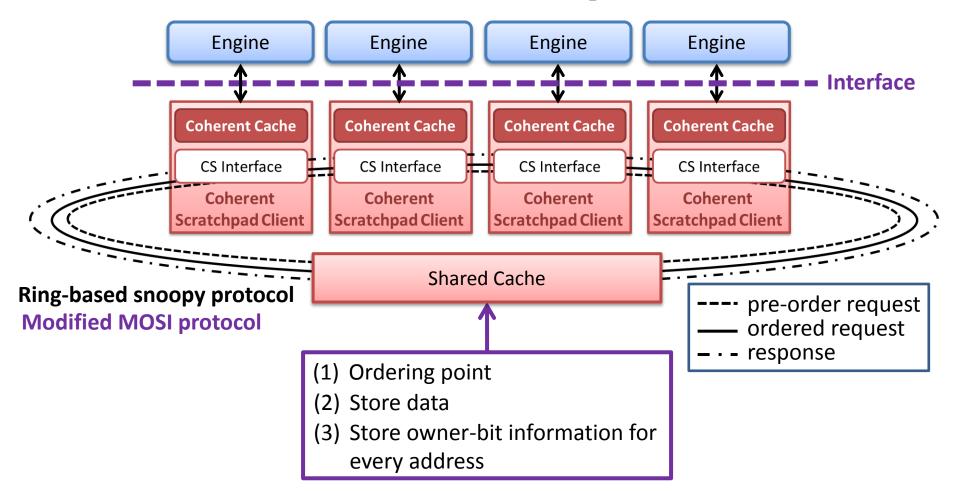

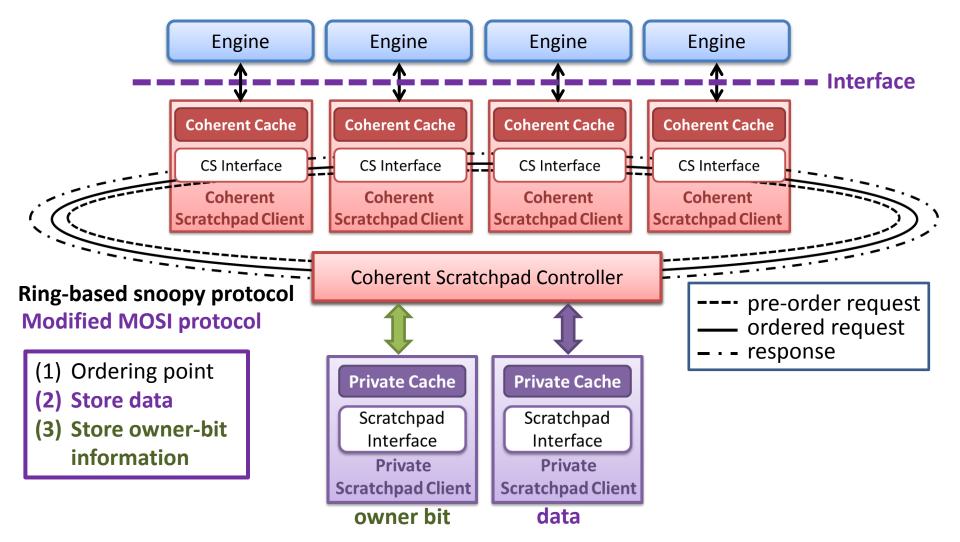

- Coherent scratchpads: manage multiple coherent caches

- Synchronization primitives

- We improve programming efficiency

- Common interface:

Block RAM -> multi-FPGA coherent memory

- It took only a few hours to write the 2D heat transfer equation

## **Thank You**