# Sparse Computations on GPUs

Changwan Hong 04/25/24

\* Disclaimer: The methods described here are simplified/modified for easier understanding and are not highly accurate.

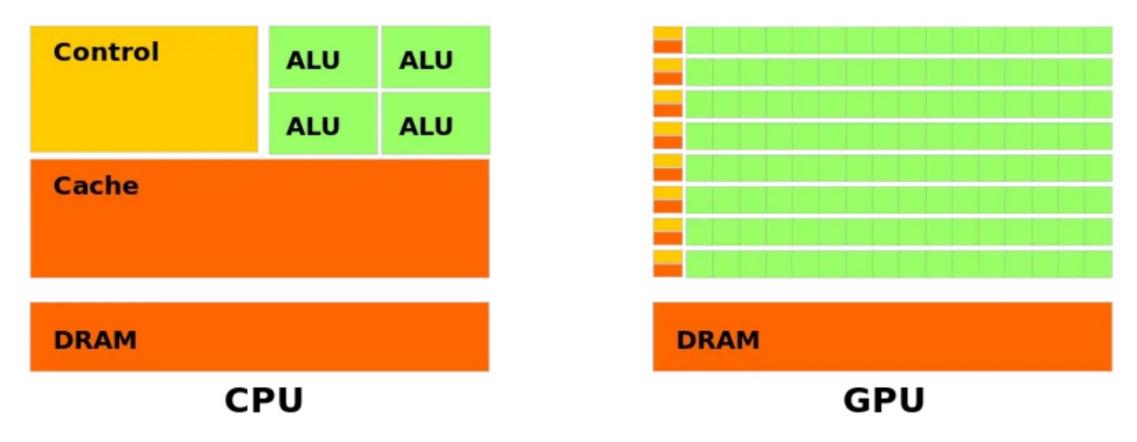

# **Recap on GPU Computing**

#### **Properties of GPUs:**

- Many lightweight cores ( high degree of parallelism )

- Extremely high computing power (FLOP/s)

- SIMD\* execution mode (all threads of a warp follow the same execution path)

- High memory bandwidth

- No sophisticated memory hierarchy, small caches

#### Why?

- Originally designed for graphics use

- No dependencies when updating pixels on a screen

- Many pixels need to be updated at the same time

#### How is the data accessed for general purpose computing?

- On CPUs: sophisticated memory hierarchy (L1, L2, L3...)

- On GPU: fast switching between contexts to hide latencies: execute operation on data that is present

# **GPU** Component

Left: CPU architecture; right: GPU architecture. Source: https://www.omnisci.com/technical-glossary/cpu-vs-

<u>gpu</u>.

\* https://medium.com/codex/understanding-the-architecture-of-a-gpu-d5d2d2e8978b

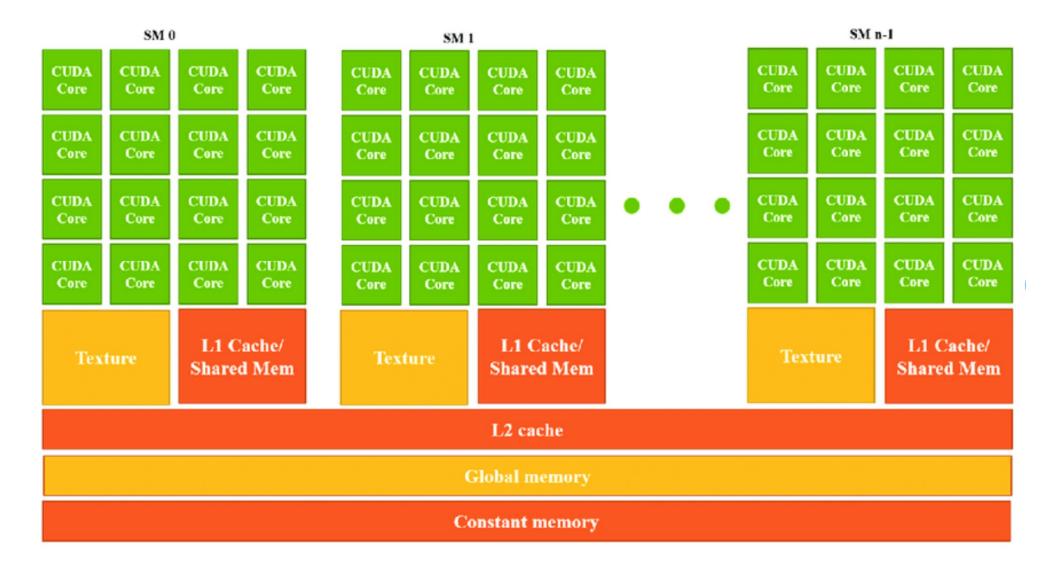

# **GPU Structure**

\* https://www.researchgate.net/figure/Schematic-of-NVIDIA-GPU-architecture-where-SM-refers-to-streamingmultiprocessor\_fig2\_321958738

# **Programming GPUs**

Fundamentally different from programming general purpose CPUs!

- On **GPU**s, we create a huge amount of independent threads.

- We organize the threads in thread blocks arranged as a grid.

threads

- One warp consists of 32 threads on Nvidia GPUs.

- You can think of the threads in a warp as being executed in single-instruction multiple-thread (SIMT) fashion.

- One thread block consists of a few warps, which users can configure."

- \* https://icl.utk.edu/~hanzt/talks/SparseMatricesAndParallelProcessingOnGPUs.pdf

```

global void kernel(int* a)

a[blockIdx.x*blockDim.x +

threadIdx.x]=0;

int main() {

dim3 block(4);

dim3 grid(n/block.x);

kernel<<<grid,block>>>(d a);

return 0;

```

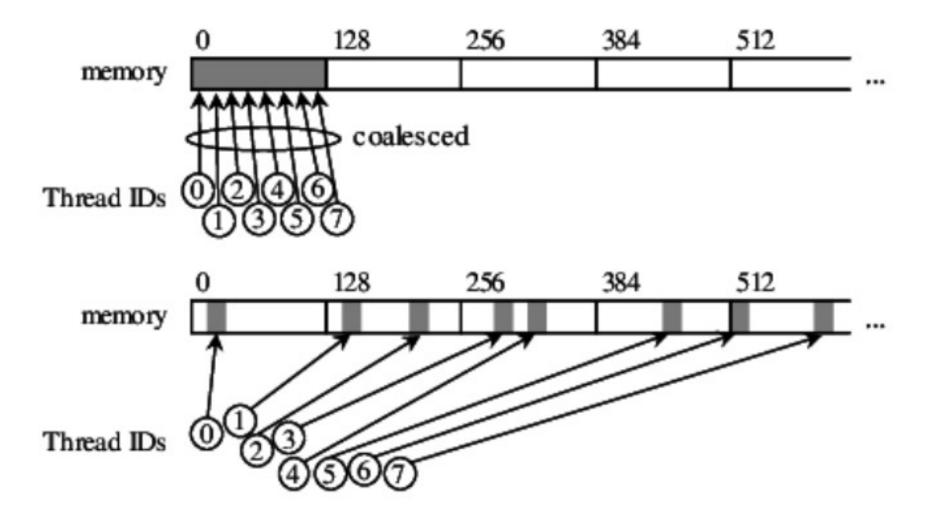

# **GPU Memory coalescing**

\* https://www.researchgate.net/figure/Memory-coalescing-fast-access-and-not-coalesced-slow-accessrepresentation\_fig2\_286446838

# **GPU Memory coalescing**

\* http://homepages.math.uic.edu/~jan/mcs572f16/mcs572notes/lec35.html

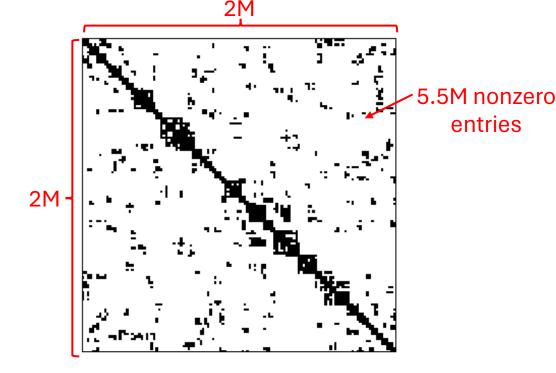

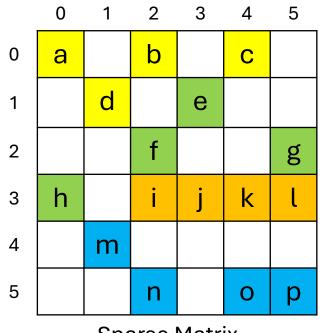

# Sparse matrix

- A matrix in which the majority of its elements are zero.

- Many real-world matrices exhibit sparsity.

- We need a compact representation that only stores the non-zero elements and their indices.

- The asymptotic time and space complexity for sparse matrix computations can be orders of magnitude worse otherwise (i.e., infeasible to compute and store).

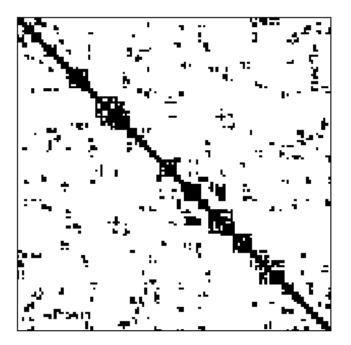

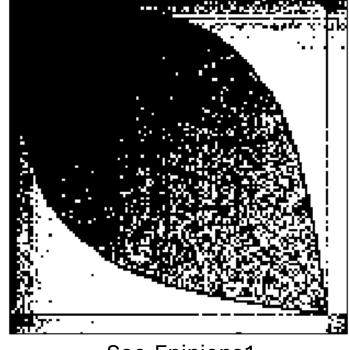

roadNet-CA (Road network of California)

Soc-Epinions1 (Who-trusts-whom network of Epinions.com)

\* http://sparse.tamu.edu

# Sparse matrix

- A matrix in which the majority of its elements are zero.

- Many real-world matrices exhibit sparsity.

- We need a compact representation that only stores the non-zero elements and their indices.

- The asymptotic time and space complexity for sparse matrix computations can be orders of magnitude worse otherwise (i.e., infeasible to compute and store).

roadNet-CA (Road network of California)

Soc-Epinions1 (Who-trusts-whom network of Epinions.com)

\* http://sparse.tamu.edu

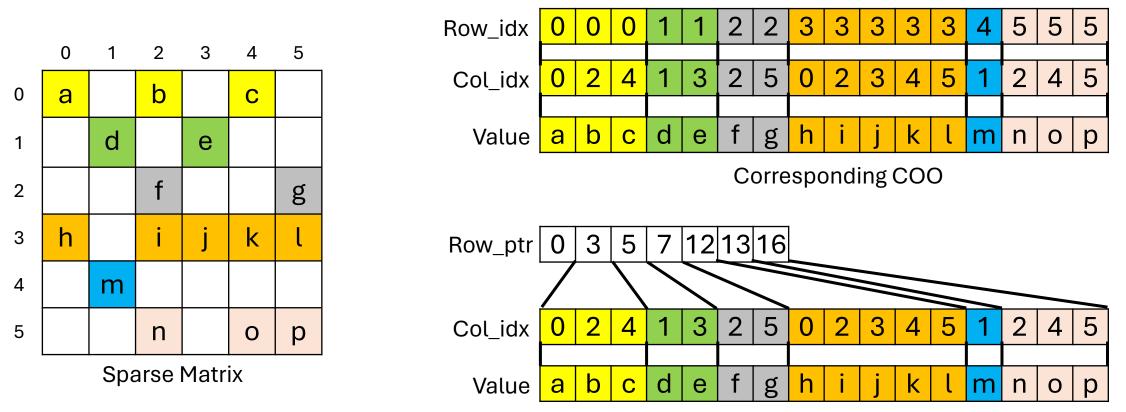

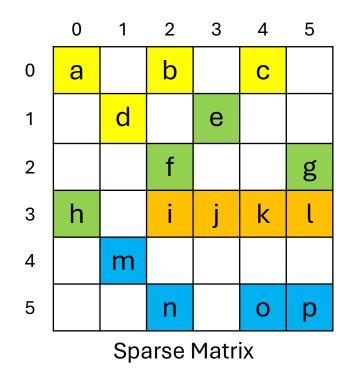

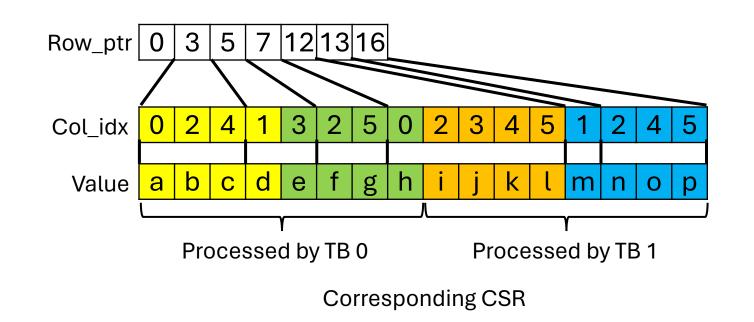

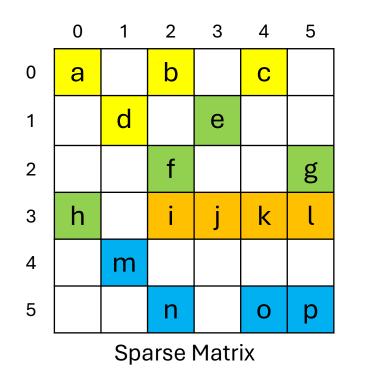

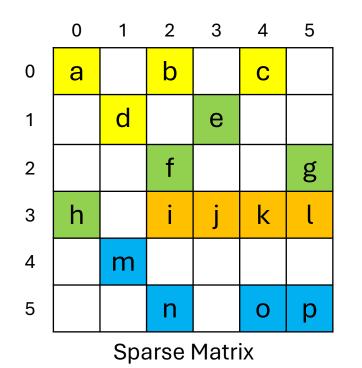

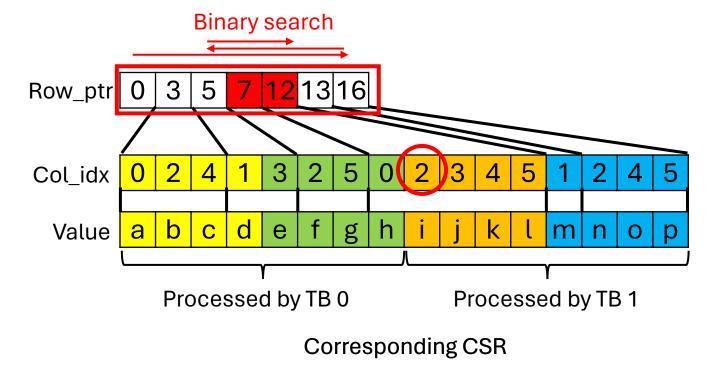

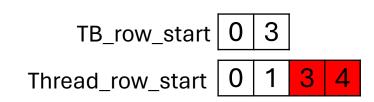

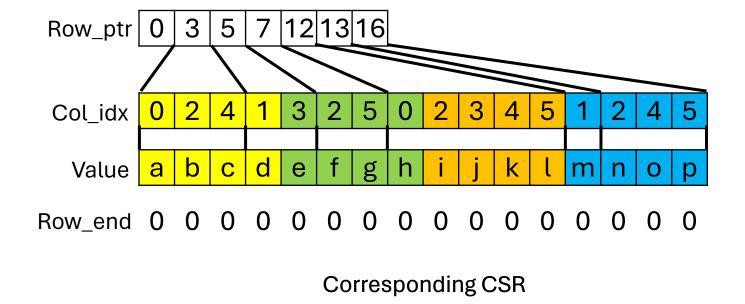

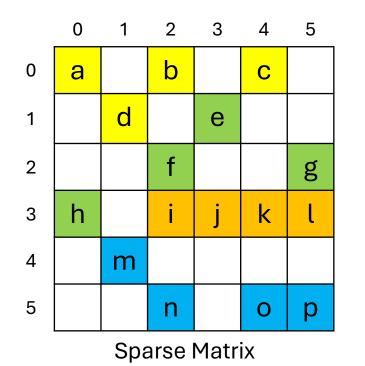

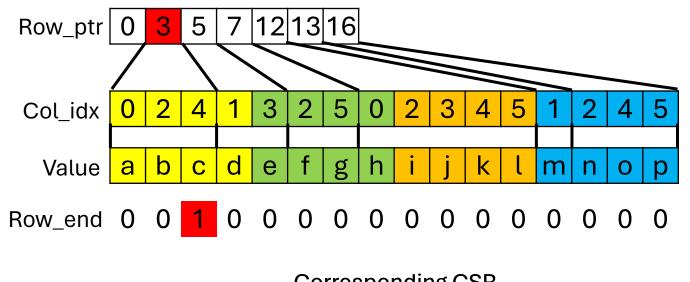

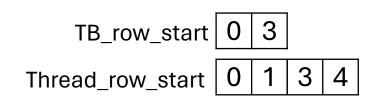

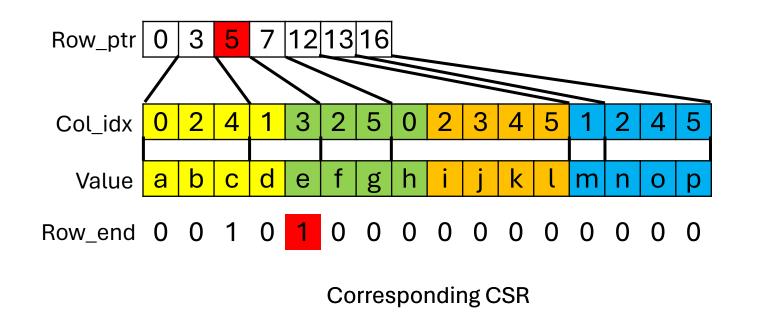

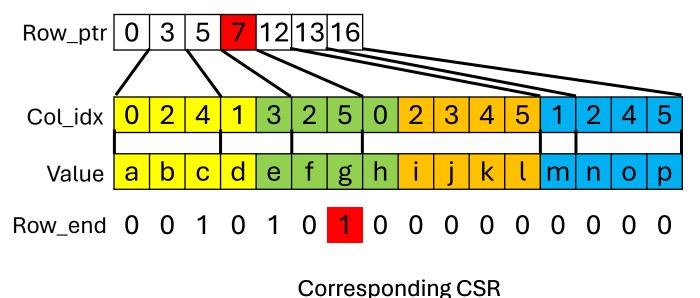

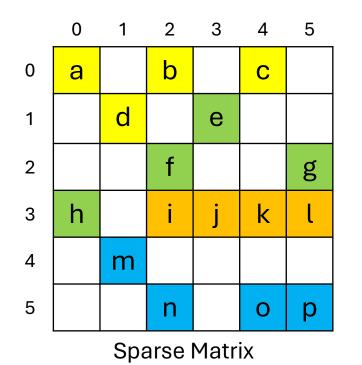

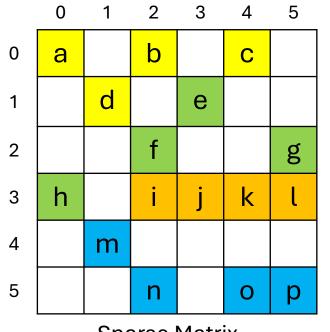

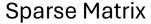

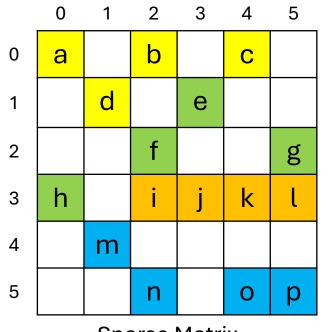

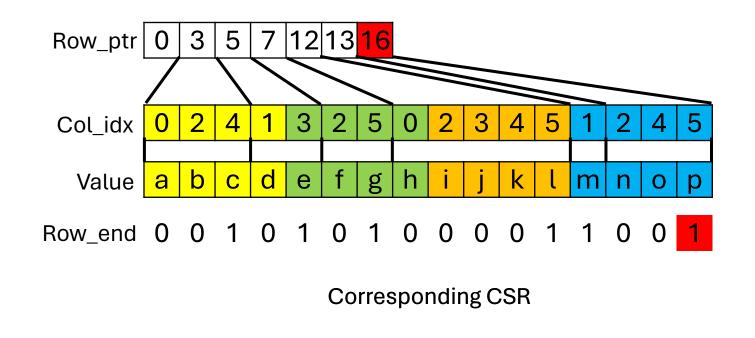

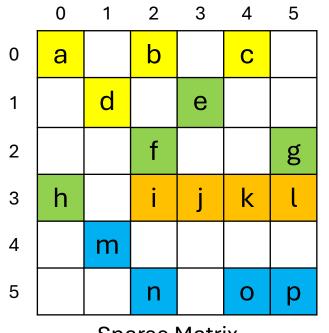

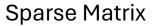

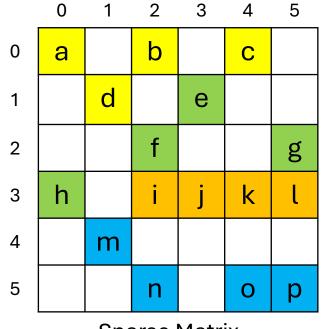

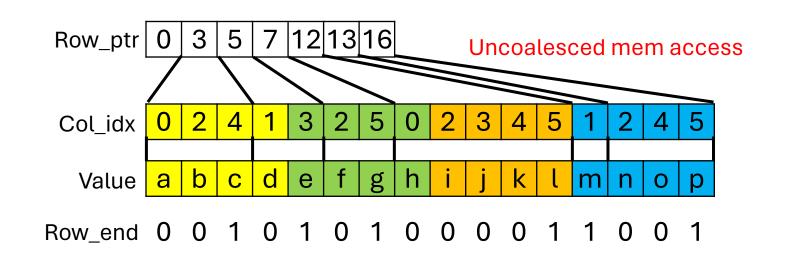

# **Compressed Sparse Row (CSR)**

- Compressed Sparse Row (CSR) and Coordinate format (COO) are the most popular data representations for sparse matrices.

- The row pointers indicate where each row starts in the other two arrays

- Column indices of each row is usually sorted in ascending order.

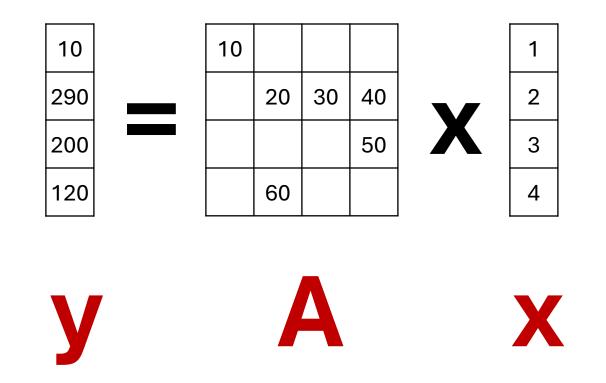

# What is SpMV?

Sparse Matrix-Vector Multiplication (SpMV) is computed by multiplying each row of the sparse matrix with the dense vector and summing the results to obtain the elements of the output vector.

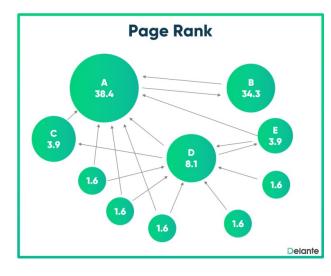

# SpMV is ubiquitous

# $\mathbf{A}\mathbf{X} = \lambda \mathbf{X}$

Graph algorithms

**Eiganvalue Systems**

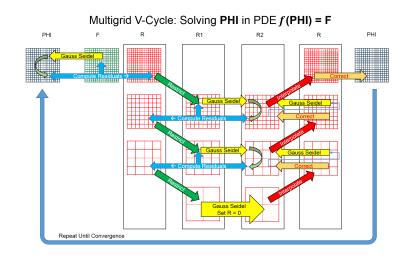

Multigrid method

\* https://delante.co/definitions/pagerank/

\* https://mathworld.wolfram.com/Eigenvalue.html

\* https://en.wikipedia.org/wiki/Multigrid\_method

# **Optimizing SpMV on GPUs is challenging**

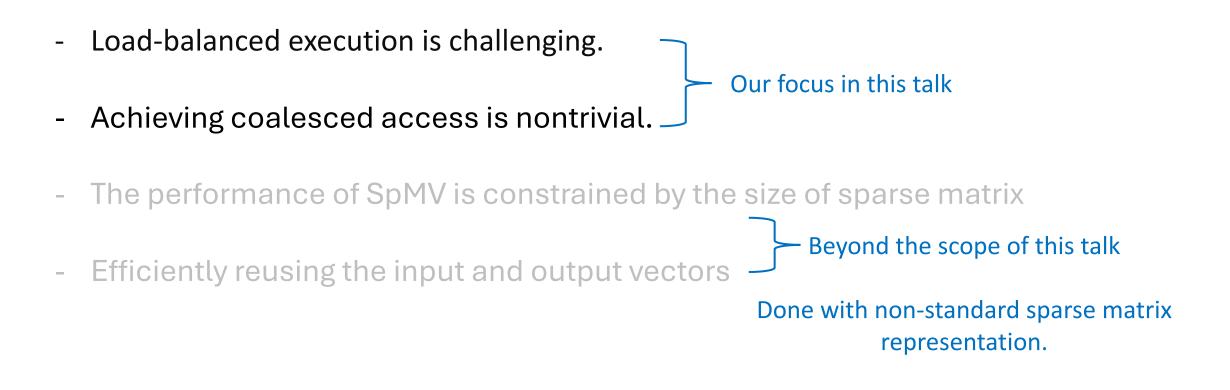

- Load-balanced execution is challenging.

- Achieving coalesced access is nontrivial.

- The performance of SpMV is constrained by the size of sparse matrix

- Efficiently reusing the input and output vectors

# **Optimizing SpMV on GPUs is challenging**

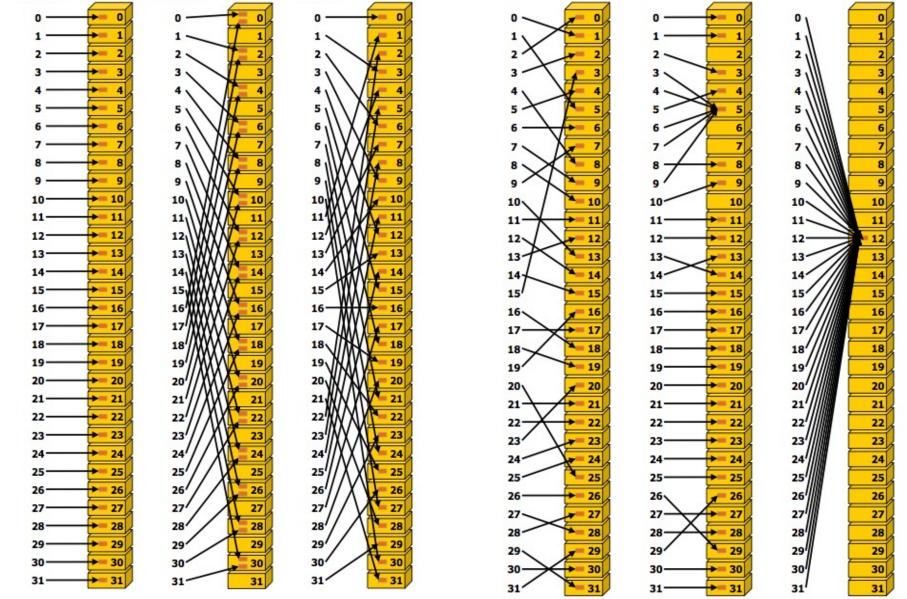

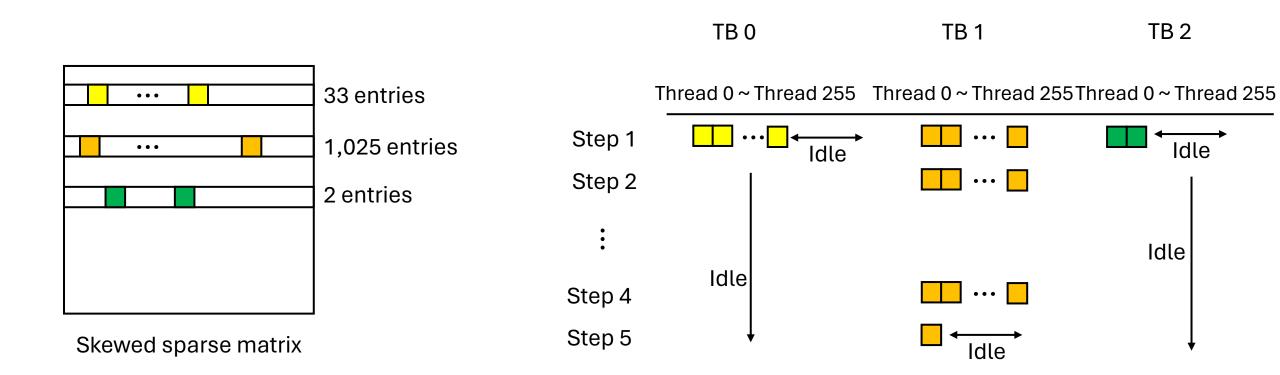

# How to assign threads to work?

- One thread per row

- One warp (=32 threads) per row

- One thread block (assuming 256 threads) per row

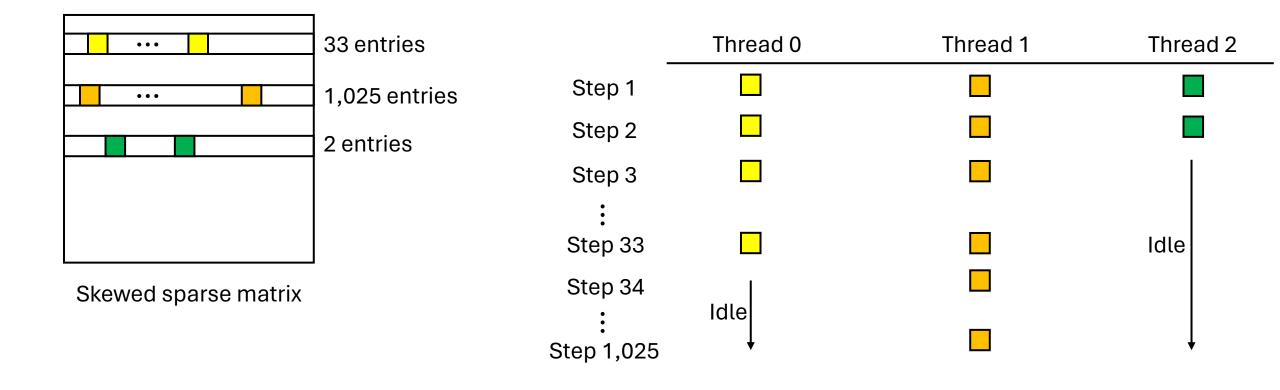

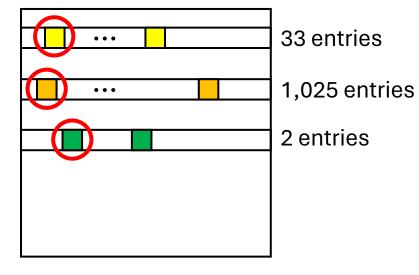

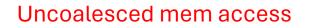

# One thread per row

- No reduction cost

- Can result in significant load-imbalance

- Can lead to uncoalesced memory accesses

# One thread per row

- No reduction cost

- Can result in significant load-imbalance

- Can lead to uncoalesced memory accesses

Skewed sparse matrix

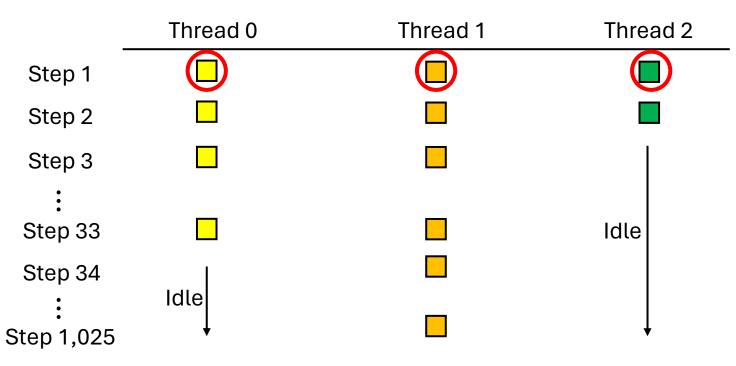

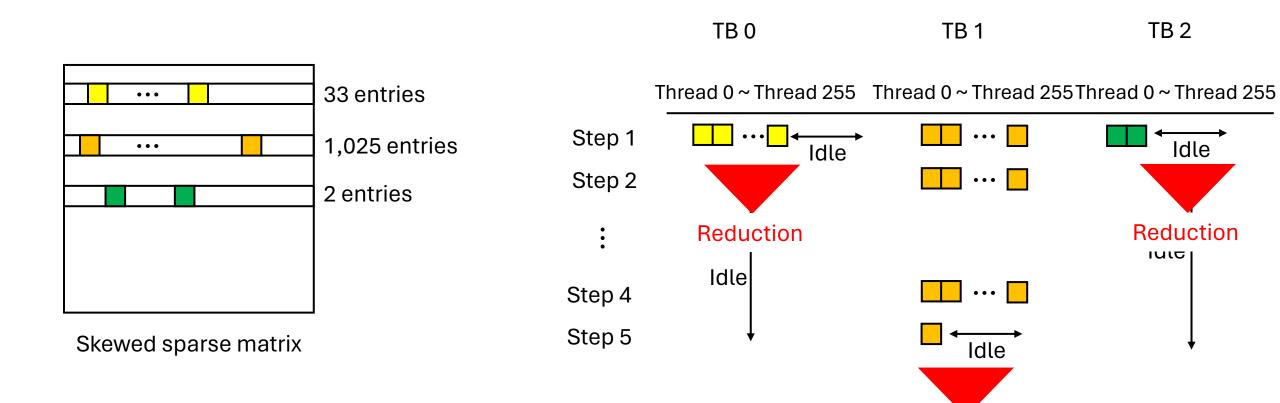

# One warp per row

- Result in reduction cost

- Can result in significant load-imbalance

# One warp per row

- Result in reduction cost

- Can result in significant load-imbalance

Reduction

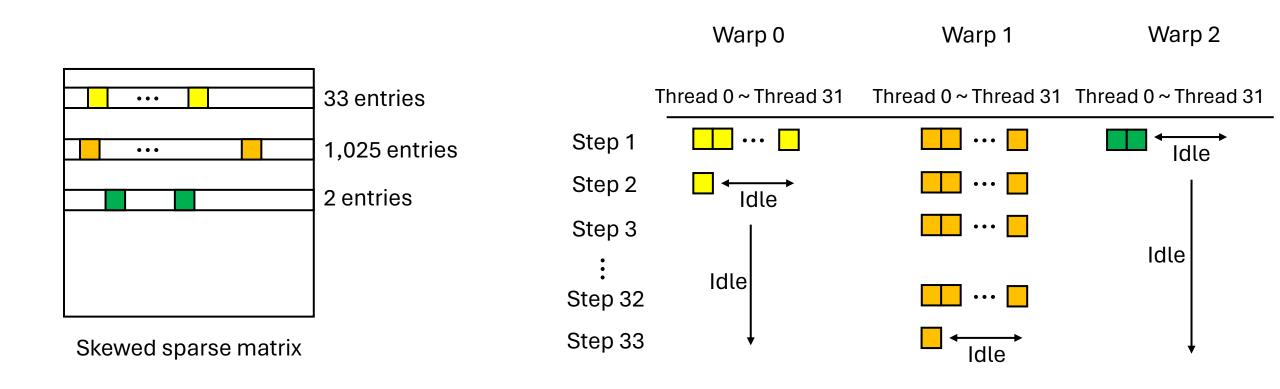

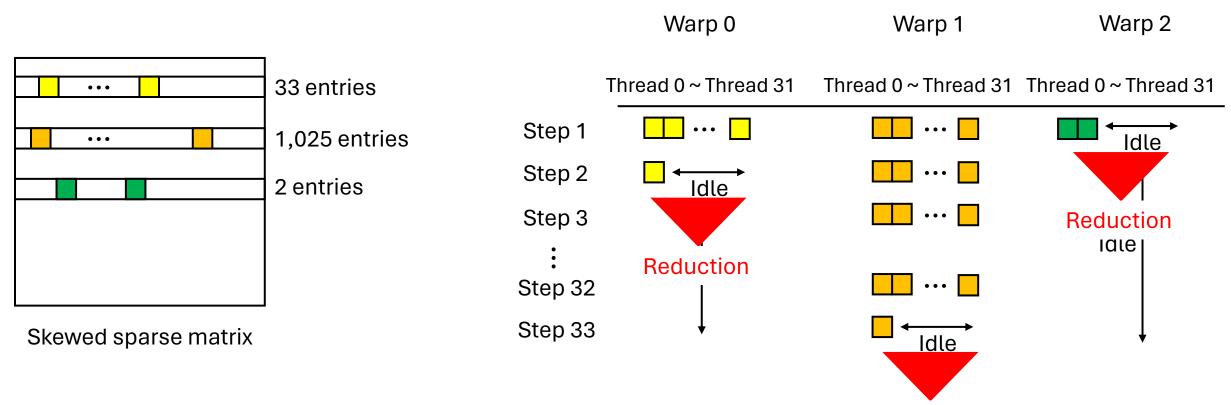

# One thread block per row

- Result in more reduction cost

- Can result in significant load-imbalance

# One thread block per row

- Result in more reduction cost

- Can result in significant load-imbalance

Reduction

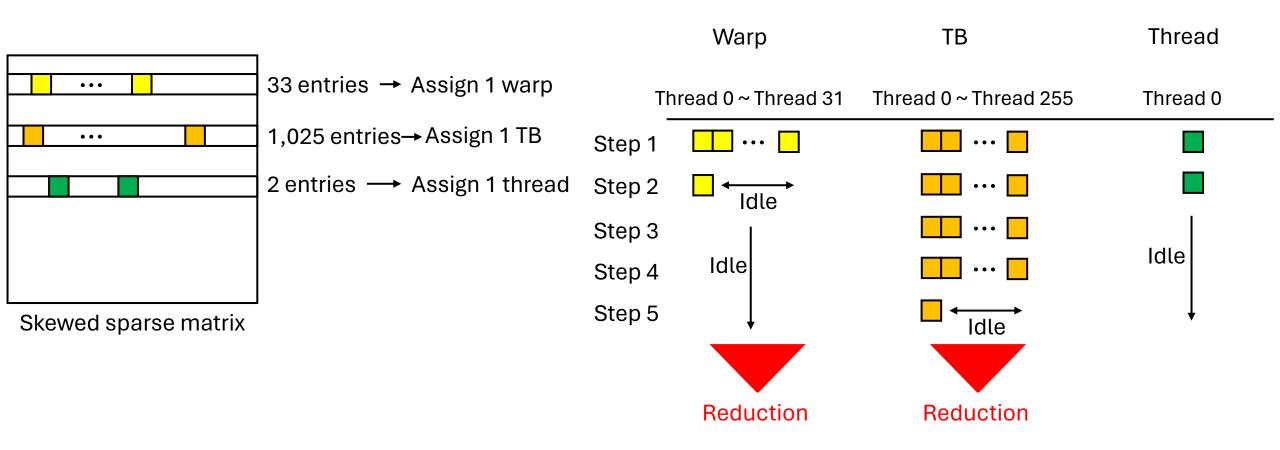

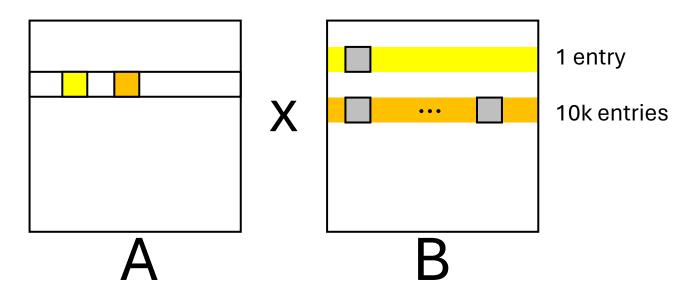

# Binning can partially resolve this problem

- A thread, warp, or thread block is assigned based on the number of entries in the row

- Still suffers from load-imbalance and reduction cost

\* Ashari, Arash, et al. "Fast sparse matrix-vector multiplication on GPUs for graph applications." SC'14: Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis. IEEE, 2014.

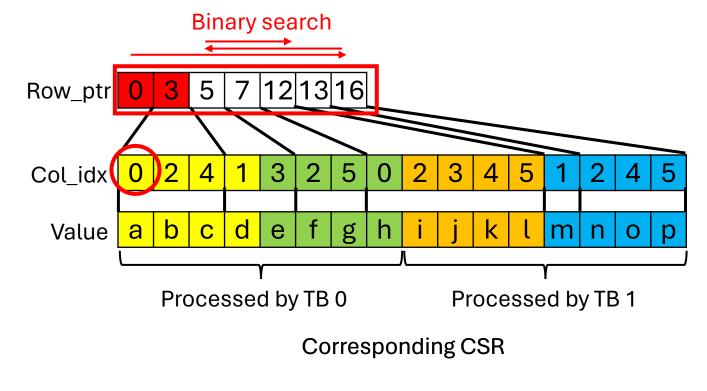

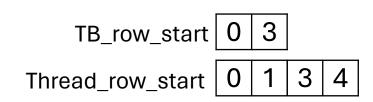

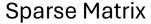

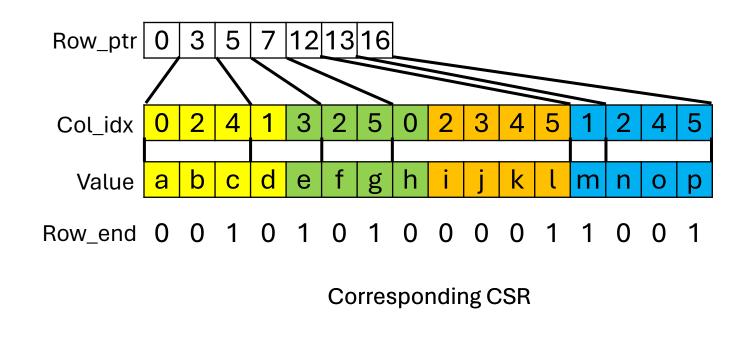

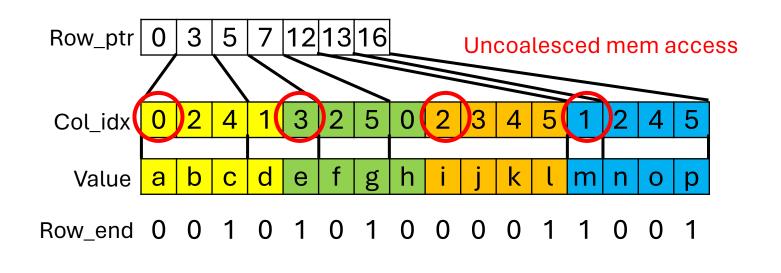

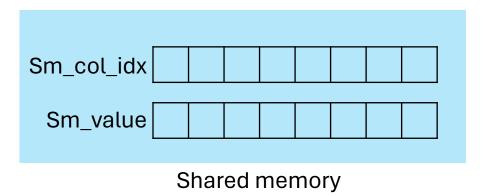

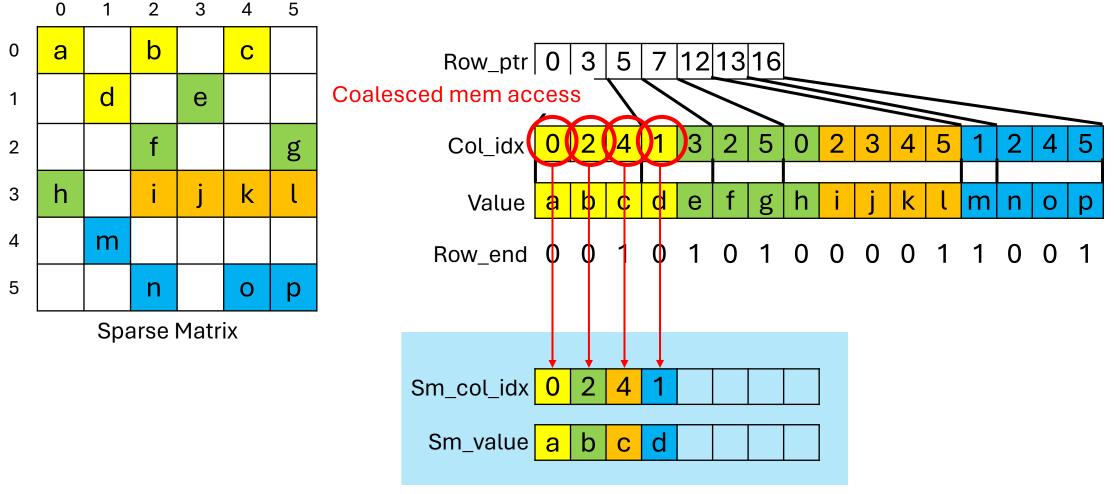

# Load-balanced SpMV with coalesced memory access

- Load imbalanced execution

- Ensure that each thread processes the same number of nonzero entries of the sparse matrix (i.e., strict nonzero splitting).

- Achieving coalesced memory access of the sparse matrix

- First load the sparse matrix into shared memory

- Achieving coalesced memory access of the output

- Use a shared memory buffer for the output

\* Steinberger, Markus, Rhaleb Zayer, and Hans-Peter Seidel. "Globally homogeneous, locally adaptive sparse matrix-vector multiplication on the GPU." Proceedings of the International Conference on Supercomputing. 2017.

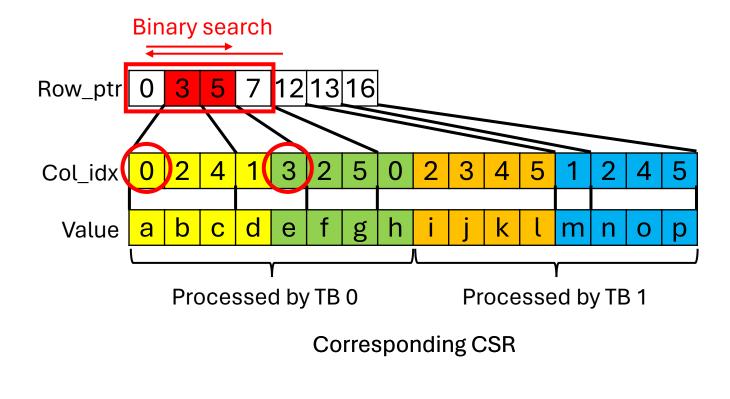

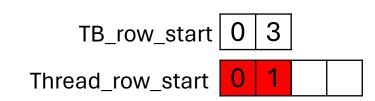

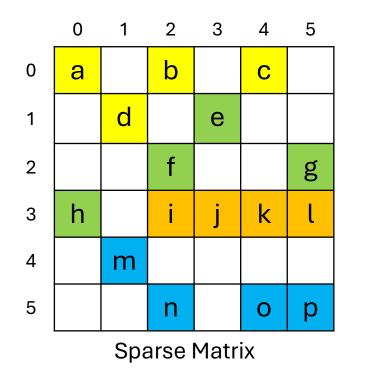

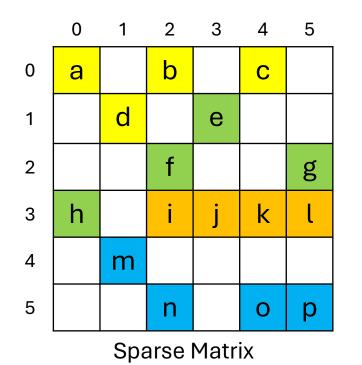

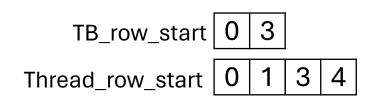

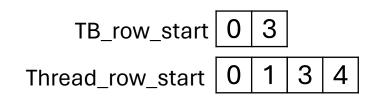

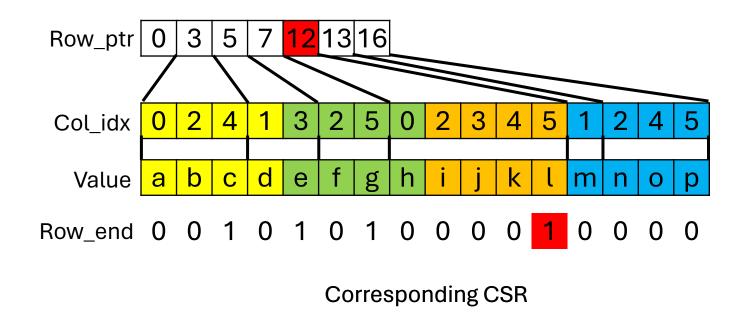

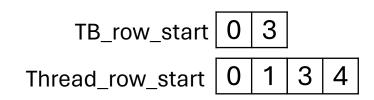

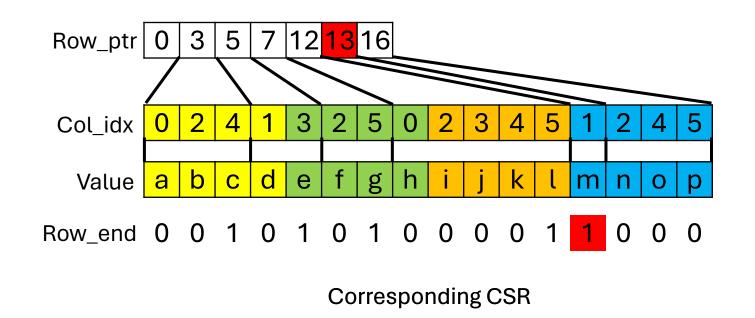

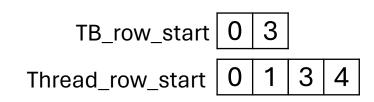

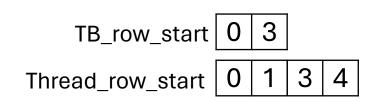

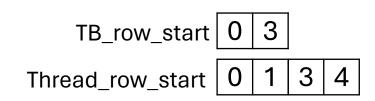

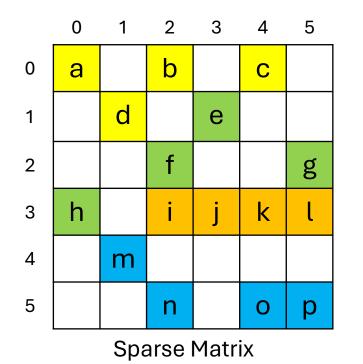

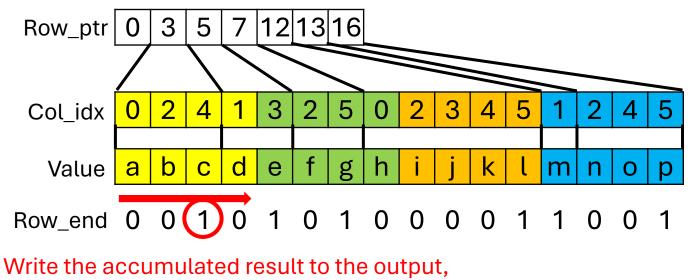

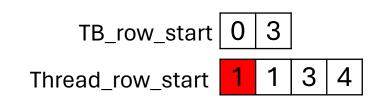

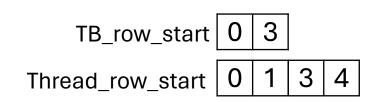

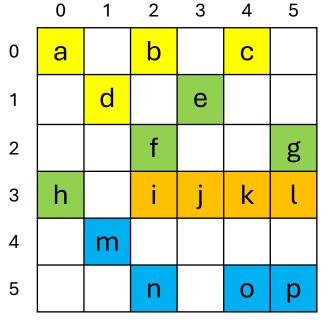

- Assuming one thread block consists of two threads, each thread is tasked with processing four nonzero entries of the sparse matrix.

Corresponding CSR

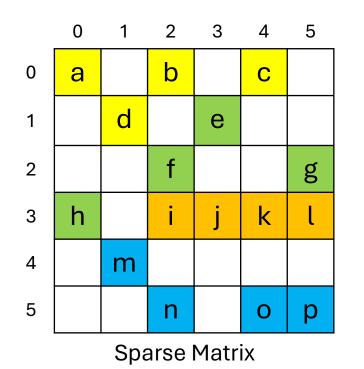

# **Strict Nonzero Splitting**

- Assuming one thread block consists of two threads, each thread is tasked with processing four nonzero entries of the sparse matrix.

and increment Thread\_row\_start by 1

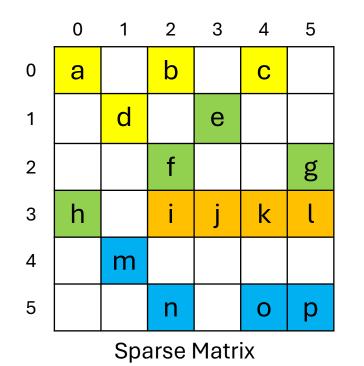

- Assuming one warp consists of four threads, each thread is tasked with processing four nonzero entries of the sparse matrix.

- Assuming one warp consists of four threads, each thread is tasked with processing four nonzero entries of the sparse matrix.

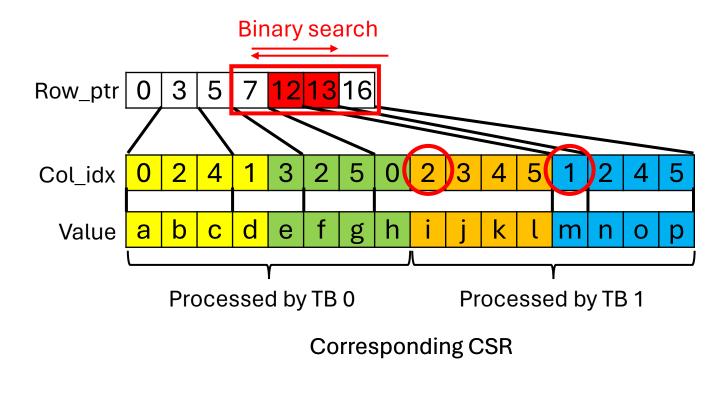

Sparse Matrix

- Assuming one warp consists of four threads, each thread is tasked with processing four nonzero entries of the sparse matrix.

Shared memory

- Assuming one warp consists of four threads, each thread is tasked with processing four nonzero entries of the sparse matrix.

Shared memory

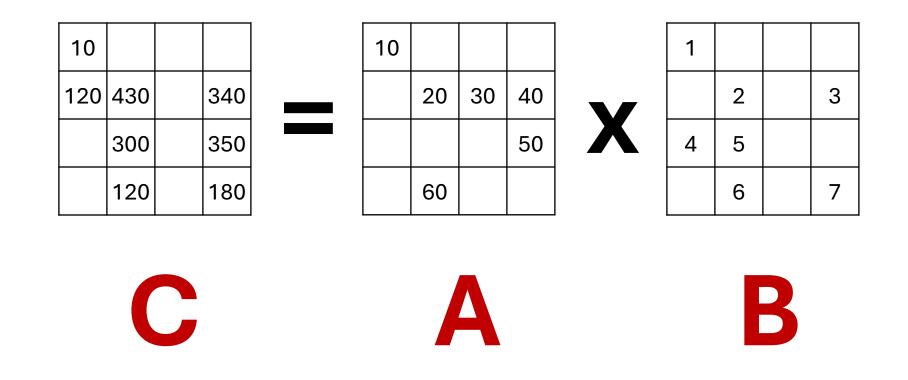

### What is SpGEMM?

In sparse matrix-matrix multiplication (SpGEMM), all three matrices are sparse

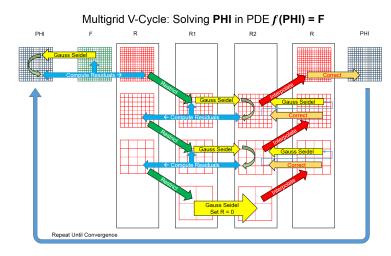

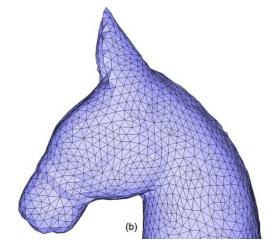

# **SpGEMM** is ubiquitous

Graph processing

Multigrid method

Mesh operation

\* https://www.datanami.com/2018/12/10/ graphit-promises-big-speedup-in-graph-processing/

\* https://en.wikipedia.org/wiki/Multigrid\_method

\* https://doc.cgal.org/latest/Polygon\_mesh\_processing/index.html

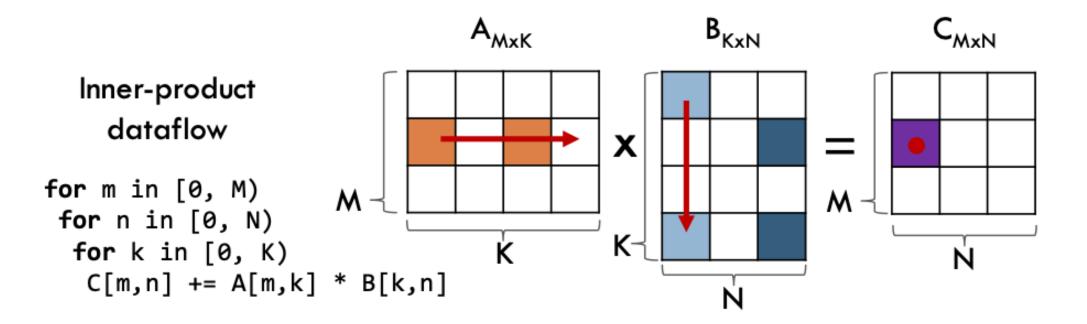

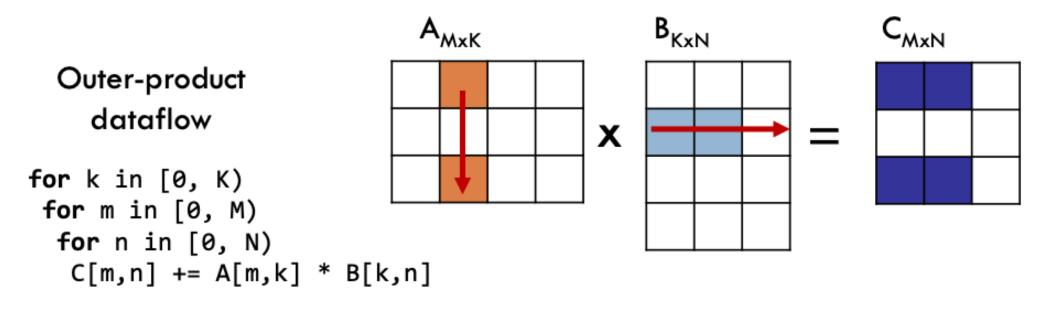

### **Three approaches for SpGEMM**

- Inner-product SpGEMM

- Outer-product SpGEMM

- Gustavson's SpGEMM

\* Zhang, Guowei, et al. "Gamma: Leveraging Gustavson's algorithm to accelerate sparse matrix multiplication." Proceedings of the 26th ACM International Conference on Architectural Support for Programming Languages and Operating Systems. 2021.<sup>44</sup>

# Inner-product SpGEMM

- Compute the output matrix one element at a time.

- Requiring the intersection between a row of A, and a column of B.

- Offers good output reuse, but poor input reuse.

- Asymptotically very inefficient

- For each row of A, an intersection operation is necessary for every nonzero column of B.

- But, most intersections will result in an empty set.

\* Zhang, Guowei, et al. "Gamma: Leveraging Gustavson's algorithm to accelerate sparse matrix multiplication." Proceedings of the 26th ACM International Conference on Architectural Support for Programming Languages and Operating Systems. 2021.<sup>45</sup>

# **Outer-product SpGEMM**

-

- Compute the output one partial matrix at a time by traversing each column of A and each row of B.

- Sums the outer products of corresponding columns and rows.

- Offers good input reuse, but poor output reuse.

- Unordered access across different rows and columns of the output matrix.

- The output is primarily required to be in GPU global memory due to poor locality.

- Global memory access for each partial product.

\* Zhang, Guowei, et al. "Gamma: Leveraging Gustavson's algorithm to accelerate sparse matrix multiplication." Proceedings of the 26th ACM International Conference on Architectural Support for Programming Languages and Operating Systems. 2021.<sup>46</sup>

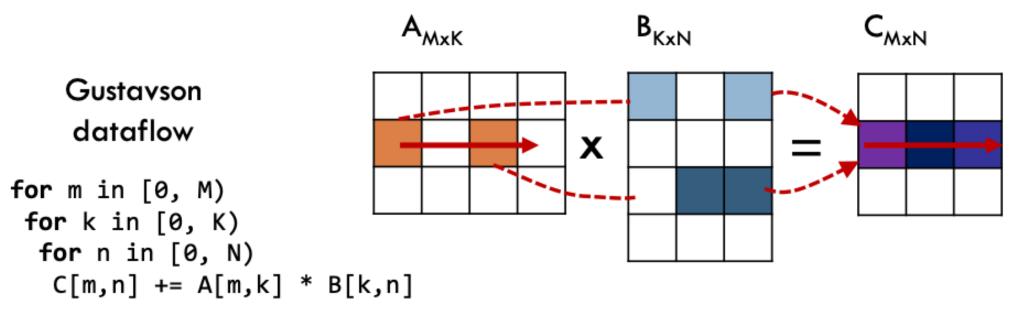

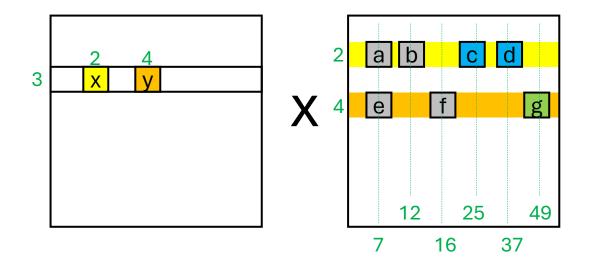

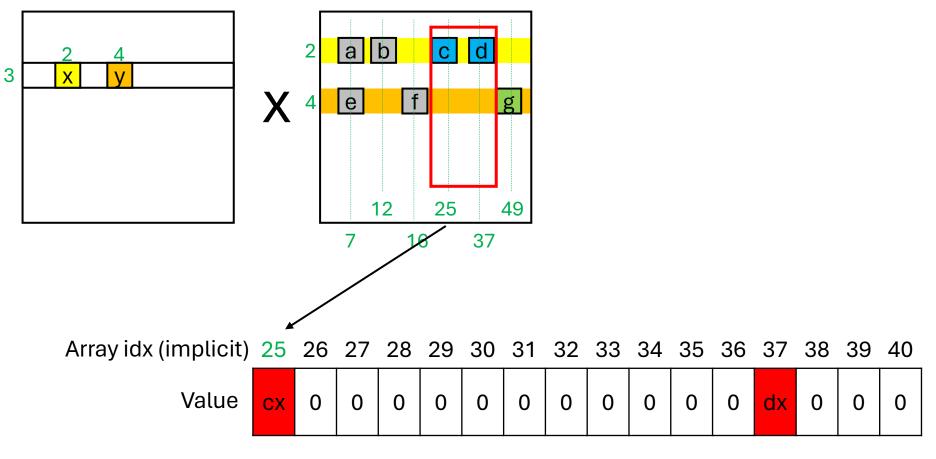

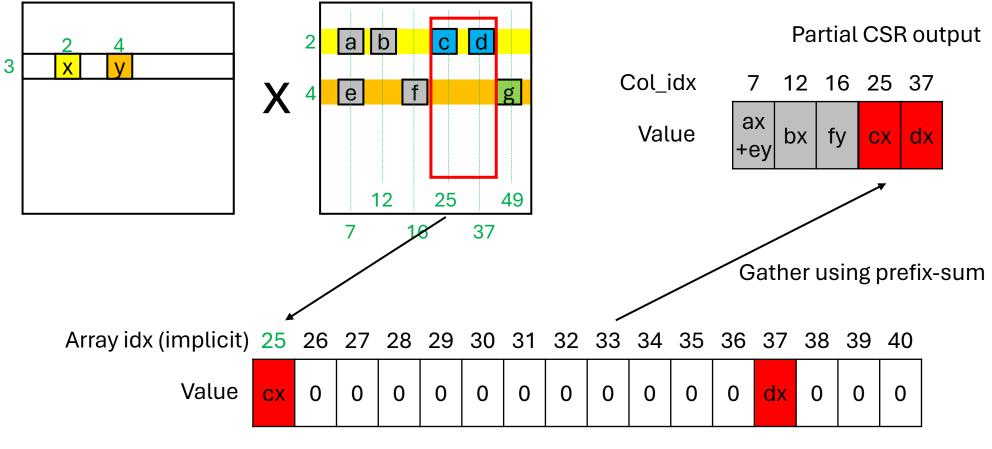

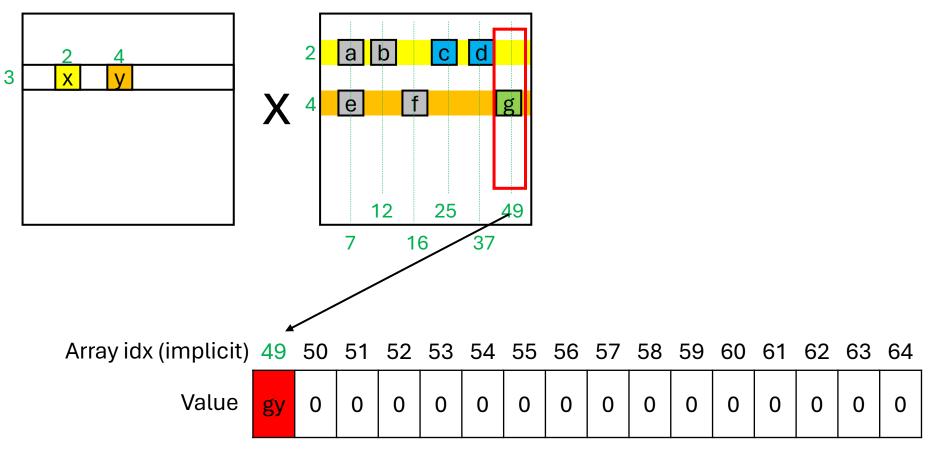

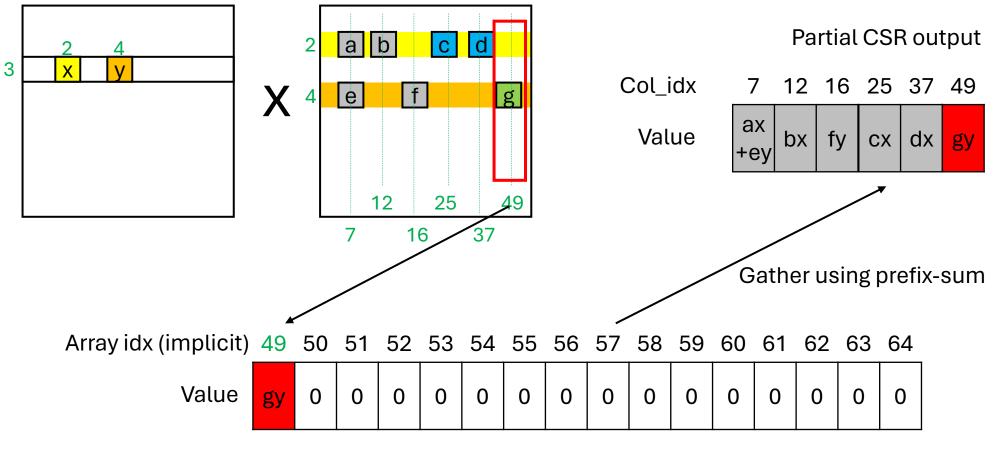

# **Gustavson's SpGEMM**

- Computes the output matrix one row at a time by summing the rows of B scaled by the corresponding columns in each row of A.

- Requires combining partial output rows instead of partial output matrices, as in outer-product SpGEMM.

- Modest reuse of input and output

- Allows for consistency in the format for both inputs and outputs, meaning all formats are CSR.

- Inner- or outer-product requires one input to be transposed (i.e., transposed CSR).

\* Zhang, Guowei, et al. "Gamma: Leveraging Gustavson's algorithm to accelerate sparse matrix multiplication." Proceedings of the 26th ACM International Conference on Architectural Support for Programming Languages and Operating Systems. 2021.<sup>47</sup>

### **Three approaches for SpGEMM**

- Inner-product SpGEMM

- Outer-product SpGEMM

- Gustavson's SpGEMM

Adopted in all state-of-the-art GPU implementations

\* Zhang, Guowei, et al. "Gamma: Leveraging Gustavson's algorithm to accelerate sparse matrix multiplication." Proceedings of the 26th ACM International Conference on Architectural Support for Programming Languages and Operating Systems. 2021.<sup>48</sup>

# **Optimizing SpGEMM on GPUs is challenging**

- Concurrent access of the output.

- The sparse output matrix needs to be constructed in parallel.

- The output size is unknown a priori.

- Accumulating partial products.

- Accumulating partial products in global memory significantly hurts performance.

- Causes uncoalesced atomic memory accesses.

- Load balancing.

- All matrices are irregular.

- Achieving load-balanced execution in SpGEMM is significantly more challenging compared to SpMV.

\* Parger, Mathias, et al. "Speck: Accelerating gpu sparse matrix-matrix multiplication through lightweight analysis." 49 Proceedings of the 25th ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming. 2020.

# **Optimizing SpGEMM on GPUs is challenging**

- Concurrent access of the output.

- The sparse output matrix needs to be constructed in parallel.

- The output size is unknown a priori.

- Accumulating partial products.

- Accumulating partial products in global memory significantly hurts performance.

- Causes uncoalesced atomic memory accesses.

- Load balancing.

- All matrices are irregular.

- Achieving load-balanced execution in SpGEMM is significantly more challenging compared to SpMV.

\* Parger, Mathias, et al. "Speck: Accelerating gpu sparse matrix-matrix multiplication through lightweight analysis." 50 Proceedings of the 25th ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming. 2020.

#### Methods for Memory Pre-allocation for the Output Matrix\*

- Progressive method

- Upper-bound method

- Probabilistic method

- Two-phase method (Precise method)

\* Liu, Weifeng, and Brian Vinter. "An efficient GPU general sparse matrix-matrix multiplication for irregular data." 2014, *28th International Parallel and Distributed Processing Symposium*. IEEE, 2014.

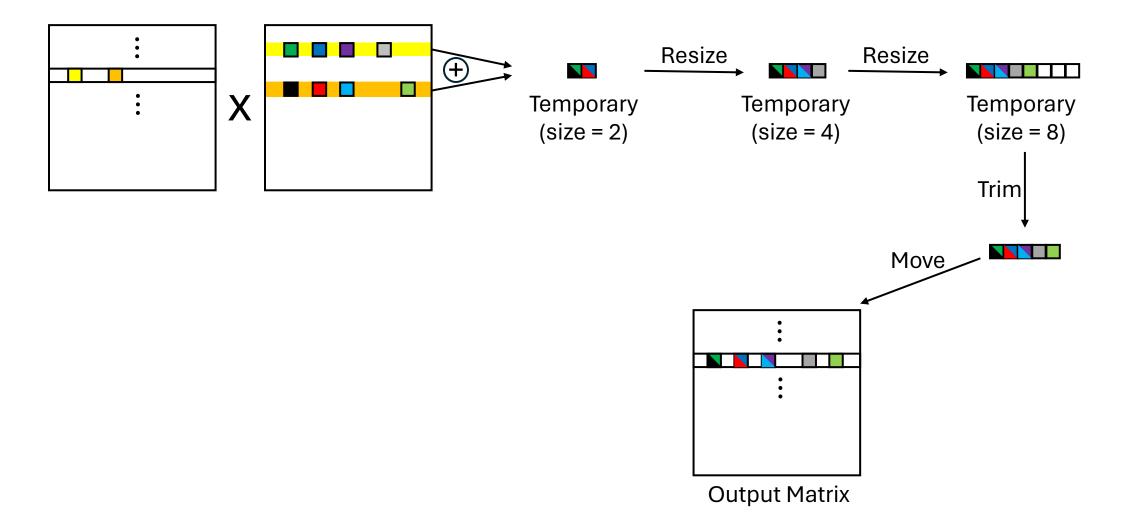

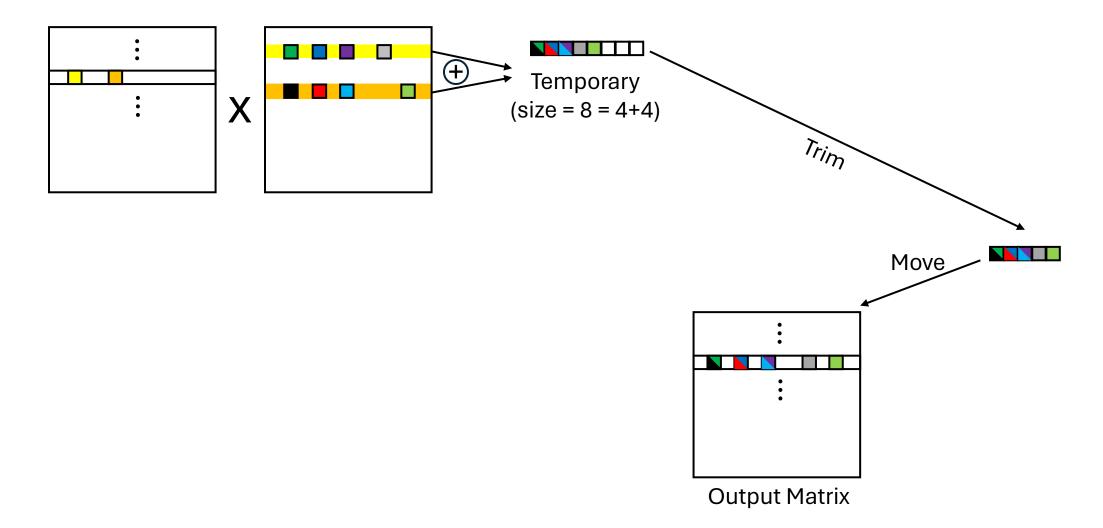

# **Progressive Method**

- First allocates memory of a proper size, starts sparse matrix computation and reallocates the buffer if larger space is required.

## **Progressive Method**

- First allocates memory of a proper size, starts sparse matrix computation and reallocates the buffer if larger space is required.

- Concurrent memory management over hundreds of thousands of threads is challenging.

- Reallocation of device memory on the fly during computations is difficult.

- Memory space is wasted up to k times (k is an expansion factor).

# **Upper-bound Method**

- Computes an upper bound of the number of the nonzero entries in the output matrix and allocates corresponding memory space.

# **Upper-bound Method**

- Computes an upper bound of the number of the nonzero entries in the output matrix and allocates corresponding memory space.

- Can significantly waste memory space

- The size of GPU memory is relatively small (e.g., 80GB for an A100 GPU)

- Memory bandwidth can be wasted

- GPU transaction granularity is 32/64 bytes

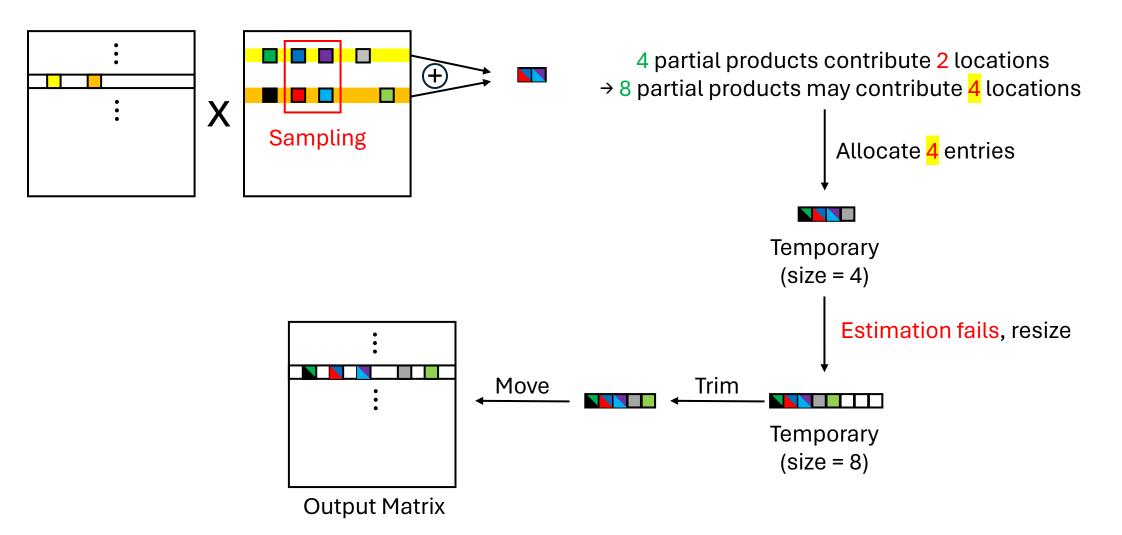

# **Probabilistic Method**

- Estimates an imprecise size of the output based on random sampling and probability analysis on the input matrices.

# **Probabilistic Method**

- Estimates an imprecise size of the output based on random sampling and probability analysis on the input matrices.

- Precisely estimating the upper bound of the output size is very challenging.

- Interactions between A and B are complicated: estimating which intermediate results contribute to the same entry of the output is difficult.

- Extra memory has to be allocated while the estimation fails.

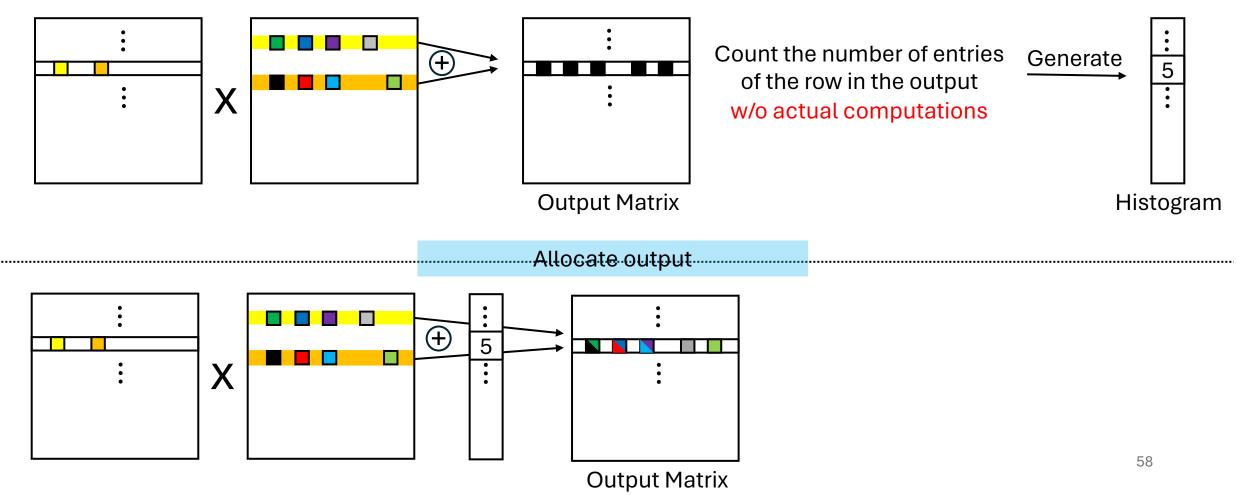

# Two-phase method

- In the symbolic phase, count the number of nonzero entries of each row of the output

- In the numeric phase, compute the column indices and values of the entries of the output

## Two-phase method

- In the symbolic phase, count the number of nonzero entries of each row of the output

- In the numeric phase, compute the column indices and values of the entries of the output

- The significant overhead arises from having the same pattern of computations twice.

- Memory-space efficiency is achieved, ensuring that memory space is not wasted.

- All state-of-the-art SpGEMM implementations on GPUs utilize this method.

#### **Progressive Method**

- Progressive method

- Upper-bound method

- Probabilistic method

- Two-phase method (Precise method)

Adopted in all state-of-the-art GPU implementations

\* Liu, Weifeng, and Brian Vinter. "An efficient GPU general sparse matrix-matrix multiplication for irregular data." 2014, IEEE 28th International Parallel and Distributed Processing Symposium. IEEE, 2014.

#### **Progressive Method**

- Progressive method

This may outperform the two-phase method on GPUs if we have enough GPU memory

- Upper-bound method

- Probabilistic method

- Two-phase method (Precise method)

Adopted in all state-of-the-art GPU implementations

\* Liu, Weifeng, and Brian Vinter. "An efficient GPU general sparse matrix-matrix multiplication for irregular data." 2014, [EEE 28th International Parallel and Distributed Processing Symposium. IEEE, 2014.

# **Optimizing SpGEMM on GPUs is challenging**

- Parallel assembly for the output.

- The sparse output matrix needs to be constructed in parallel.

- The output size is unknown a priori.

- Accumulating partial products.

- Accumulating partial products in global memory significantly hurts performance.

- Causes uncoalesced atomic memory accesses.

- Load balancing.

- All matrices are irregular.

- Achieving load-balanced execution in SpGEMM is significantly more challenging compared to SpMV.

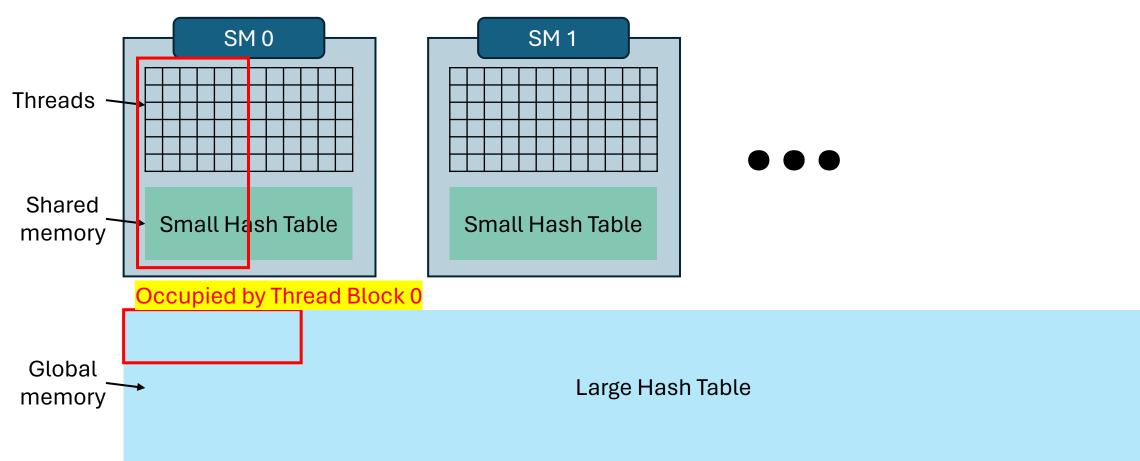

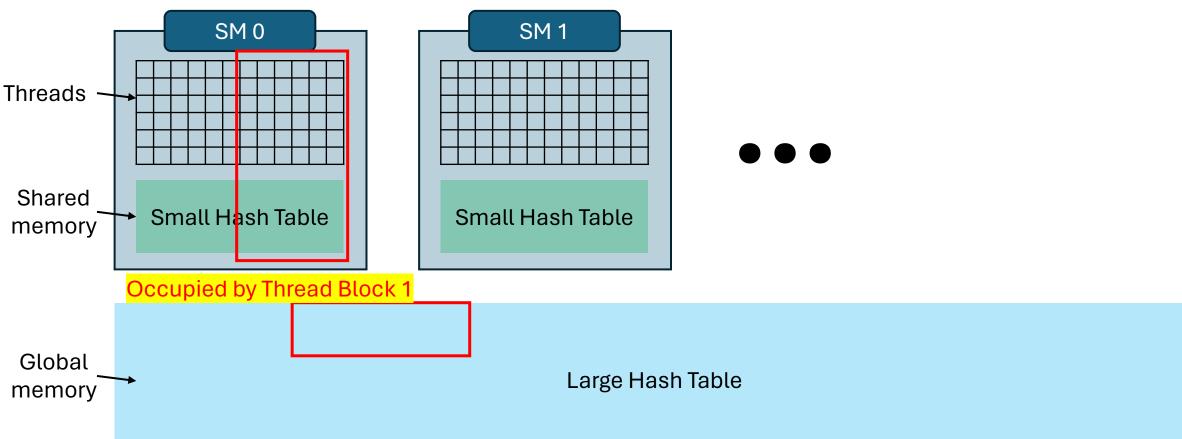

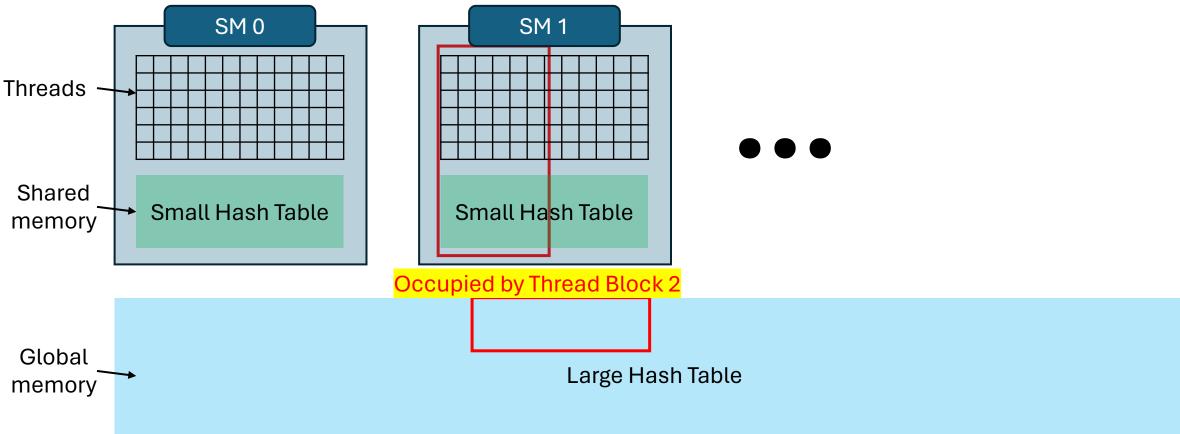

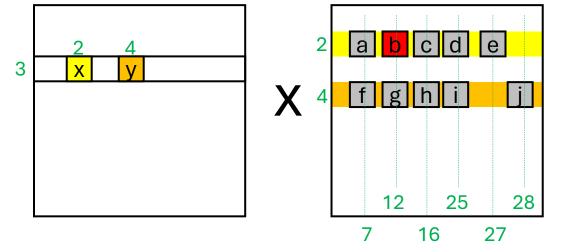

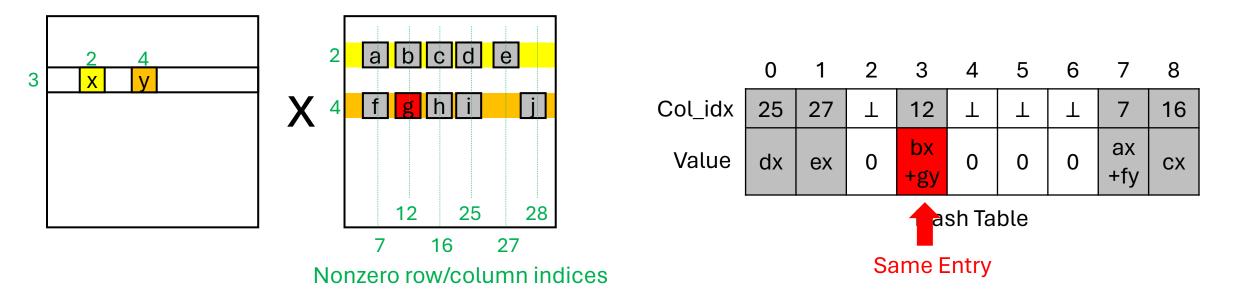

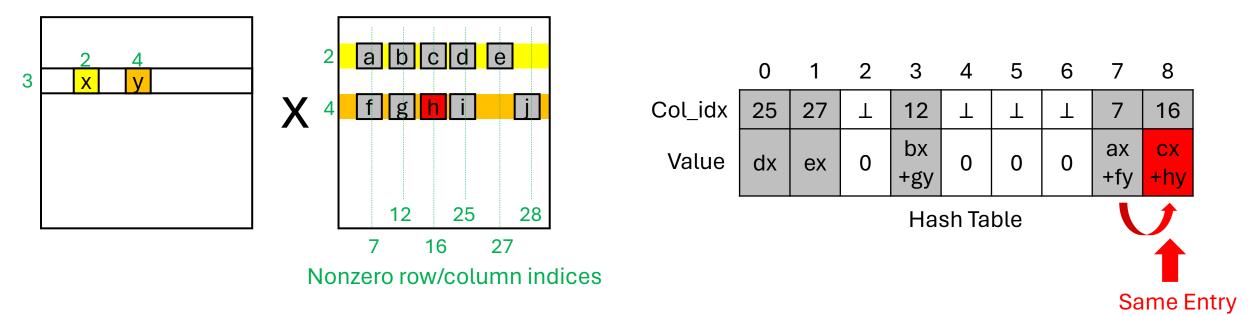

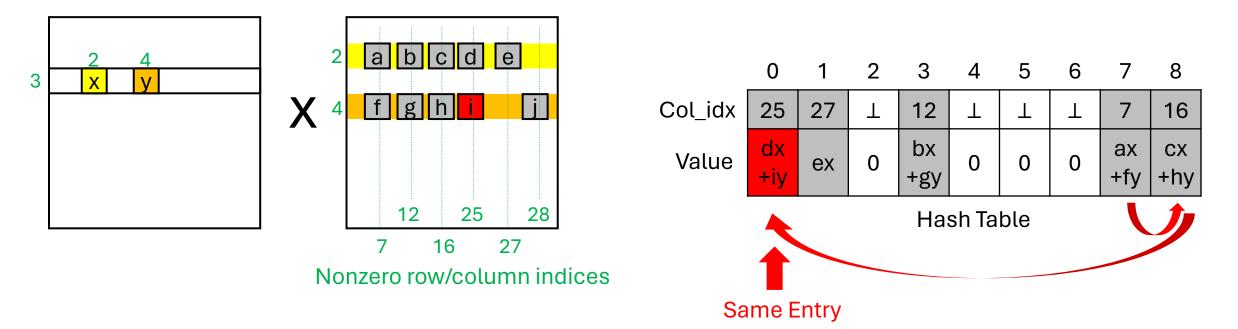

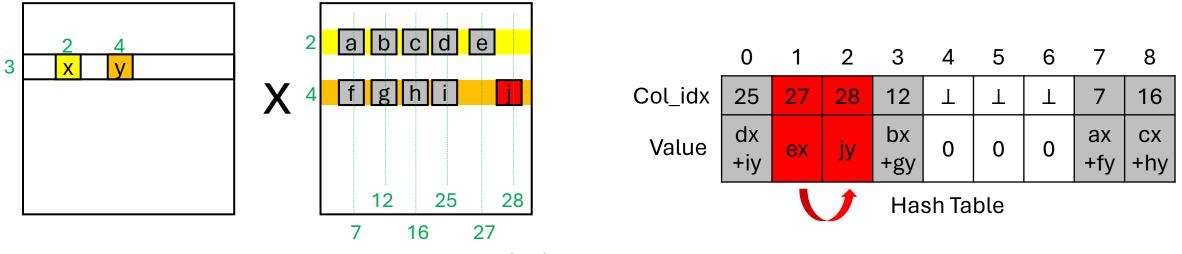

- For brevity, each thread block processes each row of the output matrix.

- Each thread block has two (hierarchical) hash tables in shared memory and global memory.

- Utilize a small hash table initially. If the small hash table is unable to contain all entries, transfer all data from the small hash table and rely solely on the large hash table.

- For brevity, each thread block processes each row of the output matrix.

- Each thread block has two (hierarchical) hash tables in shared memory and global memory.

- Utilize a small hash table initially. If the small hash table is unable to contain all entries, transfer all data from the small hash table and rely solely on the large hash table.

- For brevity, each thread block processes each row of the output matrix.

- Each thread block has two (hierarchical) hash tables in shared memory and global memory.

- Utilize a small hash table initially. If the small hash table is unable to contain all entries, transfer all data from the small hash table and rely solely on the large hash table.

- During the Symbolic phase, the number of nonzero entries in each row of the output remains unknown.

- Hash table size = the number of partial products (representing the upper bound).

- Store only the nonzero column indices in hash tables.

- In the Numeric phase, we gain knowledge about the number of nonzero entries in each output row.

- Hash table size =  $1.5 \times$  the number of nonzero entries.

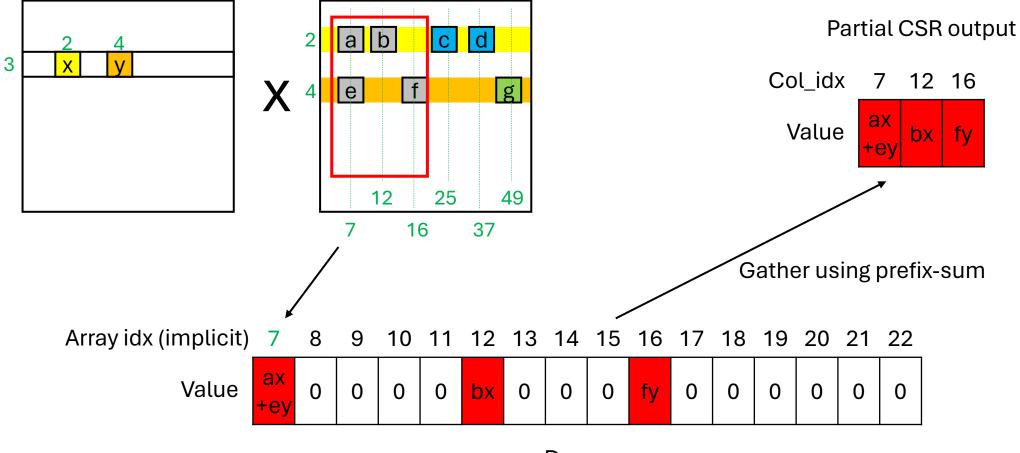

- Gathering nonzero entries of the hash table is achieved through parallel prefix-sum operations.

- Following the gathering process, sorting becomes necessary to arrange nonzero entries of an output row in ascending order of column indices.

- Store both the nonzero column indices and their corresponding values in hash tables.

- Need more space for hash tables

- Linear probing is used

-

-

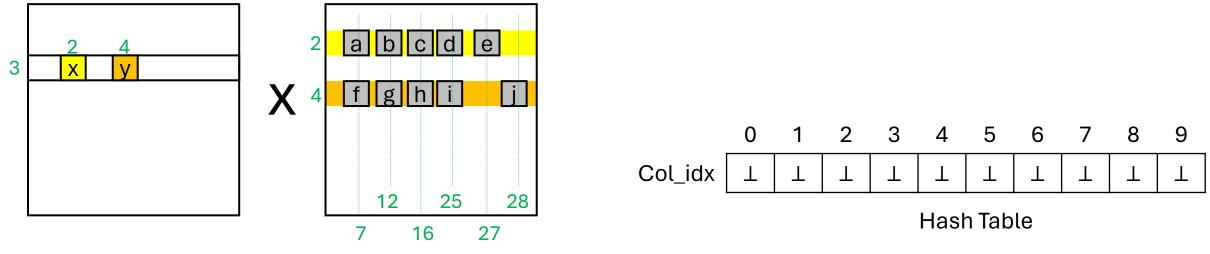

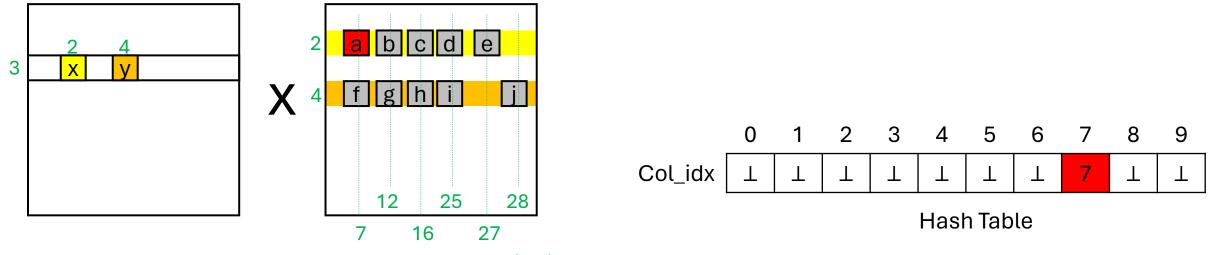

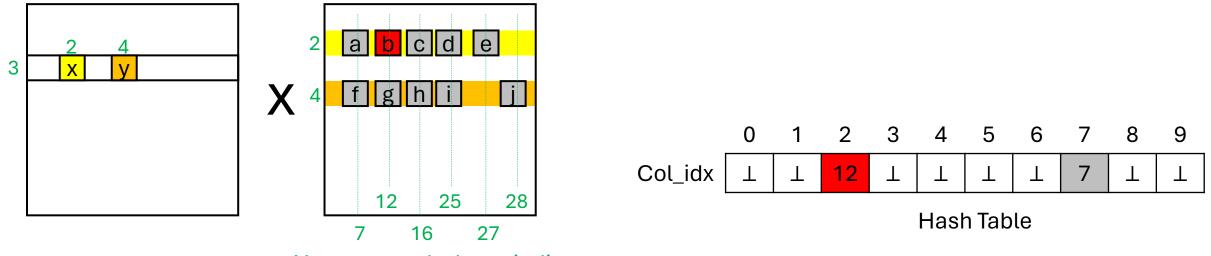

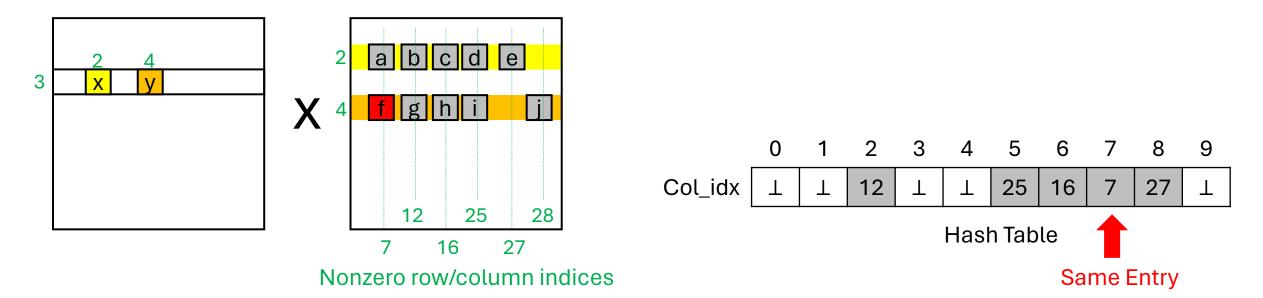

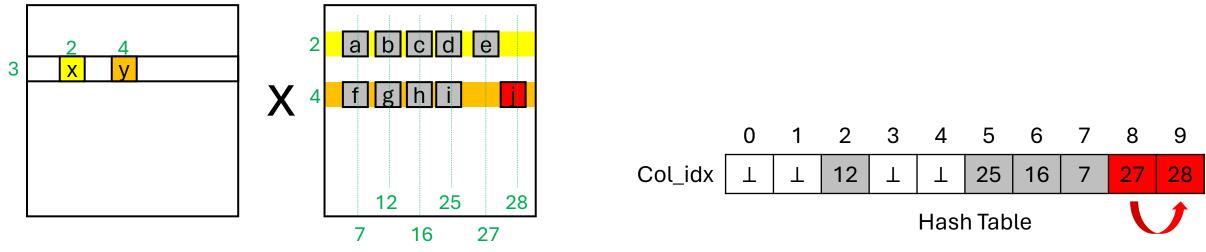

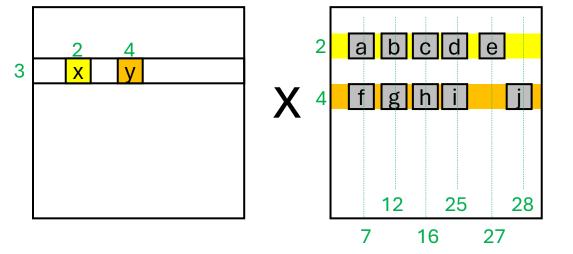

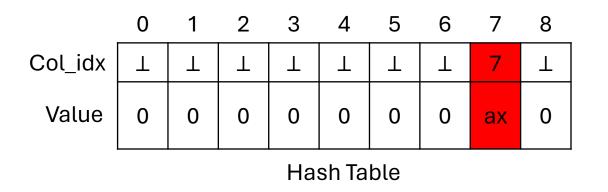

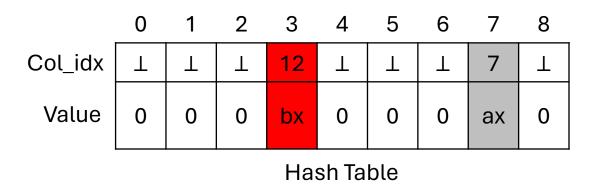

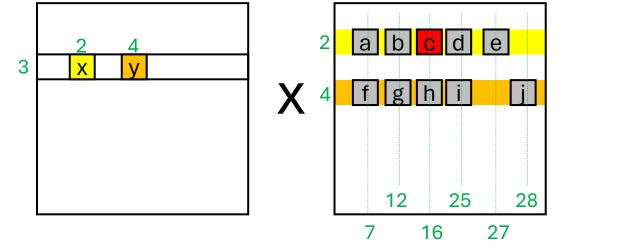

- In Symbolic phase,

- Hash table size = the number of partial products = 5+5 = 10

- Only maintain column indices

- Assume hash function h = (h+1)%10 in case of collisions.

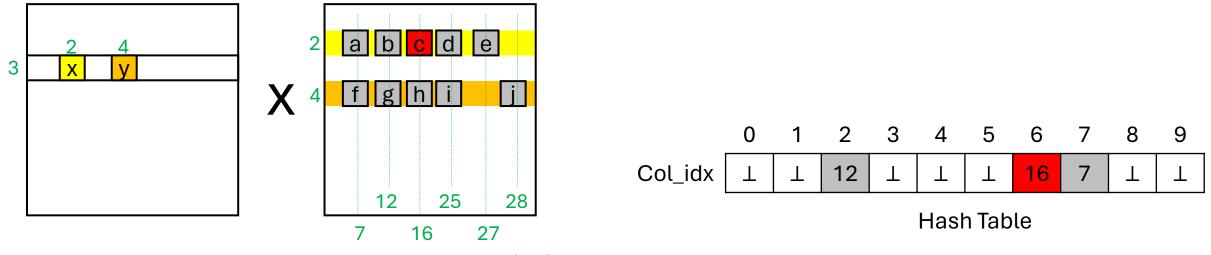

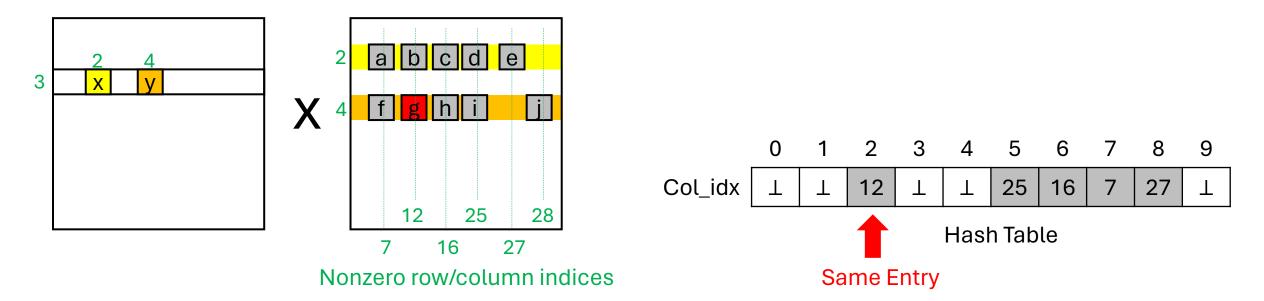

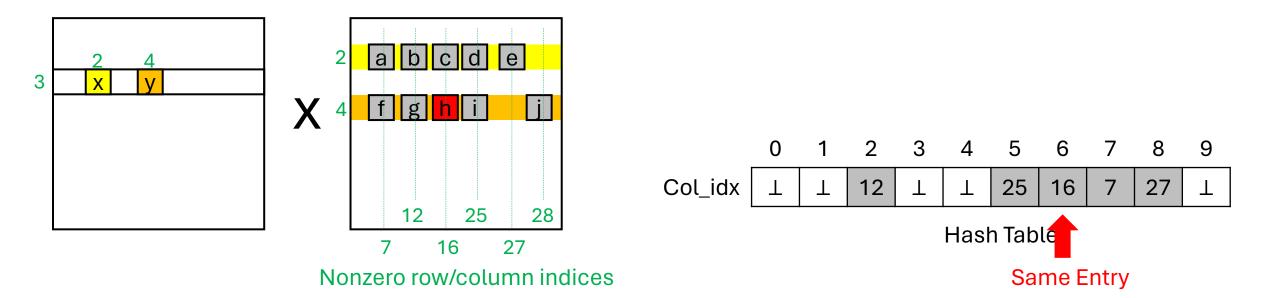

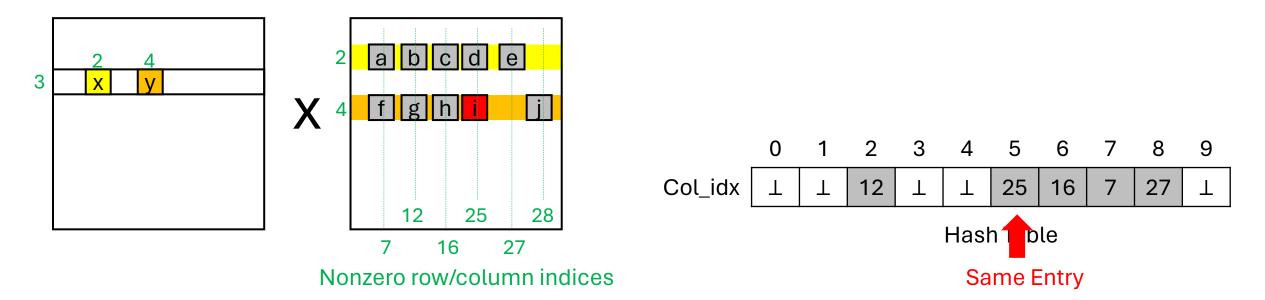

- In Symbolic phase,

- Hash table size = the number of partial products = 5+5 = 10

- Only maintain column indices

- Assume hash function h = (h+1)%10 in case of collisions.

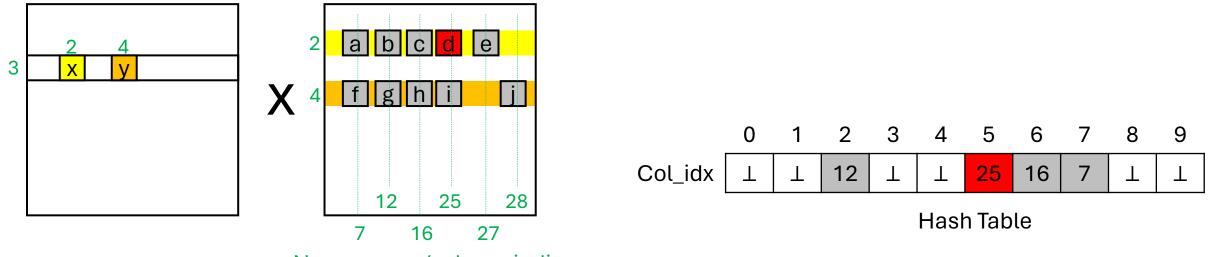

- In Symbolic phase,

- Hash table size = the number of partial products = 5+5 = 10

- Only maintain column indices

- Assume hash function h = (h+1)%10 in case of collisions.

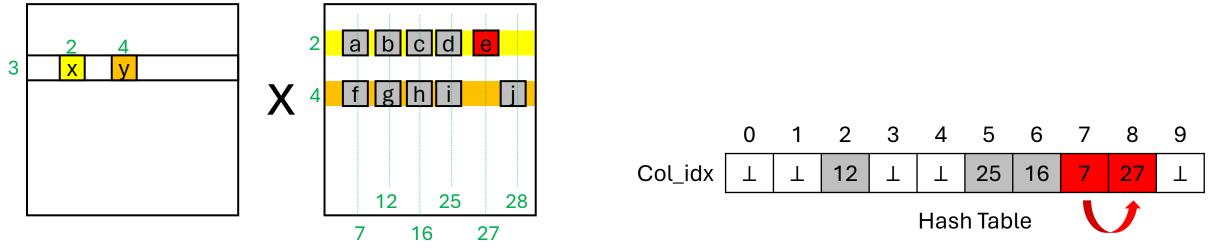

- In Symbolic phase,

- Hash table size = the number of partial products = 5+5 = 10

- Only maintain column indices

- Assume hash function h = (h+1)%10 in case of collisions.

- In Symbolic phase,

- Hash table size = the number of partial products = 5+5 = 10

- Only maintain column indices

- Assume hash function h = (h+1)%10 in case of collisions.

- In Symbolic phase,

- Hash table size = the number of partial products = 5+5 = 10

- Only maintain column indices

- Assume hash function h = (h+1)%10 in case of collisions.

- In Symbolic phase,

- Hash table size = the number of partial products = 5+5 = 10

- Only maintain column indices

- Assume hash function h = (h+1)%10 in case of collisions.

- In Symbolic phase,

- Hash table size = the number of partial products = 5+5 = 10

- Only maintain column indices

- Assume hash function h = (h+1)%10 in case of collisions.

- In Symbolic phase,

- Hash table size = the number of partial products = 5+5 = 10

- Only maintain column indices

- Assume hash function h = (h+1)%10 in case of collisions.

- In Symbolic phase,

- Hash table size = the number of partial products = 5+5 = 10

- Only maintain column indices

- Assume hash function h = (h+1)%10 in case of collisions.

- In Symbolic phase,

- Hash table size = the number of partial products = 5+5 = 10

- Only maintain column indices

- Assume hash function h = (h+1)%10 in case of collisions.

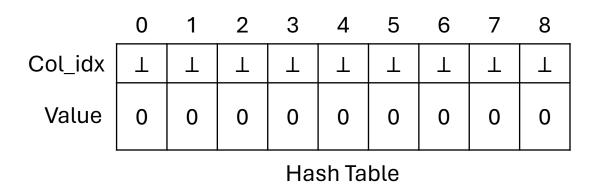

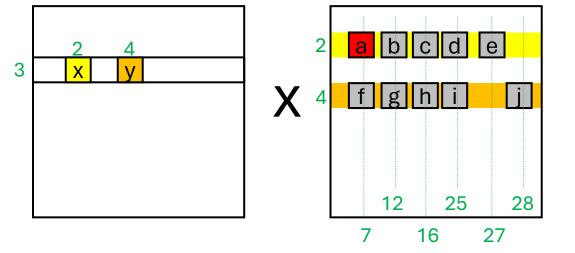

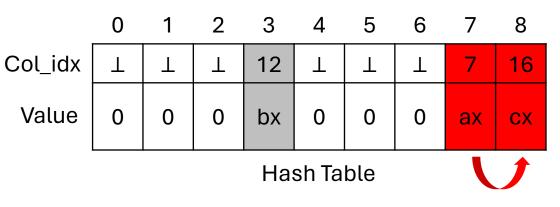

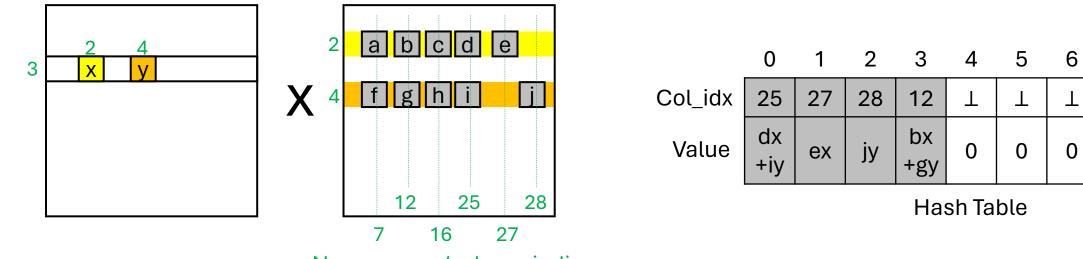

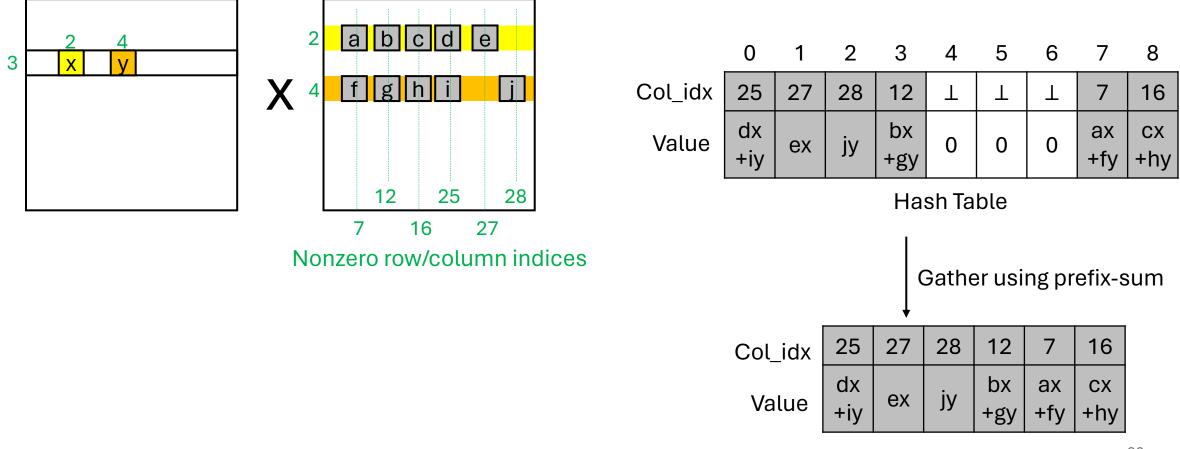

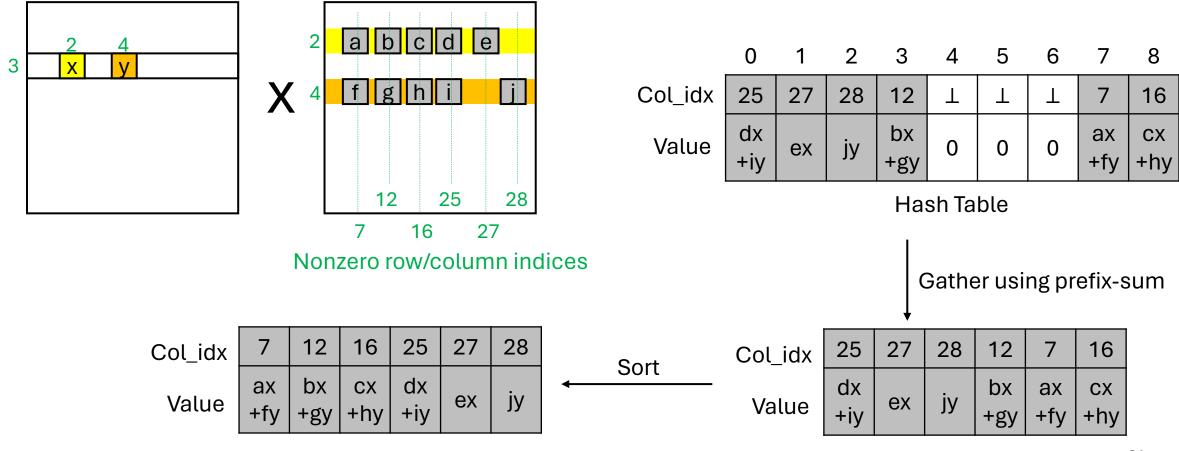

- In Numeric phase,

- Hash table size =  $1.5 \times$  the number of nonzero entries =  $1.5 \times 6 = 9$ .

- Maintain both column indices and corresponding values.

- Assume hash function h = (h+1)%9 in case of collisions.

- In Numeric phase,

- Hash table size =  $1.5 \times$  the number of nonzero entries =  $1.5 \times 6 = 9$ .

- Maintain both column indices and corresponding values.

- Assume hash function h = (h+1)%9 in case of collisions.

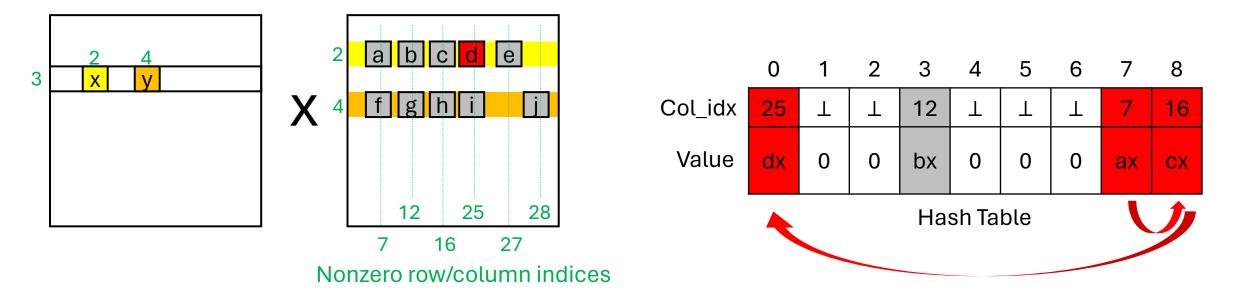

- In Numeric phase,

- Hash table size =  $1.5 \times$  the number of nonzero entries =  $1.5 \times 6 = 9$ .

- Maintain both column indices and corresponding values.

- Assume hash function h = (h+1)%9 in case of collisions.

- In Numeric phase,

- Hash table size =  $1.5 \times$  the number of nonzero entries =  $1.5 \times 6 = 9$ .

- Maintain both column indices and corresponding values.

- Assume hash function h = (h+1)%9 in case of collisions.

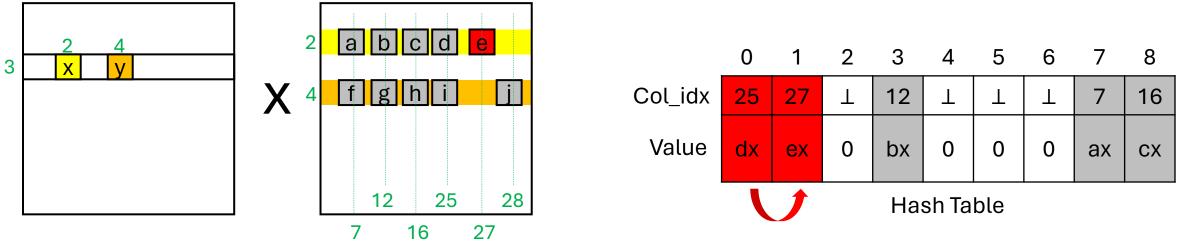

- In Numeric phase,

- Hash table size =  $1.5 \times$  the number of nonzero entries =  $1.5 \times 6 = 9$ .

- Maintain both column indices and corresponding values.

- Assume hash function h = (h+1)%9 in case of collisions.

- In Numeric phase,

- Hash table size =  $1.5 \times$  the number of nonzero entries =  $1.5 \times 6 = 9$ .

- Maintain both column indices and corresponding values.

- Assume hash function h = (h+1)%9 in case of collisions.

- In Numeric phase,

- Hash table size =  $1.5 \times$  the number of nonzero entries =  $1.5 \times 6 = 9$ .

- Maintain both column indices and corresponding values.

- Assume hash function h = (h+1)%9 in case of collisions.

- In Numeric phase,

- Hash table size =  $1.5 \times$  the number of nonzero entries =  $1.5 \times 6 = 9$ .

- Maintain both column indices and corresponding values.

- Assume hash function h = (h+1)%9 in case of collisions.

- In Numeric phase,

- Hash table size =  $1.5 \times$  the number of nonzero entries =  $1.5 \times 6 = 9$ .

- Maintain both column indices and corresponding values.

- Assume hash function h = (h+1)%9 in case of collisions.

- In Numeric phase,

- Hash table size =  $1.5 \times$  the number of nonzero entries =  $1.5 \times 6 = 9$ .

- Maintain both column indices and corresponding values.

- Assume hash function h = (h+1)%9 in case of collisions.

- In Numeric phase,

- Hash table size =  $1.5 \times$  the number of nonzero entries =  $1.5 \times 6 = 9$ .

- Maintain both column indices and corresponding values.

- Assume hash function h = (h+1)%9 in case of collisions.

- In Numeric phase,

- Hash table size =  $1.5 \times$  the number of nonzero entries =  $1.5 \times 6 = 9$ .

- Maintain both column indices and corresponding values.

- Assume hash function h = (h+1)%9 in case of collisions.

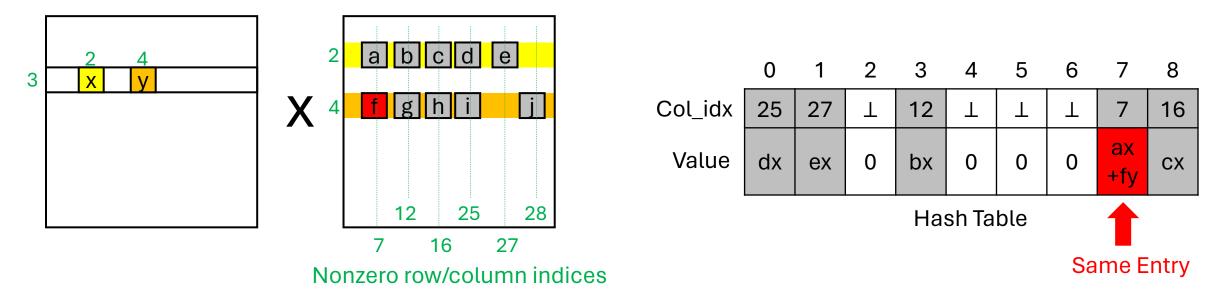

Nonzero row/column indices

7

7

ах

+fy

8

16

CX

+hy

- In Numeric phase,

- Hash table size =  $1.5 \times$  the number of nonzero entries =  $1.5 \times 6 = 9$ .

- Maintain both column indices and corresponding values.

- Assume hash function h = (h+1)%9 in case of collisions.

- In Numeric phase,

- Hash table size =  $1.5 \times$  the number of nonzero entries =  $1.5 \times 6 = 9$ .

- Maintain both column indices and corresponding values.

- Assume hash function h = (h+1)%9 in case of collisions.

Partial CSR output

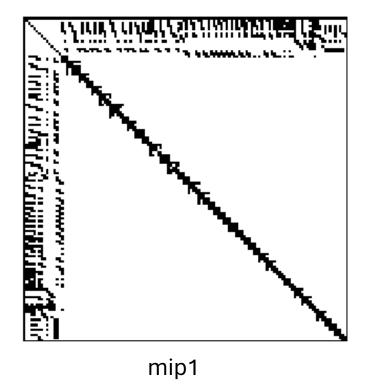

#### Many real-world sparse matrices are structured

- In many real-world sparse matrices, the nonzero entries are typically densely populated.

- Leveraging clustered entries is crucial for achieving high performance.

shipsec1

- Hashmaps incur overheads.

- Keeping track of nonzero column indices.

- Additional costs arise in the event of collision.

- Random access of the hash table, particularly problematic for hash tables in global memory.

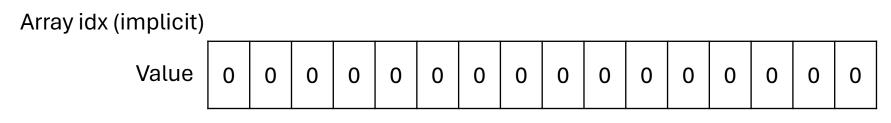

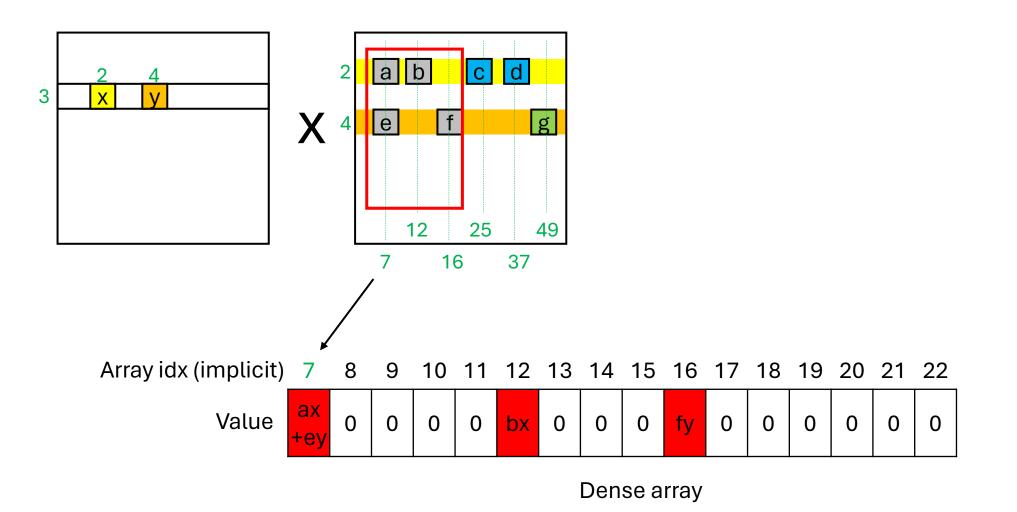

- When the nonzero entries of a row in the output are densely populated, a viable alternative is to use a dense array in shared memory.

- This approach eliminates the need for storing column indices and handling hash function collisions.

- It results in redundant memory space consumption.

- The use of a dense array is advantageous only when the entries within a row are densely populated.

- If the range from minimum to maximum column index in the resulting row does not fit in scratchpad memory, the dense accumulator needs multiple iterations on different column ranges, successively progressing through the output row.

- Need to store the positions of the last element that could be processed in the current iteration for each row.

- Assume the shared memory size is 16

- Assume the shared memory size is 16

- Assume the shared memory size is 16

- Assume the shared memory size is 16

- Assume the shared memory size is 16

- Assume the shared memory size is 16

- Assume the shared memory size is 16

## **Optimizing SpGEMM on GPUs is challenging**

- Parallel assembly for the output.

- The sparse output matrix needs to be constructed in parallel.

- The output size is unknown a priori.

- Accumulating partial products.

- Accumulating partial products in global memory significantly hurts performance.

- Causes uncoalesced atomic memory accesses.

- Load balancing.

- All matrices are irregular.

- Achieving load-balanced execution in SpGEMM is significantly more challenging compared to SpMV.

- Considering load-balanced execution across A and B (C = A X B) seems to be crucial.

- Assigning a predefined number of thread to each nonzero entry of A is insufficient.

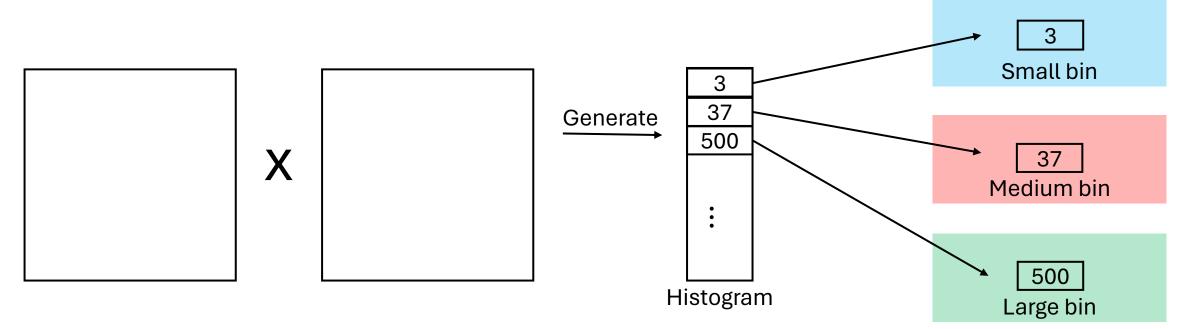

- Obtain the number of partial products for each row of the output

- Apply binning similar to SpMV's binning

- Small bin contains rows of the output with < 4 partial products

- Each thread processes each row in the small bin

- Medium bin contains rows of the output with < 128 partial products

- Each warp processes each row in the medium bin

- Large bin contains rows of the output with  $\geq$  128 partial products

- Each thread block processes each row in the large bin

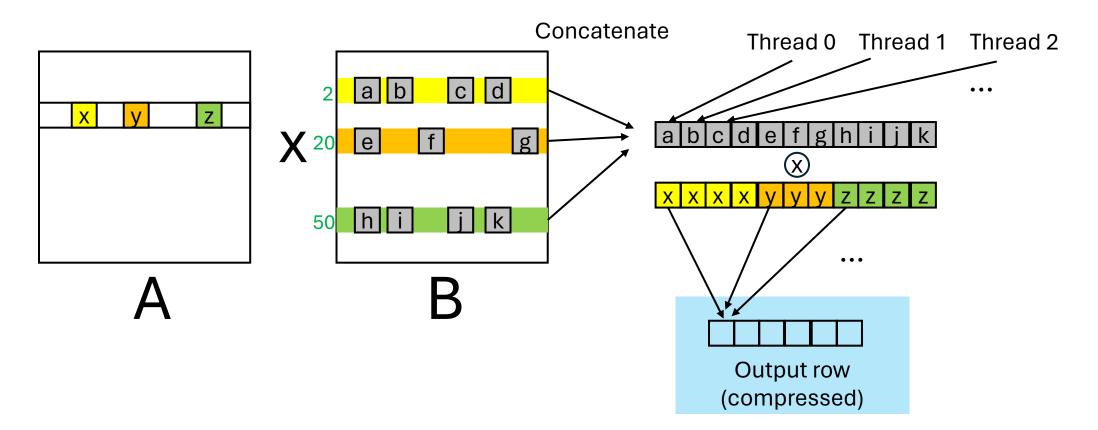

- Apply 'strict nonzero splitting' for each row of the input.

- Virtually concatenate rows of B corresponding to nonzero column indices of a row of A.

- Threads process each entry in the concatenated structure in a cyclic fashion.

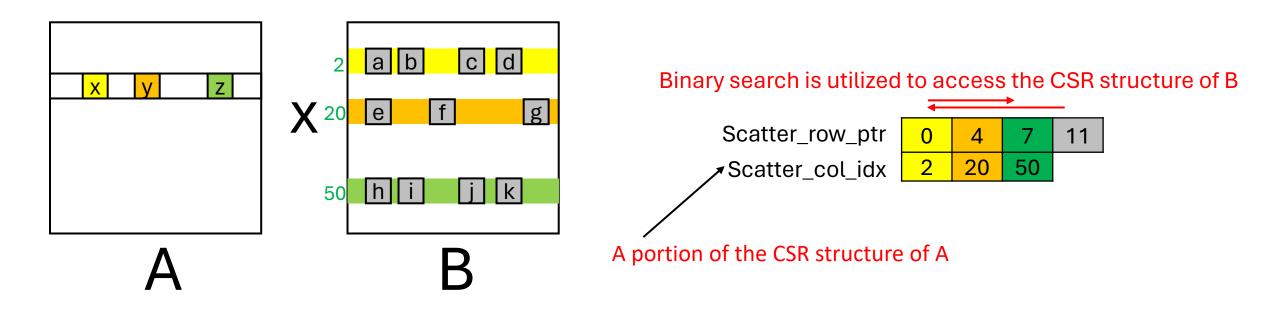

- Using binary search on the auxiliary arrays 'scatter\_row\_ptr' and 'scatter\_col\_idx' facilitates 'strict nonzero splitting' without actual concatenation.

- Actually, 'scatter\_col\_idx' is a partial 'col\_idx' of the original CSR for A.

# Questions?