# ENTRYBLEED

A Universal KASLR Bypass against KPTI on Linux

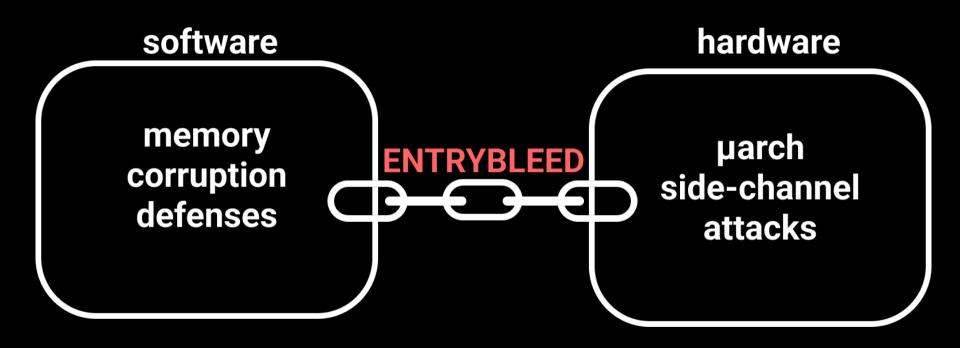

### Where does EntryBleed fit in?

#### hardware

µarch side-channel attacks

#### software

memory corruption defenses

#### hardware

µarch side-channel attacks

### Contributions

Reveal misconception in KPTI security

CVE-2022-4543: KASLR bypass on bare metal and VT-x

Provide root cause analyses

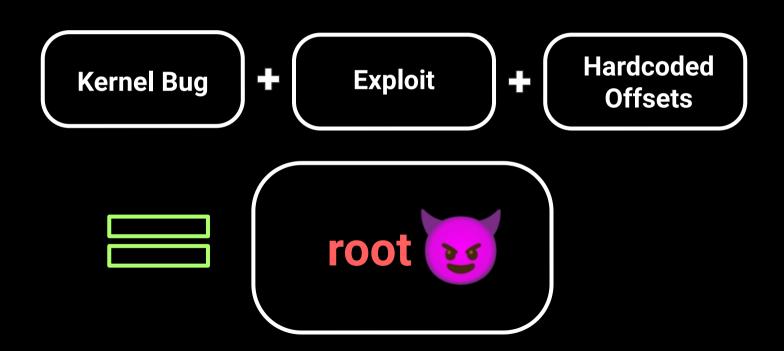

# Why should we care?

# Back in the old days...

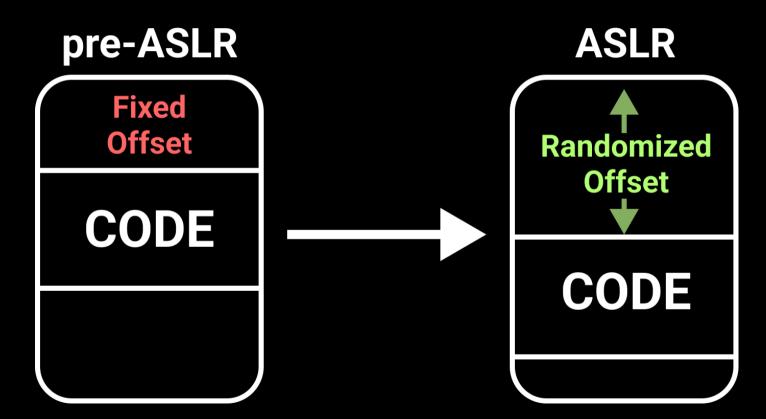

# **KASLR**

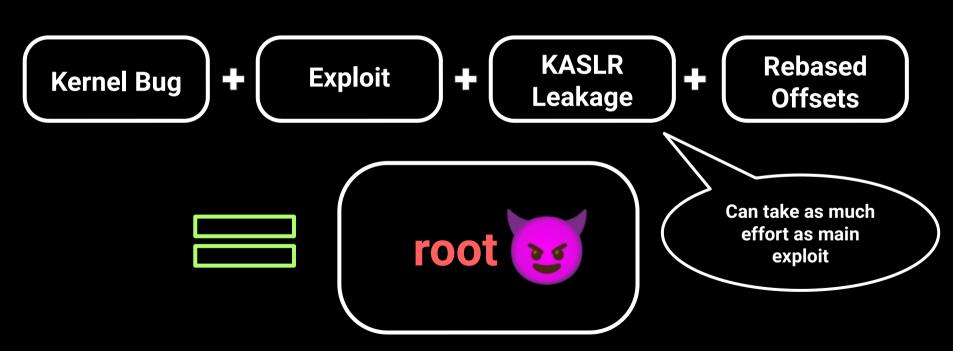

# With KASLR

# With KASLR

# With KASLR

# With EntryBleed

### Pre-Meltdown

• If a VA is invalid

- If a VA is invalid

- No ISA exceptions

- If a VA is invalid

- No ISA exceptions

- But takes longer

- If a VA is invalid

- No ISA exceptions

- But takes longer

side-channel vector

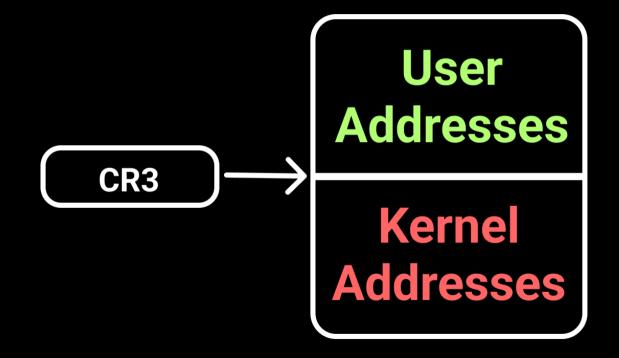

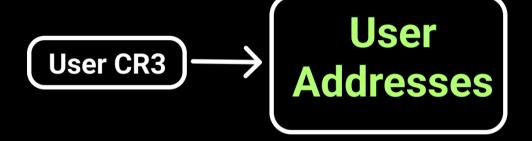

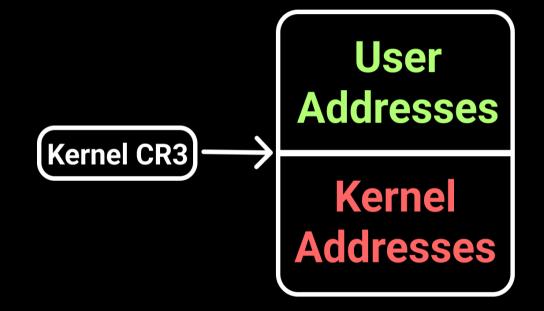

# **KPTI**

# **KPTI**

### Does the prefetch attack still work?

#### Prefetch vs. KPTI

#### Fetching the KASLR slide with prefetch

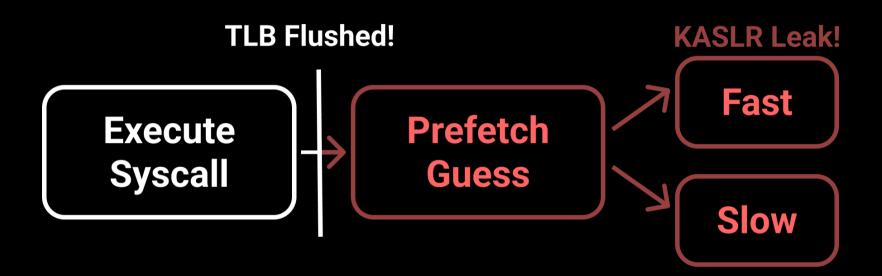

Upon reporting this bug to the Linux kernel security team, our suggestion was to start randomizing the location of the percpu cpu\_entry\_area (CEA), and consequently the associated exception and syscall entry stacks. This is an effective mitigation against remote attackers but is insufficient to prevent a local attacker from taking advantage. 6 years ago, Daniel Gruss et al. discovered a new more reliable technique for exploiting the TLB timing side channel in x86 CPU's. Their results demonstrated that prefetch instructions executed in user mode retired at statistically significant different latencies depending on whether the requested virtual address to be prefetched was mapped vs unmapped, even if that virtual address was only mapped in kernel mode. kPTI was helpful in mitigating this side channel however, most modern CPUs now have innate protection for Meltdown, which kPTI was specifically designed to address, and thusly kPTI (which has significant performance implications) is disabled on modern microarchitectures. That decision means it is once again possible to take advantage of the prefetch side channel to defeat not only KASLR, but also the CPU entry area randomization mitigation, preserving the viability of the CEA stack corruption exploit technique against modern X86 CPUs.

There are surprisingly few fast and reliable examples of this prefetch KASLR bypass technique available in the open source realm, so I made the decision to write one.

#### Prefetch vs. KPTI

#### Fetching the KASLR slide with prefetch

Upon reporting this bug to the Linux kernel security team, our suggestion was to start randomizing the location of the percpu cpu\_entry\_area (CEA), and consequently the associated exception and syscall entry stacks. This is an effective mitigation against remote attackers but is insufficient to prevent a local attacker from taking advantage. 6 years ago, Daniel Gruss et al. discovered a new more reliable technique for exploi executed kPTI was helpful in mitigating this side channel mapped in kernel mode. kPTI was helpful in mitigating this side channel however, most modern CPUs now have innate protection for Meltdown, which kPTI was specifically designed to address, and thusly kPTI (which has significant performance implications) is disabled on modern microarchitectures. That decision means it is once again possible to take advantage of the prefetch side channel to defeat not only KASLR, but also the CPU entry area randomization mitigation, preserving the viability of the CEA stack corruption exploit technique against modern X86 CPUs.

There are surprisingly few fast and reliable examples of this prefetch KASLR bypass technique available in the open source realm, so I made the decision to write one.

# But...

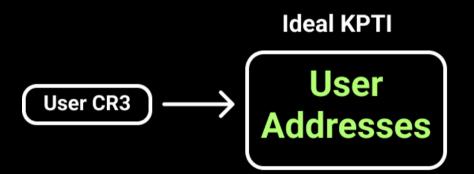

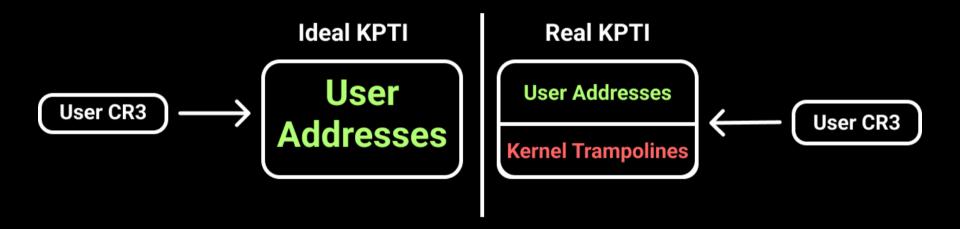

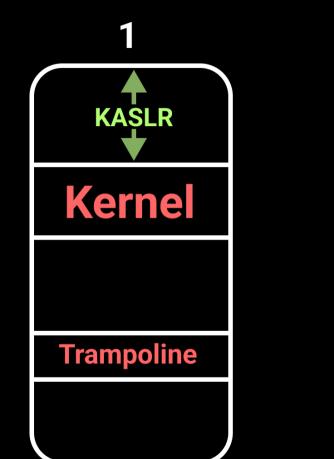

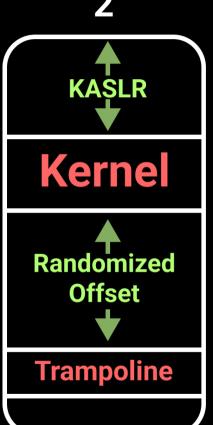

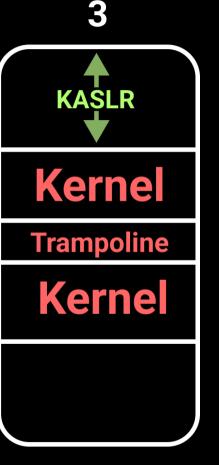

# **Isolation Flaw in KPTI**

#### **Isolation Flaw in KPTI**

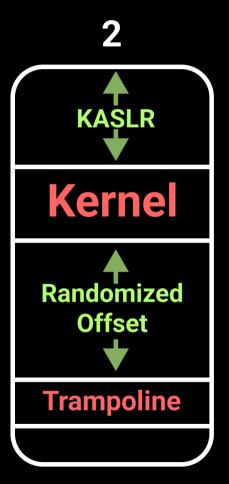

#### What VA is reasonable for this mapping?

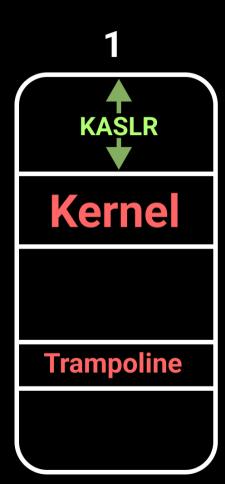

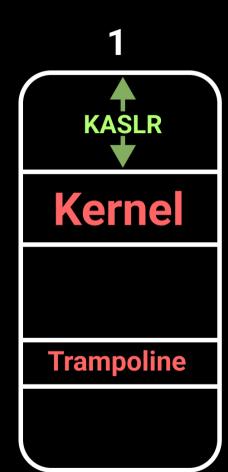

#### Kernel

**Trampoline**

Kernel

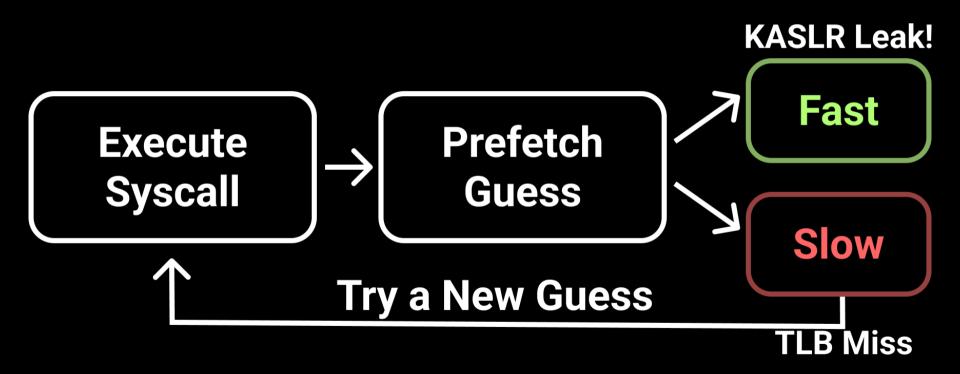

# **Attack Strategy**

# **Attack Strategy**

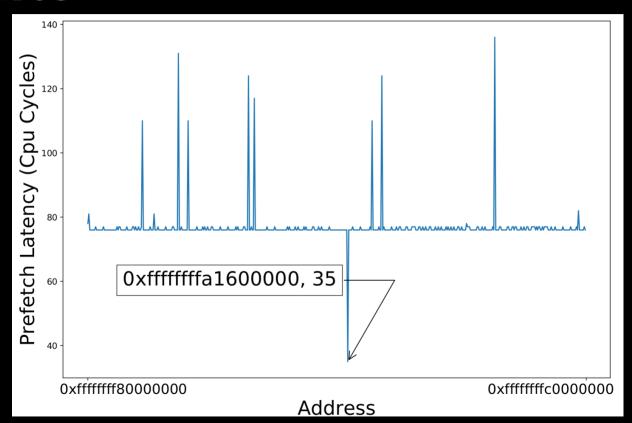

- Bruteforce range

- Start: 0xfffffff80000000

- End: 0xfffffffc0000000

- Increment by 2MB

# Results

# Results

| CPU Model               | Kernel Version | Average Leakage<br>Time (s) | Accuracy Rate |

|-------------------------|----------------|-----------------------------|---------------|

| Intel i5-4590           | 5.4.0-146      | 0.2236                      | 100%          |

| Intel i7-7950H          | 5.15.0-83      | 0.2761                      | 99.7%         |

| Intel i7-6700           | 5.15.0-67      | 0.1334                      | 99.6%         |

| Intel i7-7950H<br>(KVM) | 5.15.0-58      | 0.4148                      | 99.9%         |

#### **DEMO**

#### **USER**

#### **ROOT**

test@arch-sec-xss:~\$ root@arch-sec-xss:/home/test# 0:bash\* "arch-sec-xss.csail.mi" 14:04 20-0ct-23 How can prefetch work after address space switch?

```

syscall_return_via_sysret:

199

IBRS EXIT

200

POP REGS pop rdi=0

201

202

203

* Now all regs are restored except RSP and RDI.

* Save old stack pointer and switch to trampoline stack.

204

*/

movq

%rsp, %rdi

PER_CPU_VAR(cpu tss rw + TSS sp0), %rsp

movq

208

UNWIND_HINT_END_OF_STACK

209

RSP-RDI(%rdi)

210

pusha

/* RSP */

211

(%rdi)

/* RDI */

pushq

212

213

* We are on the trampoline stack. All regs except RDI are live.

214

* We can do future final exit work right here.

215

216

217

STACKLEAK ERASE NOCLOBBER

218

SWITCH_TO_USER_CR3_STACK_scratch_reg=%rdi

219

220

221

%rdi

DODQ

popq

%rsp

223

SYM_INNER_LABEL(entry_SYSRETO_unsafe_stack, SYM_L_GLOBAL)

224

ANNOTATE_NOENDBR

225

swapgs

226

sysreta

227

SYM_INNER_LABEL(entry_SYSRETQ_end, SYM_L_GLOBAL)

228

ANNOTATE_NOENDBR

229

int3

230

SYM_CODE_END(entry_SYSCALL_64)

```

#### syscall\_return\_via\_sysret:

```

IBRS EXIT

POP REGS pop rdi=0

* Now all reas are restored except RSP and RDI.

* Save old stack pointer and switch to trampoline stack.

%rsp, %rdi

pvom

PER_CPU_VAR(cpu tss rw # TSS sp0), %rsp

pvom

UNWIND HINT END OF STACK

pushq RSP-RDI(%rdi)

/* RSP */

pushq (%rdi)

/* RDI */

* We are on the trampoline stack. All regs except RDI are live.

* We can do future final exit work right here.

STACKLEAK ERASE NOCLOBBER

SWITCH_TO_USER_CR3_STACK_scratch_reg=%rdi

%rdi

popq

%FSD

SYM_INNER_LABEL(entry_SYSRETO_unsafe_stack, SYM_L_GLOBAL)

ANNOTATE_NOENDBR

swapgs

sysreta

SYM_INNER_LABEL(entry_SYSRETQ_end, SYM_L_GLOBAL)

ANNOTATE_NOENDBR

int3

SYM_CODE_END(entry_SYSCALL_64)

```

```

syscall_return_via_sysret:

IBRS EXIT

POP REGS pop rdi=0

* Now all reas are restored except RSP and RDI.

* Save old stack pointer and switch to trampoline stack.

%rsp, %rdi

pvom

PER_CPU_VAR(cpu tss rw # TSS sp0), %rsp

pvom

UNWIND HINT END OF STACK

pushq RSP-RDI(%rdi)

/* RSP */

pushq (%rdi)

/* RDI */

* We are on the trampoline stack. All regs except RDI are live.

* We can do future final exit work right here.

STACKLEAK FRASE NOCLOBBER

SWITCH_TO_USER_CR3_STACK scratch_reg=%rdi

%rdi

DODG

%гѕр

popq

SYM_INNER_LABEL(entry_SYSRETQ_unsafe_stack, SYM_L_GLOBAL)

ANNOTATE_NOENDBR

swapgs

sysreta

SYM_INNER_LABEL(entry_SYSRETQ_end, SYM_L_GLOBAL)

ANNOTATE_NOENDBR

int3

```

SYM\_CODE\_END(entry\_SYSCALL\_64)

```

syscall_return_via_sysret:

IBRS EXIT

POP REGS pop rdi=0

* Now all reas are restored except RSP and RDI.

* Save old stack pointer and switch to trampoline stack.

%rsp, %rdi

pvom

PER_CPU_VAR(cpu_tss_rw # TSS_sp0), %rsp

movq

UNWIND HINT END OF STACK

pushq RSP-RDI(%rdi)

/* RSP */

pushq (%rdi)

/* RDI */

* We are on the trampoline stack. All regs except RDI are live.

* We can do future final exit work right here.

STACKLEAK_ERASE_NOCLOBBER

SWITCH_TO_USER_CR3_STACK scratch_reg=%rdi

%rdi

DODG

%rsp

popq

SYM_INNER_LABEL(entry_SYSRETQ_unsafe_stack, SYM_L_GLOBAL)

ANNOTATE_NOENDBR

Sysretq Lend, SYM_L_GLOBAL)

int3

SYM_CODE_END(entry_SYSCALL_64)

```

arch/x86/entry\_64.S, entry\_syscall\_64, v6.5.9

# **Attacking Guest OS**

How does side-channel fare under VM exits?

#### Read the paper!

Effects of VM MMU Optimizations

Fully Working POC

Mitigation Proposal

EntryBleed against VM Exits

**More Data**

• KPTI is insufficient against prefetch

- KPTI is insufficient against prefetch

- An unpatched Linux KASLR bypass on Intel

- KPTI is insufficient against prefetch

- An unpatched Linux KASLR bypass on Intel

- Lowers exploitation difficulty

willsroot.io

compute. collaborate. create.

**Questions?**

will@willsroot.io