MULTICS SYSTEM-PROGRAMMERS MANUAL

SECTION BC.4.01 PAGE 1

Published: 06/30/67 (Supersedes: BC.4.01, 10/21/66; BC.4.01, 04/14/67)

## Identification

System Initialization and Bootload A. Bensoussan

### Purpose

This document describes the system initialization and bootload procedure for GE 645 system.

"Initialize" and "Initialize and Bootload" functions are provided using two distinct pushbuttons.

The Initialize function will place all of the active and passive units of the system in an initial state. The peripherals are not affected.

The bootload function initializes the system and then loads a program, stored in the GIOC hardware, into core memory. The processor executes the bootload program, which is designed to read a tape written in the Multics standard format; it reads the beginning of the tape and transfers to a conventional location.

## Initialize

Fressing the Initialize Button causes the following sequence:

- 1. A logic signal is sent from GIOC to all Memory Controllers

- 2. The Memory Controllers will Initialize the controller Send an initial signal to all ports

- 3. All active units will reset their control logic to an initial state

Memory Controllers: All Interrupt Cells reset No memory cycle or request existing The masks are set so that all interrupts are allowed.

Processors : All fault conditions reset DIS instruction in CPU (wait for interrupt)

GIOC

: All adapters reset No channel service requests existing

Drum

: Controller in disconnected state

#### Bootload

The bootload is activated by a single pushbutton. One of the 2 GIOC peripheral adapter channels implemented within the bootload as the loader program channel must have been preselected by a panel switch in the bootload GIOC controller cabinet.

The GIOC contains a Bootload channel with a fixed store memory from which 64 words are transferred into selected locations in core. The bootload channel is part of the controller and operates as a <u>direct</u> channel; no channel number is assigned and no command can be issued to it; the channel is only activated by depressing the bootload button.

#### Before pushing the bootload button.

A certain number of switches have to be set before pushing the bootload button, so that the hardware assumptions made by the bootload program are respected.

1. GIOC base address Go

The GIOC has an 18 bit panel switch to determine the base address Go of the GIOC mailboxes. Setting this address defines the memory controller that is "control memory" for this GIOC. Let m be the number associated with this memory controller (m = 1, 2, 3, 4, 5, 6, 7 or 8).

Because of the mailbox address formation mechanism, this address must be zero modulo a power of two which is greater than twice the highest assigned channel number: if n is the highest assigned channel number, then Go must be zero modulo a power of two which is greater than 2 x n.

2. Control processor

There is an 8-position panel switch in each memory controller, to define what processor will be designated as control processor for this memory controller. Let p be the value of this switch in memory controller (m) MULTICS SYSTEM-PROGRAMMERS MANUAL SECTION

SECTION BC.4.01 PAGE 3

3. Processor base address Po

The 18 bit panel switch in processor p is set with the value So that defines the base address Po of the fault vector the following way:  $Po = So \times 64$ . Po has to be zero modulo 1024. This assumption is made in order to be able to determine the base address of the fault vector without having to know the port number through which processor p receives the interrupt from memory controller m.

4. Bootload base address Bo

This address is set by an 18 bit panel switch on the GIOC. It must be equal to the location to which the control processor will be forced when it receives the interrupt at the end of the loading.

$Bo = Po + k \times 64$

where k is the port number through which the processor p is connected to the memory controller m.

5. Bootload channel selection

A separate switch within the GIOC will select one of the 2 peripheral adapter channels implemented within the bootload as the loader program channel.

This switch is read by the GIOC when the diodes are transferred into core; its value is 1 or 2. If the value is 2, then the GIOC "OR"s a one in word Go + 17, bit 17.

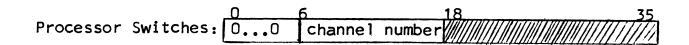

When the switch is set to 1, the bootload program described below assumes that the tape to be read is on channel 31. When the switch is set to 2, the bootload program reads the channel number from the processor switches, the value of which is given by the operator on the processor, before pushing the bootload button.

The processor switches are a 36 bit word; the channel number is in bits 6-17. Bits 18-35 are not used by the bootload program.

The channel number <u>must be</u> the channel number of the <u>LPW</u>, that is bit 17 must be zero.

6. Interrupt cell assignment

Each status channel used by a GIOC is assigned one of the 32 interrupt cells in the memory controller (m) which contains the base address Go of the GIOC mailboxes. The assignment of a status channel to a particular execute interrupt cell is accomplished by a patch plug. Status channel 0 should always be assigned a higher priority than any other status channel.

The bootload assumes that

GIOC status channel 0 is assigned cell i  $(0 \le i \le 3)$

GIOC status channel 1 is assigned cell j  $(4 \le j \le 11)$

7. Channel number of the peripheral device

The bootload assumes that the device is the tape handler on channel #30, device #0, unless the bootload channel switch is set to 2 (see bootload channel selection).

Pushing the bootload button

When the bootload button is depressed

The Initialize signal is activated, causing all active and passive units to be initialized.

Then the sequence of events described below occurs.

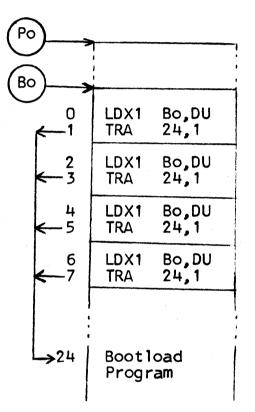

1. 64 words are loaded from GIOC into core

a. Interrupt vector

8 words are loaded at Bo to Bo + 7, providing four interrupt entries associated with cells 0,1,2,3. All of them transfer to the beginning of the bootload program (Bo + 24)

b. Bootload program

The bootload program is loaded starting at Bo + 24

Mailboxes c.

> Control words are stored in the mailboxes. All addresses contained in these control words are relative to Go; they will be adjusted to absolute addresses by the bootload program before the Connect GIOC is issued.

#### 2. Interrupt 0

When the 64 words are loaded, GIOC sends an SXC (Set Execute Interrupt Cell) to the Memory Controller (m) containing the base address Go. The interrupt cell i, associated with status channel #0 is set (status channel 0 has been assigned interrupt cell 0,1,2 or 3). The Memory Controller (m) interrupts its control processor (p); the interrupt vector associated with this processor and this Memory Controller is located at Bo, where 4 interrupt entries have been stored. Control goes to the beginning of bootload program. at STARTO (Bo+24).

3. Bootload program execution: STARTO

Tests the value of the bootload channel selection switch, using the bit 17 of word Go+17. If this bit is ONE, the CCW is read from the 36 switches and the channel number is stored in Go+CCW bits O-17.

Sets interrupt vector entries O-11 so that they will transfer to START1 after the tape label is skipped.

Initializes control words in the mailboxes for the first connect.

Sends a connect to GIOC through connect channel specified by the Connect Operand Word (COW) located at Go+O, for skipping the tape label until a physical EOF mark is encountered.

Waits for interrupt 1 which will occur when the physical EOF mark is found.

4. Interrupt 1

When the tape label is skipped, status channel 1 is activated and interrupt cell j is set ON ( $4 \le j \le 11$ ). The interrupt vector is entered that transfers to START1.

5. Bootload program execution: START1

Sets interrupt vector entries O-11 so that they will transfer to START2 after the next physical record of the MST is read

Initializes control words in the mailboxes for the second connect.

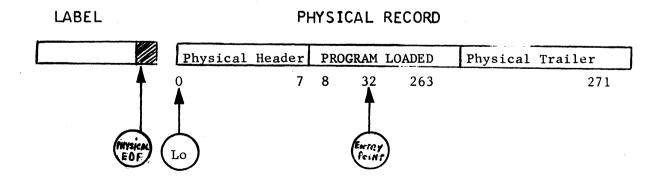

Sends a connect to GIOC for reading one physical record on the tape into location Lo=Go+1024

Waits for interrupt2 which will occur when the physical record is read

6. Interrupt 2

When the physical record is read, status channel 1 is activated, and the interrupt vector is entered that transfers to START2.

7. Bootload program execution: START2

If <u>major</u> status is <u>ready</u>, transfers to Lo+32. The constant 32 has been chosen to allow flexibility in the logical format of the tape read by the bootload program.

If not, stop.

#### Bootload program code and Mailboxes

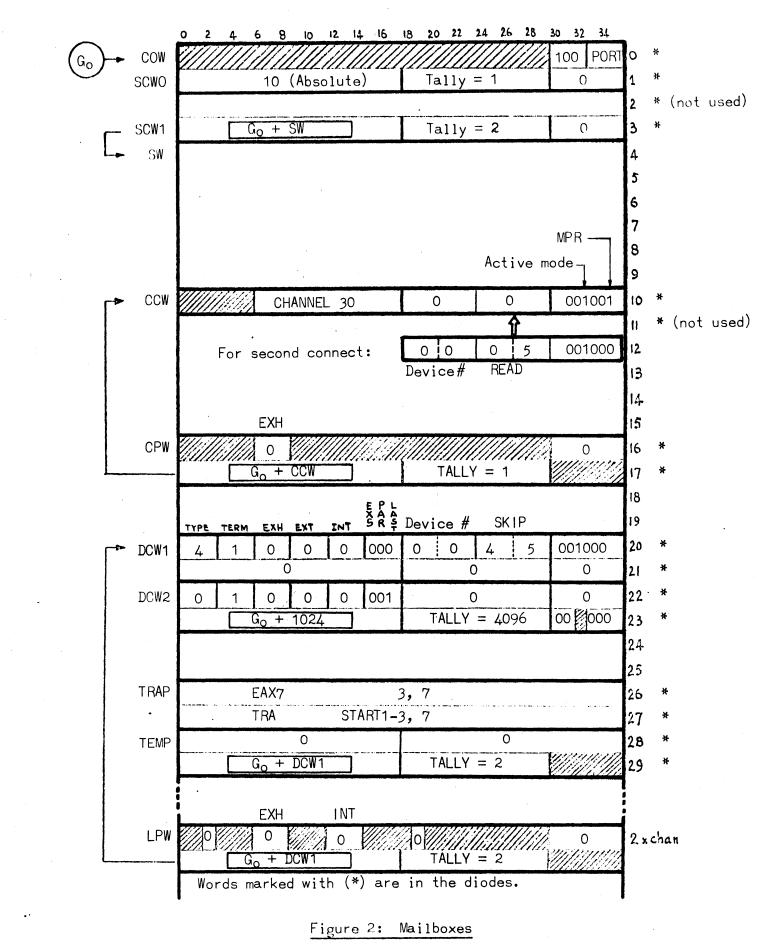

The bootload program code is shown in Figure 1. The contents of the mailboxes is shown in Figure 2. In both figures 1 and 2,

stands for zero when the 64 words are in the diodes and stands for the value x when the 64 words are in core.

stands for zero when the 64 words are in the diodes and stands for x during the connect operation. The value x is stored by the bootload program.

## 1. Program Code

This program relocates all internal references by index register 1, which is loaded upon entry to contain the base address of the bootload (Bo). It relocates all external references by index register 0 which is loaded in the program, to contain the base address of the mailboxes (Go). Thus, this program written for loading at zero will operate anywhere, the mailboxes being anywhere in memory.

2. Mailboxes

Figure 2 shows the Mailboxes as they are in the diodes. All addresses of control words (except the absolute address 10 in word 1) are zero in the diodes and are stored by the bootload program before the connect is issued.

COW: Has to be at Go+O

Bits 33-35 specify the Memory Controller port number to which the GIOC is connected. This port number is stored in the diodes. Bits 31-32 are zero and specify the connect channel #8.

SCWO: Has to be at Go+1 It is the SCW used when status channel #0 is activated, after the diodes have been transferred into core.

The status is stored in <u>ABSOLUTE</u> <u>location</u> <u>10</u>.

SCW1: Has to be at Go+3 It is the SCW used when status channel #1 is activated. The address is zero in the diodes.

CCW: Channel Command Word. The CCW is at Go+10. Figure 2 shows the CCW as it is stored in the diodes, that is:

> The LPW channel number is 30; bit 35=1 indicates that the multiple physical record (MPR) mode is set; bits 32-33=10 set the active mode. The device number (bits 18-23) and the operation code (bits 24-29) are not used in the CCW when the multiple physical record mode is set. They are found in the command DCW (DCW1).

MPR mode has to be set because the command SKIP does not cause any data transfer; if the mode was single physical record (Bit 35=0), no LPW list would be activated; as a consequence no status channel could be specified and no interrupt would occur after completion of the command SKIP.

Using the MPR mode, the LPW is activated even if there is no data transfer, and we can specify the status channel by a pointer in the command DCW (bits 3-5 of DCW1).

Before the second connect is issued, the bootload program sets bits 18-23 of the CCW with the value 000510 (octal):

| Bits $18-23 = 000$ |     |                         |

|--------------------|-----|-------------------------|

| Bits $24-29 = 000$ | 101 | define the operation    |

|                    |     | code READ               |

| Bits $30-31 = 00$  |     | they must be zero       |

| Bits $32-33 = 10$  |     | set the active mode     |

| Bit $34 = 0$       |     | it must be zero         |

| Bit $35 = 0$       |     | set the single physical |

|                    |     | record mode.            |

### CPW: Has to be in Go+16 The address contained in Go+17 is zero in the diodes. GIOC will "OR" a one in bit 17 of word Go+17 if the bootload channel switch is set to 2.

DCW1: It is a command DCW (bits 0-2 = 4). The device number (bits 18-23) is 0: the operation code (bits 24-29) is 45 octal = SKIP. When SKIP is completed, the EOF status forces termination; the terminate signal occurs and the status word is stored using status channel #1 (bits 3-5 = 001 in DCW1). Correct operation depends on EOF forcing termination.

DCW2: It is a data transfer DCW (bits 0-2 = 0) for use during the READ operation. If a terminate signal occurs, status channel 1 is activated. Bit 17 = 1 which indicates the last DCW. Exhaust, external and internal signals should not occur, and if they do, it is an error.

TRAP:

Words TRAP and TRAP+1 contain two instructions:

EAX7 3,7 TRA START1-3,7

These instructions are stored by the bootload program into each pair of the interrupt vector. Index register 7 is initialized with the value Bo. When the interrupt occurs after the label is skipped the interrupt vector is entered. The first instruction causes register 7 to be incremented by 3 (X7=Bo+3); the second instruction transfers to START1.

When the next interrupt occurs after the physical record is read, the first instruction sets register 7 to the value BO+6 and the second instruction transfers to START1+3 which is START2.

TEMP:

Words TEMP and TEMP+1 are used to manufacture the information that has to be stored in the LPW. When the program has computed the address of the LPW, it stores the contents of TEMP and TEMP+1 in LPW and LPW+1.

LPW:

The LPW is not stored in the diodes since its location is not known (the channel number specified by the CCW is 30 in the diodes, but it can be changed by the operator).

#### PAGE 10 MULTICS SYSTEM-PROGRAMMERS MANUAL SECTION BC.4.01

Before the first connect is issued for skipping the label. LPW contains zero. LPW+1 points to DCW1 and the tally is 2.

When the first connect is given, the multiple physical record mode is set (Bit 35=1 in CCW). the LPW is activated, the command DCW (DCW1) is executed which initiates a SKIP operation. When SKIP is completed, the EOF status will force termination and leave the LPW pointing at DCW2.

Before the second connect is issued, the CCW is set to contain the device #0, the operation code READ (05 octal) and the single physical record mode bit (Bit 35=0). The LPW is activated which still points to DCW2; the GIOC initiates the READ operation and interprets DCW2 as the last data transfer DCW (Bit 17=1) for the connect in single physical record mode.

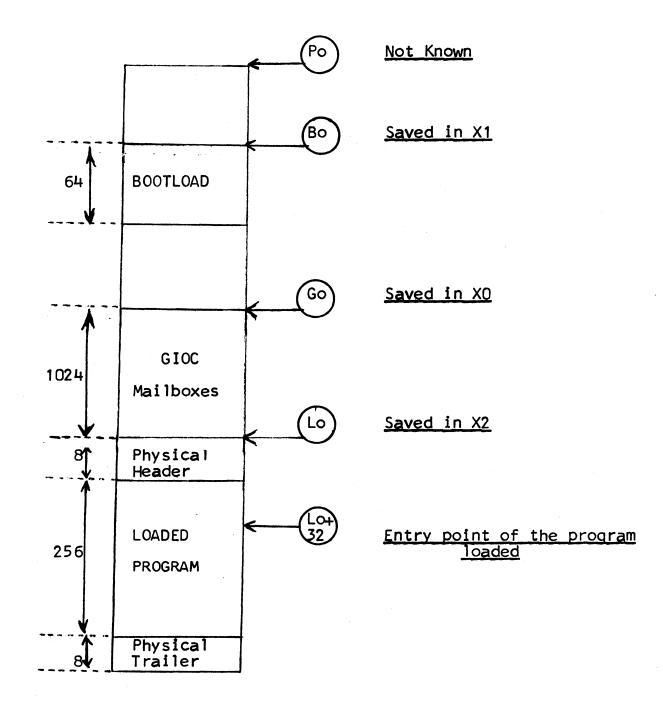

#### <u>Communication</u> between bootload and the program loaded

When the bootload program transfers control to the program it has loaded:

- 1. Go: GIOC base address saved in index register O :

- 2. Bootload base address : Bo: saved in index register 1 Program loaded address : saved in index register 2 LO:

- 3. Po: Processor base address : is not known, so it cannot 4.

- be passed to the program loaded. If the convention that Po is 0 modulo 1024 has been followed. Po can be computed from Bo.

- The COW used by the bootload is at location Go+O 5.

- The entry point of the loaded program must be at location 6. Lo+32 as shown below: this program may be the bootstrap initializer, or a dump program or a diagnostic program

If the tape cannot be read, the bootload will halt on the instruction DIS 1

# Memory Map

.

| <br> |     |    |                                                                                                 |

|------|-----|----|-------------------------------------------------------------------------------------------------|

| GO   | ΕϘU | 0  | GO is the symbolic name for index                                                               |

| BO   | ΕϘυ | 1  | register O that contains Go<br>BO is the symbolic name for index<br>register 1 that contains Bo |

| LO   | ΕϘU | 2  | LO is the symbolic name for index<br>register 2 that contains Lo                                |

| CØW  | ΕϘυ | 0  | Relative position of CØW in the mailbox area                                                    |

| SCW1 | EQU | 3  | Relative position of SCW1 in the mailbox area                                                   |

| SW   | EQU | 4  | Relative position of SW in the mailbox area                                                     |

| CCW  | EQU | 10 | Relative position of CCW in the mailbox area                                                    |

| CPW  | EQU | 16 | Relative position of CPW in the mailbox area                                                    |

| DCW1 | EQU | 20 | Relative position of DCW1 in the mailbox area                                                   |

| DCW2 | ΕϘυ | 22 | Relative position of DCW2 in the mailbox area                                                   |

| TRAP | EQU | 26 | Relative position of TRAP in the mailbox area                                                   |

| TEMP | ΕϘU | 28 | Relative position of TEMP in the mailbox area                                                   |

|      |     |    |                                                                                                 |

|      |     |    |                                                                                                 |

|      |     |    |                                                                                                 |

# Figure 1: The Bootload Program

EVEN CONTINUED NEXT PAGE

|                     | LDX1<br>TRA     | Bo,DU<br>24,B0        | INTERRUPT VECTOR FOR INTERRUPT CELL O                             |

|---------------------|-----------------|-----------------------|-------------------------------------------------------------------|

|                     | LDX1            | Bo,DU                 | INTERRUPT VECTOR FOR INTERRUPT CELL 1                             |

| (After<br>Diodes)   | TRA<br>LDX1     | 24,80<br>Bo,DU        | INTERRUPT VECTOR FOR INTERRUPT CELL 2                             |

| biodes              | TRA<br>LDX1     | 24,80<br>Bo,DU        | INTERRUPT VECTOR FOR INTERRUPT CELL 3                             |

|                     | TRA<br>ORG      | 24,BO<br>24           |                                                                   |

| <b>└─&gt;</b> STAR⊺ |                 | Go,DU<br>1024,GO      | XO=BASE ADD GIOC = GO<br>X2=BASE ADD BOOTSTRAP LOADER             |

|                     | EAX7            | 0,B0                  | SET X7 WITH BOOTLOAD BASE ADDRESS BO                              |

|                     | LDX3<br>TZE     | 17,GO<br>A,BO         | TEST G0+17 BIT 17                                                 |

|                     | RSW<br>EAX3     | O,AU                  | READ SWITCHES IF BIT 17 ON                                        |

| А                   | STX3<br>EAX3    | CCW,GO<br>O,BO        | STORE CHANNEL NUMBER FROM SWITCHES<br>X3=BOOTLOAD BASE ADDRESS=BO |

|                     | EAX4<br>LDAQ    | -12<br>TRAP,GO        | FOR INTERRUPT CELLS 0 to 11<br>ALL INT. VECTOR GO TO START1       |

| SETRA               | AP STAO<br>EAX3 | 0,32,3                | SET NEXT PAIR                                                     |

|                     | EAX4<br>TMI     | - 1 <b>,</b> 4        | INCREMENT COUNT                                                   |

|                     | EAX3            | SETRAP, BO<br>SW, GO  |                                                                   |

|                     | STX3<br>STX2    | SCW1,GO<br>DCW2+1,GO  | SET ADD IN SCW1<br>SET ADD IN DCW DATA                            |

|                     | EAX3            | DCW1,GO               |                                                                   |

|                     | STX3<br>LDX3    | TEMP+1,GO<br>CCW,GO   | STORE GO+DCW1 IN TEMPORARY LPW                                    |

|                     | STX3<br>EAX3    | *+1,B0<br>**,3        | CALCULATE THE LPW ADDRESS<br>DEPENDING ON THE CHANNEL NUMBER      |

|                     | STX3<br>LDAQ    | *+2,BO<br>TEMP,GO     | STORE LPW ADDRESS IN *+2<br>LOAD TEMPORARY LPW                    |

| BECON               | STAQ            | **,GÖ                 | STORE TEMPORARY LPW IN REAL LPW                                   |

| RECON               | STX3            | CCW,GO<br>CPW+1,GO    | INIT. CPW FOR EACH CONNECT                                        |

| (After<br>Label)    | LDX3<br>SXL3    | =0100,DU<br>CPW+1,GO  | SET TALLY OF 1                                                    |

| $\checkmark$        | CIOC<br>DIS     | 0,G0<br>0             | INITIATE CONNECT OPERATION<br>WAIT FOR I/O                        |

| STAR⊺               | T1 LDX6<br>SXL6 | =0510,DU<br>CCW,GO    | INITIALIZE CCW WITH READ COMMAND<br>BEFORE ISSUING SECOND CONNECT |

| ∣<br>START          | TRA<br>T2 LXL3  | RECÔN, BO<br>SW+1, GO | GO TO ISSUE ONE OTHER CONNECT<br>EXAMINE STATUS FROM READ         |

| After               | EAX3<br>TMI     | -4096,3<br>32,L0      | TRANSFER TO LOADED PROGRAM                                        |

| Record              | DIS             | 1                     | MAJOR STATUS NOT O.K.                                             |

| $\smile$            |                 |                       |                                                                   |