## Goal

Although hypothetical minimalist computers has long been an interesting study in Computer Science, there exists very few actual hardware implementations of such computers, and the goal of this investigation was to design one from scratch using the standard integrated logic circuits of digital electronics.

## The Investigation

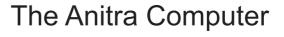

I started my investigation by defining the exact requirements for my computer. Then, as I was aiming to keep its design as simple as possible, I tried to logically deduce what components would unquestionably be required parts of it. Using only components presumed to be essential, I could put together a structure that should be capable of fetching

## Conclusions

circuits in detail on paper.

Given the initial requirement to restrict its design to standard circuits, it seems possible to devise a computer of ultimate simplicity by proving the need for each hardware component logically. Howey-

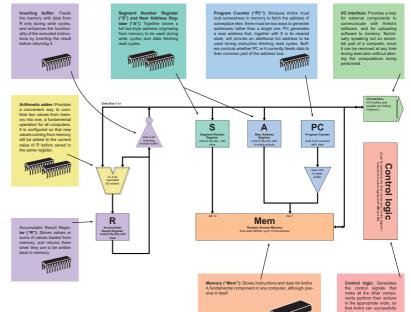

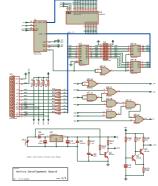

> The Anitra CPU Structural Logi

and executing instructions in memory.

From this, I went on by designing the necessary control logic and defining the

hardware component logically. However, the argument used in the investigation is not watertight, and it does not cover in detail the computer's control circuits.

The computer components found to be essential included data retaining units for holding addresses and values during memory write cycles, a data retaining unit resembling a program counter for holding additional addresses independent of the former ones, and an arithmetic adder for combining two values from memory into one. It is interesting to note that familiar components such as a program counter and an arithmetic adder are needed even in a minimalist computer. However, efficient simplifications may be done by limiting branching functionality and the memory area where instructions can reside.

A computer is a machine that, given enough time and memory, can perform any computational operation on a set of data. A minimalist computer is a computer that satisfies this requirement with only a minimum level of architectural complexity."

Anitra's two universal instructions

tions in memory. An instruction is a signal for the computer to carry out a single where computational operation. Surv operations may read and their value in memory, or affect the order instructions are executed. By combining such in structions in the appropriate way, more advanced operations may be synthesised that Anton and the appropriate way and advanced operations may be synthesized that Anton and the appropriate way and advanced operations may be estimated and any advanced and the synthesized and advanced operations and the ends, subvided in the blocks of B instructions each. These wall execute over and over again in an etemal loop. While modern computes have hundreds of different instructions available for the programmer to use, Anthin bas only two

## "mov S,Q" Read the value in memory at address S, and save an inverted copy at address Q.

2 Read the values in memory at addresses S and Q, add them to-gether, and save the result in inverted at address O. If the result is too large to fit into Q, skp the rest of the instructions in the current block, (in the latter case, discard the result's most significant bit and save the stat. If the current instruction is the fast one in its block, skep all the instructions in the following block instead.)

dress is a value identifying a single place in memory. In Anitra, an 8-bit comeach such place may hold a value made up of 8 binary digits. A value is said nverted if each of its digits are complemented (1s becomes 0s and vice versa)

ilhough Anitra's two different instructions may seem fairly primitive, and though the area of memory where instructions are executed can only old 128 such instructions, there is still in fact no limitation on what soft and other the structure of the still in the structure of the structure of and of the memory and because tooms instructions may be used to reproram other ones, there are plenty of ways to extend Anitra's functionality to one practical level. Together, Anitra's two instructions are truly universal

| Theory of<br>Operation<br>(Summan)<br>WARING: Geska only!<br>Arkin is built around a 32-kikely/e SRAM<br>memory oip with an 8-bil data bui. Ful 15-<br>al addresses for the memory are made from<br>a 7-bit segment number and an 8-bit new<br>divide referent data for the memory through | sero. The stair address can come<br>the lack A or the counter PC depr<br>which of the two counter PC depr<br>puts enabled. PCs first and last 4 bits<br>increased or reset individually. PCs in<br>infland bits controlled directly by the<br>document of the state of the state of the<br>bits and the state of the state of the<br>counter of the document of the state<br>is also be stated as the state of the state<br>of the state of the state of the state of the<br>attempt of the state that the state of the state<br>state bits. The data bits in the state that<br>also be a state that the state that the state<br>state bits. The state that the state that the state<br>state bits. The state that a state state that the<br>state bits. The state that a state state that a state<br>state bits. The state state state state state state state<br>is a state state state state state state state state state<br>state bits. The state state state state state state state<br>state bits. The state state state state state state state<br>state bits. The state state state state state state state state state<br>state bits. The state st |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                            | trol signals, one for each clock cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |