# **The Anitra Computer** How simple can a basic computer be designed to be using TTL/74-series standard circuits?

http://www.princeton.edu/~ebakke/anitra by Eirik Bakke

#### Goal

A computer is a machine that, given enough time and memory, can perform any rigidly defined computational operation. A minimalist computer is a computer that satisfies this requirement with only a minimum level of architectural complexity. Although hypothetical minimalist computers has long been an interesting study in Computer Science, there exists very few actual hardware implementations of such, and the goal of this investigation was to design one from scratch

using the standard 74-series TTL-compatible digital logic circuits (ICs).

#### The Investigation

I started my investigation by defining the exact requirements for my com-puter. Then, as I was aiming to keep its design as simple as possible, I tried to discuss which components would unquestionably have to be included. The resulting set of components included D-flip flops for holding target addresses and values during memory write cycles, and a unit resembling a program counter for simultaneously keeping track of an additional address. An arithmetic adder was needed for the computer to be able to combine two values into one. Using only components presumed to be es-

sential, I could put together a structure that should be capable of fetching and executing instructions in memory. From this, I went on by designing the necessary control logic and defining all circuits in detail on paper. The resulting computer, called Anitra, has two universal instructions: "move with complement" and "add with complement and branch if carry". Branching is done in a special way which does not require program counter to be programmable. In addition, the program counter is limited in size, which restricts the memory area where instructions may reside.

#### Conclusions

The CPU part of the finished Anitra computer has an 8-bit data bus and consists of three octal D-flip-flops, two octal tri-state buffers, one 8-bit non-programmable counter, two 4-bit arithmetic adders and some control logic (single gates and D-flip-flops only). Given the initial premises, it is difficult to imagine how the structural parts of the computer could have been made with significantly fewer or simpler components than those used; each of its components has been shown to fill a specific need during the execution of operations presumed to be essential

I have now completed the next great step in this project, which is the construction of a working physical prototype of the Anitra computer. Finally, I am now in the process of writing an operating syste for the computer.

### The Anitra Computer

And

**66**A computer is a machine that, given enough time and memory, can perform any computational operation on a set of data. A minimalist computer is a computer that satisfies this requirement with only a minimum level of architectural complexity."

#### Anitra's two universal instructions

tions are executed th subcions in the appropriate way, more advanced operations may be sym thesised. The Anitra computer has a predefined area in memory where instructions may reside, subdivided into *blocks* of 8 instructions each These will execute over and over again in an eternal loop. While tradi-tional computers have hundreds of different instructions available for the nalist" computer and has only

Anitra, an 8-bit computer, each such place may hold a value made up of 8 binary digits. A value is said to be inverted if each

ions, there is still in fact no lir ing them. Because the instruc

Theory of Operation (Summary) WARNING: Geeks only!

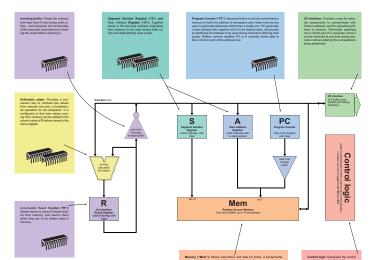

Anitra is built around 32-kilolyte SRAM memory chip with an 8-bit data bus. Full 15-bit addresses for the memory are made from a 7-bit segment number and an 8-bit near address. The two octal D lip-flops S and A may both retrieve data from the memory through the data bus. The segment number is al-ways prepared in [Inf-pdop S. The tatter may contain data from the memory, or tmay be reset to zero. The near address can come from ether [Inf-plops A cit the segment of the segment of the segment of the segment and the segment of the segment of the segment and the segment of the segment and the segment segment and the segment segment and the segment and

## counter PC, depending on which of the two currently has its instate outputs enabled. PC's first and last 4 bits may be increased or reset individually. PC's least significant bit is controlled directly by the con-trol logic A simple accumulator system is connected to the data bus. The file-flops R may be triggered, which will add the current data from memory to bit existing value through an antimetic adder; or it may be neset to zero. The result may be directed back to the memory to bit and the reset of zero. memory during write cycles through an inverting tri-state buffer. To execute instructions, the control log-

The address that is now passed to memory is no longer the address of the instruction itself, but the pointer that was specified as its first argument. The memory will load the value at this address, which is two two-byte full addresses. The most significant bit of the segment number of the last address is used to been reset and initially contains zero, nothing will be added to the value as R is clocked this time. This setion block. In any case, the accumulator value is finally w ee oo tha loo

uction byte, which is next

The execution sequence starts by resetting octal ilip-flops R and S, and selecting PC. PC's least significant bit is set to 0. This will generate the address of the current instruction's first byte, which the memory will now load and place on the data bus. In the next step, this byte is clocked into A while PC is still selected. PC's least significant bit is then set to 1. The memoed into S while A is selected. PC is increased state buller. To strebule insurfacions, the control log-tic outputs a 7-step sequence of control signals, one for each clock cycle. A set of D flip-flops, called ES, is configured to keep track of the current execution state. Each instruction is 4 bytes long, consisting of