Secure Processors Part II: Intel SGX Security Analysis and MIT Sanctum Architecture

# Secure Processors Part II: Intel SGX Security Analysis and MIT Sanctum Architecture

Victor Costan, Ilia Lebedev and Srinivas Devadas victor@costan.us, ilebedev@mit.edu and devadas@mit.edu Computer Science and Artificial Intelligence Laboratory Massachusetts Institute of Technology

# Foundations and Trends<sup>®</sup> in Electronic Design Automation

Published, sold and distributed by: now Publishers Inc. PO Box 1024 Hanover, MA 02339 United States Tel. +1-781-985-4510 www.nowpublishers.com sales@nowpublishers.com

Outside North America: now Publishers Inc. PO Box 179 2600 AD Delft The Netherlands Tel. +31-6-51115274

The preferred citation for this publication is

V. Costan, I. Lebedev and S. Devadas. Secure Processors Part II: Intel SGX Security Analysis and MIT Sanctum Architecture. Foundations and Trends<sup>®</sup> in Electronic Design Automation, vol. 11, no. 3, pp. 249–361, 2017.

This Foundations and Trends $^{\circledR}$  issue was typeset in  $\LaTeX$  using a class file designed by Neal Parikh. Printed on acid-free paper.

ISBN: 978-1-68083-302-7

© 2017 V. Costan, I. Lebedev and S. Devadas

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, mechanical, photocopying, recording or otherwise, without prior written permission of the publishers.

Photocopying. In the USA: This journal is registered at the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923. Authorization to photocopy items for internal or personal use, or the internal or personal use of specific clients, is granted by now Publishers Inc for users registered with the Copyright Clearance Center (CCC). The 'services' for users can be found on the internet at: www.copyright.com

For those organizations that have been granted a photocopy license, a separate system of payment has been arranged. Authorization does not extend to other kinds of copying, such as that for general distribution, for advertising or promotional purposes, for creating new collective works, or for resale. In the rest of the world: Permission to photocopy must be obtained from the copyright owner. Please apply to now Publishers Inc., PO Box 1024, Hanover, MA 02339, USA; Tel. +1 781 871 0245; www.nowpublishers.com; sales@nowpublishers.com

now Publishers Inc. has an exclusive license to publish this material worldwide. Permission to use this content must be obtained from the copyright license holder. Please apply to now Publishers, PO Box 179, 2600 AD Delft, The Netherlands, www.nowpublishers.com; e-mail: sales@nowpublishers.com

# Foundations and Trends $^{\mbox{\scriptsize $\mathbb{R}$}}$ in Electronic Design Automation

Volume 11, Issue 3, 2017 **Editorial Board**

# **Editor-in-Chief**

### Radu Marculescu

Carnegie Mellon University United States

#### **Editors**

Robert K. Brayton UC Berkeley

Raul Camposano

Nimbic

K.T. Tim Cheng UC Santa Barbara

Jason Cong UCLA

Masahiro Fujita University of Tokyo

Georges Gielen KU Leuven Tom Henzinger

Institute of Science and Technology

Austria

Andrew Kahng  $UC\ San\ Diego$

Andreas Kuehlmann

Coverity

Sharad Malik

Sharad Malik

Princeton University

Ralph Otten TU Eindhoven Joel Phillips

Cadence Berkeley Labs

Jonathan Rose

University of Toronto

Rob Rutenbar University of Illinois at Urbana-Champaign

Alberto Sangiovanni-Vincentelli

$\begin{array}{c} UC\ Berkeley \\ \text{Leon Stok} \\ IBM\ Research \end{array}$

# **Editorial Scope**

#### **Topics**

Foundations and Trends<sup>®</sup> in Electronic Design Automation publishes survey and tutorial articles in the following topics:

- System level design

- Behavioral synthesis

- Logic design

- Verification

- Test

- Physical design

- Circuit level design

- Reconfigurable systems

- Analog design

- Embedded software and parallel programming

- Multicore, GPU, FPGA, and heterogeneous systems

- Distributed, networked embedded systems

- Real-time and cyberphysical systems

#### Information for Librarians

Foundations and Trends<sup>®</sup> in Electronic Design Automation, 2017, Volume 11, 4 issues. ISSN paper version 1551-3939. ISSN online version 1551-3947. Also available as a combined paper and online subscription.

Foundations and Trends<sup>®</sup> in Electronic Design Automation Vol. 11, No. 3 (2017) 249–361 © 2017 V. Costan, I. Lebedev and S. Devadas

DOI: 10.1561/1000000052

# Secure Processors Part II: Intel SGX Security Analysis and MIT Sanctum Architecture

Victor Costan, Ilia Lebedev and Srinivas Devadas victor@costan.us, ilebedev@mit.edu and devadas@mit.edu Computer Science and Artificial Intelligence Laboratory Massachusetts Institute of Technology

# Contents

| 1 | Intr | oduction                                            | 3  |

|---|------|-----------------------------------------------------|----|

|   | 1.1  | The Case for Hardware Isolation                     | 4  |

|   | 1.2  | Intel SGX is Not the Answer                         | 5  |

|   | 1.3  | MIT Sanctum Processor                               | 6  |

| 2 | An . | Analysis of Intel's Software Guard Extensions (SGX) | 9  |

|   | 2.1  | SGX Implementation Overview                         | 10 |

|   | 2.2  | SGX Memory Access Protection                        | 15 |

|   | 2.3  | SGX Security Check Correctness                      | 22 |

|   | 2.4  | Tracking TLB Flushes                                | 30 |

|   | 2.5  | Enclave Signature Verification                      | 34 |

|   | 2.6  | Key Hierarchy and Derivation                        | 39 |

|   | 2.7  | SGX Security Properties                             | 42 |

| 3 | The  | MIT Sanctum Processor                               | 61 |

|   | 3.1  | Threat Model                                        | 62 |

|   | 3.2  | Programming Model Overview                          | 64 |

|   | 3.3  | Protection Boundaries                               | 70 |

|   | 3.4  | Security Primitives                                 | 70 |

|   | 3.5  | Hardware Modifications                              | 72 |

|   | 3.6  | Software Design                                     | 79 |

|    |       | Security Analysis of Sanctum |     |

|----|-------|------------------------------|-----|

| 4  | Con   | clusion                      | 105 |

| Ac | know  | ledgments                    | 107 |

| Re | feren | ices                         | 109 |

#### **Abstract**

This manuscript is the second in a two part survey and analysis of the state of the art in secure processor systems, with a specific focus on remote software attestation and software isolation. The first part established the taxonomy and prerequisite concepts relevant to an examination of the state of the art in trusted remote computation: attested software isolation containers (enclaves). This second part extends Part I's description of Intel's Software Guard Extensions (SGX), an available and documented enclave-capable system, with a rigorous security analysis of SGX as a system for trusted remote computation. This part documents the authors' concerns over the shortcomings of SGX as a secure system and introduces the MIT Sanctum processor developed by the authors: a system designed to offer stronger security guarantees, lend itself better to analysis and formal verification, and offer a more straightforward and complete threat model than the Intel system, all with an equivalent programming model.

This two part work advocates a principled, transparent, and well-scrutinized approach to system design, and argues that practical guarantees of privacy and integrity for remote computation are achievable at a reasonable design cost and performance overhead.

# 1

# Introduction

Between the Snowden revelations and the seemingly unending series of high-profile hacks of the past few years, the public's confidence in software systems has decreased considerably. At the same time, key initiatives such as cloud computing and the IoT (Internet of Things) are gaining popularity but require users to place much trust in the systems providing these services. We must therefore develop capabilities to build software systems with compelling security, and gain back our users' trust.

This manuscript is the second in a two part survey of the state of the art in secure processor systems, with a specific focus on remote software attestation and software isolation. Part I [Costan et al., 2017] established relevant background in computer system design (§ I.2) and security primitives (§ I.3), and surveyed relevant prior work (§ I.4). The same work discussed the attested software isolation container (enclave): a modern primitive for modular secure software and trusted remote computation, as exemplified by Intel's Software Guard Extensions (§ I.5).

This manuscript extends the discussion of enclaves and SGX by surveying the implementation and security properties of SGX (§ 2),

4 Introduction

and documents the authors' concerns with its vulnerabilities to several classes of software attacks. Informed by the successes and shortcomings of SGX, this manuscript also discusses the MIT Sanctum processor (§ 3): a secure processor that offers an equivalent programming model with strong security guarantees against an insidious software threat model including cache timing and memory access pattern attacks. With this work, we hope to enable a shift in discourse in secure hardware architecture away from plugging specific security holes to a principled approach to eliminating attack surfaces.

#### 1.1 The Case for Hardware Isolation

The best known practical method for securing a software system amounts to modularizing the system's code in a way that minimizes code in the modules responsible for the system's security. Formal verification techniques are then applied to these modules, which make up the system's trusted codebase (TCB). The method assumes that software modules are isolated, so the TCB must also include the mechanism providing the isolation guarantees.

Today's systems rely on an operating system kernel, or a hypervisor (such as Linux or Xen, respectively) for software isolation. However **each** of the last three years (2012-2014) witnessed over 100 new security vulnerabilities in Linux [cve, 2014a, Chen et al., 2011], and over 40 in Xen [cve, 2014b].

One may hope that formal verification methods can produce a secure kernel or hypervisor. Unfortunately, these codebases are far outside our verification capabilities: Linux and Xen have over 17 million [Anthony, 2014] and 150,000 [xen, 2015] lines of code, respectively. In stark contrast, the seL4 formal verification effort [Klein et al., 2009] spent 20 man-years to cover 9,000 lines of code.

Given Linux and Xen's history of vulnerabilities and uncertain prospects for formal verification, a prudent system designer cannot include either in a TCB (trusted computing base), and must look elsewhere for a software isolation mechanism. Fortunately, Intel's Software Guard Extensions (SGX) [McKeen et al., 2013, Anati et al., 2013] has brought attention to the alternative of providing software isolation primitives in the CPU's hardware. This avenue is appealing because the CPU is an unavoidable TCB component, and processor manufacturers have strong economic incentives to build correct hardware.

# 1.2 Intel SGX is Not the Answer

Unfortunately, although the SGX design includes a vast array of defenses against a variety of software and physical attacks, it fails to offer meaningful software isolation guarantees. The SGX threat model protects against all direct attacks, but excludes "side-channel attacks", even if they can be performed via software alone.

Alarmingly, cache timing attacks require only unprivileged software running on the victim's host computer, and do not rely on any physical access to the machine. This is particularly concerning in a cloud computing scenario, where gaining software access to the victim's computer only requires a credit card [Ristenpart et al., 2009], whereas physical access is harder, requiring trespass, coercion, or social engineering on the cloud provider's employees.

Similarly, in many Internet of Things (IoT) scenarios, the processing units have some amount of physical security, but they run outdated software stacks that have known security vulnerabilities. For example, an attacker may exploit a vulnerability in an IoT lock's Bluetooth stack and obtain software execution privileges, then mount a cache timing attack on its access-granting process, and obtain the cryptographic key that opens the lock.

Furthermore, the analysis of SGX documentation as described in Part I of this work reveals that it is impossible for anyone but Intel to reason about SGX's security properties, because significant implementation details are not covered by the publicly available documentation. This is a concern, as the myriad of security vulnerabilities [Wojtczuk and Rutkowska, 2011, 2009b, Wojtczuk et al., 2009, Duflot et al., 2006, Rutkowska and Wojtczuk, 2008, Wojtczuk and Rutkowska,

6 Introduction

2009a, Wecherowski, 2009, Embleton et al., 2010] in TXT [Grawrock, 2009], Intel's previous attempt at securing remote computation, show that securing the machinery underlying Intel's processors is incredibly challenging, even in the presence of strong economic incentives.

If a successor to SGX claimed to protect against cache timing attacks, substantiating such a claim would require an analysis of its hardware and microcode, and ensuring that no implementation detail is vulnerable to cache timing attacks. Barring a highly unlikely shift to open-source hardware from Intel, such analysis will never happen.

A concrete example: the SGX documentation [Int, 2013, 2014] does not state where SGX stores the EPCM (enclave page cache map). If the EPCM is stored in cacheable RAM, page translation verification is subject to cache timing attacks. Interestingly, this detail is unnecessary for analyzing the security of today's SGX implementation, as we know that SGX uses the operating system's page tables, and page translations are therefore vulnerable to cache timing attacks. The example does, however, demonstrate the fine nature of crucial details that are simply undocumented in today's hardware security implementations.

In summary, while the principles behind SGX have great potential, the SGX design does not offer meaningful isolation guarantees, and the SGX implementation is not open enough for independent researchers to be able to analyze its security properties.

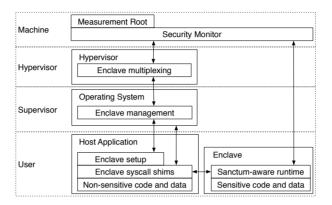

#### 1.3 MIT Sanctum Processor

The Sanctum processor's main contribution is a software isolation scheme that addresses the issues raised above: Sanctum's isolation provably defends against known software side-channel attacks, including cache timing attacks and passive address translation attacks. Sanctum is a co-design that combines *minimal* and *minimally invasive* hardware modifications with a trusted software security monitor that is amenable to rigorous analysis and does not perform cryptographic operations using keys.

Sanctum achieves minimality by reusing and lightly modifying existing, well-understood mechanisms. For example, Sanctum's per-

enclave page tables implementation uses the core's existing page walking circuit, and requires very little extra logic. Sanctum is minimally invasive because it does not require modifying any major CPU building block. It only adds hardware to the interfaces between blocks, and does not modify any block's input or output. The use of conventional building blocks limits the effort needed to validate a Sanctum implementation.

Sanctum demonstrates that memory access pattern attacks by malicious software can be foiled without incurring unreasonable overheads. Its hardware changes are small, small enough to present the added circuits, in their entirety, in Figures 3.9 and 3.10. Sanctum cores have the same clock speed as their insecure counterparts, as there are no modifications on the CPU core critical execution path. Using a straightforward page-coloring-based cache partitioning scheme with Sanctum adds a few percent of overhead in execution time, which is orders of magnitude lower than the overheads of the ORAM schemes [Goldreich, 1987, Stefanov et al., 2013] that are usually employed to conceal memory access patterns.

All layers of Sanctum's TCB are open-sourced [MIT, 2017], and unencumbered by patents, trade secrets, or other similar intellectual property concerns that would disincentivize security researchers from analyzing it. The Sanctum prototype targets the Rocket Chip [Lee et al., 2014], an open-sourced implementation of the RISC-V [Waterman et al., 2014, 2015] instruction set architecture, which is an open standard. Sanctum's software stack bears the MIT license.

To further encourage analysis, most of Sanctum's security monitor is written in portable C++ which, once rigorously analyzed, can be used across different CPU implementations. Furthermore, even the non-portable assembly code can be reused across different implementations of the same architecture. In comparison, SGX's microcode is CPU model-specific, so each micro-architectural revision would require a separate verification effort.

# An Analysis of Intel's Software Guard Extensions (SGX)

Intel's Software Guard Extensions (SGX) is a set of extensions to the Intel architecture that aims to provide integrity and confidentiality guarantees to security- sensitive computation performed on a computer where the privileged software (kernel, hypervisor, etc) is potentially malicious.

This section extends the survey of Intel's SGX presented in (§ I.5). Software Guard Extensions, and analyzes SGX based on the 3 papers [McKeen et al., 2013, Anati et al., 2013, Hoekstra et al., 2013] that introduced it, on the Intel Software Developer's Manual [Int, 2015b] (which supersedes the SGX manuals [Int, 2013, 2014]), an ISCA 2015 tutorial [Int, 2015a], and two patents [McKeen et al., 2009, Johnson et al., 2010]. We use the papers, reference manuals, and tutorial as primary data sources, and only draw on the patents to fill in missing information.<sup>1</sup>

This section discusses the implementation of SGX (including a series of intelligent guesses of important but undocumented aspects of

<sup>&</sup>lt;sup>1</sup>We note that this manuscript does not reflect the information available in two papers [Johnson et al., 2016, Gueron, 2016] that were published after [Costan and Devadas, 2016].

SGX), its security argument, and the implication of the complex Intel ecosystem on the ability of SGX to enable trusted remote computation.

## 2.1 SGX Implementation Overview

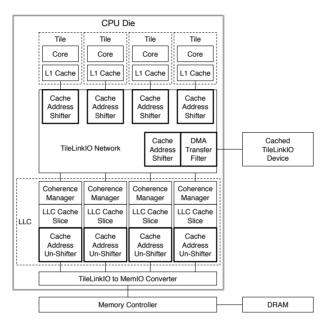

An under-documented and overlooked feat achieved by the SGX design is that implementing it on an Intel processor has a very low impact on the chip's hardware design. SGX's modifications to the processor's execution cores (§ I.2.9.4) are either very small or completely nonexistent. The CPU's uncore (§ I.2.9.3, § I.2.11.3) receives a new module, the Memory Encryption Engine, which appears to be fairly self-contained.

The bulk of the SGX implementation is relegated to the processor's microcode (§ I.2.14), which supports a much higher development speed than the chip's electrical circuitry.

#### 2.1.1 Execution Core Modifications

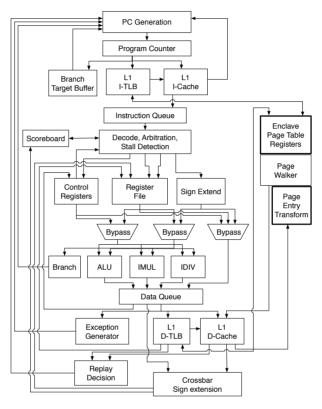

At a minimum, the SGX design requires a very small modification to the processor's execution cores (§ I.2.9.4), in the Page Miss Handler (PMH, § I.2.11.5).

The PMH resolves TLB misses, and consists of a fast path that relies on an FSM page walker, and a microcode assist fallback that handles the edge cases (§ I.2.14.3). The bulk of SGX's memory access checks, which are discussed in § 2.2, can be implemented in the microcode assist.

The only modification to the PMH hardware that is absolutely necessary to implement SGX is developing an ability to trigger the microcode assist for all address translations when a logical processor (§ I.2.9.4) is in enclave mode (§ I.5.4), or when the physical address produced by the page walker FSM matches the Processor Reserved Memory (PRM, § I.5.1) range.

The PRM range is configured by the PRM Range Registers (§ I.5.1), which have exactly the same semantics as the Memory Type Range Registers (MTRRs, § I.2.11.4) used to configure a variable memory range. The page walker FSM in the PMH is already configured to issue a microcode assist when the page tables are in uncacheable

memory (§ I.2.11.4). Therefore, the PRMRR can be represented as an extra MTRR pair.

#### 2.1.2 Uncore Modifications

The Intel's Software Development Manual (SDM) [Int, 2015b] states that DMA transactions (§ I.2.9.1) that target the PRM range are aborted by the processor. The SGX patents disclose that the PRMRR protection against unauthorized DMA is implemented by having the SGX microcode set up entries in the Source Address Decoder (SAD) in the uncore CBoxes and in the Target Address Decoder (TAD) in the integrated Memory Controller (MC).

§ I.2.11.3 mentions that Intel's Trusted Execution Technology (TXT) [Grawrock, 2009] already takes advantage of the integrated MC to protect a DRAM range from DMA. It is highly likely that the SGX implementation reuses the mechanisms brought by TXT, and only requires the extension of the SADs and TADs by one entry.

SGX's major hardware modification is the Memory Encryption Engine (MEE) that is added to the processor's uncore (§ I.2.9.3, § I.2.11.3) to protect SGX's Enclave Page Cache (EPC, § I.5.1.1) against physical attacks.

The MEE was first briefly described in the ISCA 2015 SGX tutorial [Int, 2015a]. According to the information presented there, the MEE roughly follows the approach introduced by Aegis [Suh et al., 2003] [Suh et al., 2005], which relies on a variation of Merkle trees to provide the EPC with confidentiality, integrity, and freshness guarantees (§ I.3.1). Unlike Aegis, the MEE uses non-standard cryptographic primitives that include a slightly modified AES operating mode (§ I.3.1.2) and a Carter-Wegman [Carter and Wegman, 1977, Wegman and Carter, 1981] MAC (§ I.3.1.3) construction. The MEE was further described in [Gueron, 2016].

Both the ISCA SGX tutorial and the patents state that the MEE is connected to to the Memory Controller (MC) integrated in the CPU's uncore. However, all sources are completely silent on further implementation details. The MEE overview slide states that "the Memory Controller detects [the] address belongs to the MEE region, and

routes transaction to MEE", which suggests that the MEE is fairly self-contained and has a narrow interface to the rest of the MC.

Intel's SGX patents use the name Crypto Memory Aperture (CMA) to refer to the MEE. The CMA description matches the MEE and PRM concepts, as follows. According to the patents, the CMA is used to securely store the EPC, relies on crypto controllers in the MC, and loses its keys during deep sleep. These details align perfectly with the SDM's statements regarding the MEE and PRM.

The Intel patents also disclose that the EPCM (§ I.5.1.2) and other structures used by the SGX implementation are also stored in the PRM. This rules out the possibility that the EPCM requires on-chip memory resembling the last-level cache (§ I.2.11, § I.2.11.3).

Last, the SGX patents shine a bit of light on an area that the official Intel documentation is completely silent about, namely the implementation concerns brought by computer systems with multiple processor chips. The patents state that the MEE also protects the Quick-Path Interconnect (QPI, § I.2.9.1) traffic using link-layer encryption.

#### 2.1.3 Microcode Modifications

According to the SGX patents, all SGX instructions are implemented in microcode. This can also be deduced by reading the SDM's pseudocode for all the instructions, and realizing that it is highly unlikely that any SGX instruction can be implemented in 4 or fewer microops (§ I.2.10), which is the most that can be handled by the simple decoders used in the hardware fast paths (S I.2.14.1).

The Asynchronous Enclave Exit (AEX, § I.5.4.3) behavior is also implemented in microcode. § I.2.14.2 draws on an assortment of Intel patents to conclude that hardware exceptions (§ I.2.8.2), including both faults and interrupts, trigger microcode events (§ I.2.14.2). It follows that the SGX implementation can implement AEX by modifying the hardware exception handlers in the microcode.

The SGX initialization sequence is also implemented in microcode. SGX is initialized in two phases. First, it is very likely that the boot sequence in microcode (§ I.2.14.4) was modified to initialize the registers associated with the SGX microcode. The ISCA SGX tutorial

states that the MEE' keys are initialized during the boot process. Second, SGX instructions are enabled by setting a bit in a Model-Specific Register (MSR, § I.2.4). This second phase involves enabling the MEE and configuring the SAD and TAD to protect the PRM range. Both tasks are amenable to a microcode implementation.

The SGX description in the SDM implies that the SGX implementation uses a significant number of new registers, which are only exposed to microcode. However, the SGX patents reveal that most of these registers are actually stored in DRAM.

For example, the patents state that each TCS (§ I.5.2.4) has two fields that receive the values of the DR7 and IA32\_DEBUGCTL registers when the processor enters enclave mode (§ I.5.4.1), and are used to restore the original register values during enclave exit (§ I.5.4.2). The SDM documents these fields as "internal CREGs" (CR\_SAVE\_DR7 and CR\_SAVE\_DEBUGCTL), which are stated to be "hardware specific registers".

The SGX patents document a small subset of the CREGs described in the SDM, summarized in Table 2.1, as microcode registers. While in general we trust official documentation over patents, in this case we use the CREG descriptions provided by the patents, because they appear to be more suitable for implementation purposes.

From a cost-performance standpoint, the cost of register memory only seems to be justified for the state used by the PMH to implement SGX's memory access checks, which will be discussed in § 2.2. The other pieces of state listed as CREGs are accessed so infrequently that storing them in dedicated SRAM would make very little sense.

The SGX patents state that SGX requires very few hardware changes, and most of the implementation is in microcode, as a positive fact. We therefore suspect that minimizing hardware changes was a high priority in the SGX design, and that any SGX modification proposals need to be aware of this priority.

Table 2.1: The CREGs implemented by SGX.

| SDM Name           | Bits | Scope                | Description                                      |

|--------------------|------|----------------------|--------------------------------------------------|

| CSR_SGX_OWNEREPOCH |      | CPU Chip Package     | 128 CPU Chip Package Used by EGETKEY (§ I.5.7.5) |

| CR_ENCLAVE_MODE    | 1    | 1 Logical Processor  | 1 when executing code inside an enclave          |

| CR_ACTIVE_SECS     | 16   | 16 Logical Processor | The index of the EPC page storing the            |

|                    |      |                      | current enclave's SECS                           |

| CR_TCS_LA          | 64   | 64 Logical Processor | The virtual address of the                       |

|                    |      |                      | TCS (§ I.5.2.4) used to enter (§ I.5.4.1)        |

|                    |      |                      | the current enclave                              |

| CR_TCS_PH          | 16   | 16 Logical Processor | The index of the EPC page storing the            |

|                    |      |                      | TCS used to enter the current enclave            |

| CR_XSAVE_PAGE_0    | 16   | 16 Logical Processor | The index of the EPC page storing the            |

|                    |      |                      | first page of the current SSA (§ I.5.2.5)        |

## 2.2 SGX Memory Access Protection

SGX guarantees that the software inside an enclave is isolated from all other software, including the software executing in other enclaves. This isolation guarantee is at the core of SGX's security model.

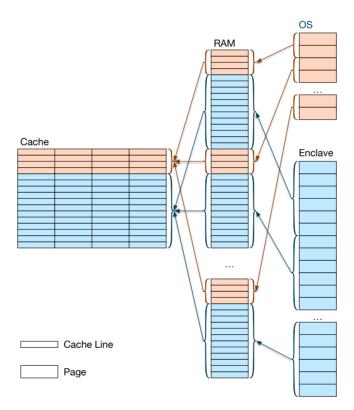

It is tempting to assume that the main protection mechanism in SGX is the Memory Encryption Engine (MEE) described in § 2.1.2, as it encrypts and MACs the DRAM's contents. However, the MEE sits in the processor's memory controller, which is at the edge of the on-chip memory hierarchy, below the caches (§ I.2.11). Therefore, the MEE cannot protect an enclave's memory from software attacks.

The root of SGX's protections against software attacks is a series of memory access checks which prevents the currently running software from accessing memory that does not belong to it. Specifically, non-enclave software is only allowed to access memory outside the PRM range, while the code inside an enclave is allowed to access non-PRM memory, and the EPC pages owned by the enclave.

Although it is believed [Evtyushkin et al., 2014] that SGX's access checks are performed on every memory access check, Intel's patents disclose that the checks are performed in the Page Miss Handler (PMH, § I.2.11.5), which only handles TLB misses.

#### 2.2.1 Functional Description

The intuition behind SGX's memory access protections can be built by considering what it would take to implement the same protections in a trusted operating system or hypervisor, solely by using the page tables that direct the CPU's address translation feature (§ I.2.5).

The hypothetical trusted software proposed above can implement enclave entry (§ I.5.4.1) as a system call (§ I.2.8.1) that creates page table entries mapping the enclave's memory. Enclave exit (§ I.5.4.2) can be a symmetric system call that removes the page table entries created during enclave entry. When modifying the page tables, the system software has to consider TLB coherence issues (§ I.2.11.5) and perform TLB shootdowns when appropriate.

SGX leaves page table management under the system software's control, but it cannot trust the software to set up the page tables in any particular way. Therefore, the hypothetical design described above cannot be used by SGX as-is. Instead, at a conceptual level, the SGX implementation approximates the effect of having the page tables set up correctly by inspecting every address translation that comes out of the Page Miss Handler (PMH, § I.2.11.5). The address translations that do not obey SGX's access control restrictions are rejected before they reach the TLBs.

SGX's approach relies on the fact that software always references memory using virtual addresses, so all micro-ops (§ I.2.10) that reach the memory execution units (§ I.2.10.1) use virtual addresses that must be resolved using the TLBs before the actual memory accesses are carried out. By contrast, the processor's microcode (§ I.2.14) has the ability to issue physical memory accesses, which bypass the TLBs. Conveniently, SGX instructions are implemented in microcode (§ 2.1.3), so they can bypass the TLBs and access memory that is off limits to software, such as the EPC page holding an enclave's SECS (§ I.5.1.3).

The SGX address translation checks use the information in the Enclave Page Cache Map (EPCM, § I.5.1.2), which is effectively an inverted page table that covers the entire EPC. This means that each EPC page is accounted for by an EPCM entry, using the structure is summarized in Table 2.2, with the PT (page type) field enumerated by Table 2.3. The EPCM fields were described in detail in § I.5.1.2, § I.5.2.3, § I.5.2.4, § I.5.5.1, and § I.5.5.2.

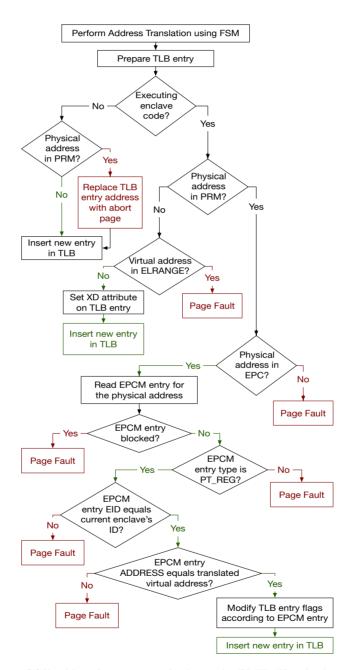

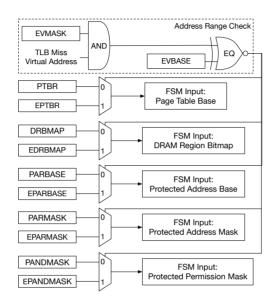

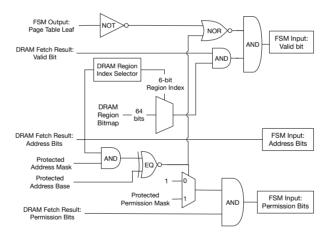

Conceptually, SGX adds the access control logic illustrated in Figure 2.1 to the PMH. SGX's security checks are performed after the page table attributes-based checks (§ I.2.5.3) defined by the Intel architecture. It follows that SGX's access control logic has access to the physical address produced by the page walker FSM.

SGX's security checks depend on whether the logical processor (§ I.2.9.4) is in enclave mode (§ I.5.4) or not. While the processor is outside enclave mode, the PMH allows any address translation that does not target the PRM range (§ I.5.1). When the processor is inside

**Figure 2.1:** SGX adds a few security checks to the PMH. The checks ensure that all TLB entries created by the address translation unit meet SGX's memory access restrictions.

| Field       | Bits | Description                             |

|-------------|------|-----------------------------------------|

| VALID       | 1    | 0 for un-allocated EPC pages            |

| BLOCKED     | 1    | page is being evicted                   |

| R           | 1    | enclave code can read                   |

| W           | 1    | enclave code can write                  |

| X           | 1    | enclave code can execute                |

| PT          | 8    | page type (Table 2.3)                   |

| ADDRESS     | 48   | the virtual address used to access this |

|             |      | page                                    |

| ENCLAVESECS |      | the EPC slot number for the SECS of the |

|             |      | enclave owning the page                 |

Table 2.2: The fields in an EPCM entry.

Table 2.3: Values of the PT (page type) field in an EPCM entry.

| Type    | Allocated by | Contents              |

|---------|--------------|-----------------------|

| PT_REG  | EADD         | enclave code and data |

| PT_SECS | ECREATE      | SECS (§ I.5.1.3)      |

| PT_TCS  | EADD         | TCS (§ I.5.2.4)       |

| PT_VA   | EPA          | VA (§ I.5.5.2)        |

enclave mode, the PMH performs the checks described below, which provide the security guarantees described in § I.5.2.3.

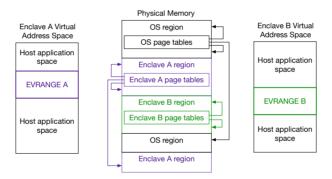

First, virtual addresses inside the enclave's virtual memory range (ELRANGE, § I.5.2.1) must always translate into physical addresses inside the EPC. This way, an enclave is assured that all code and data stored in ELRANGE is covered by SGX's confidentiality, integrity, and freshness guarantees. Since the memory outside ELRANGE does not enjoy these guarantees, the SGX design disallows having enclave code outside ELRANGE. This is most likely accomplished by setting the disable execution (XD, § I.2.5.3) attribute on the TLB entry.

Second, an EPC page must only be accessed by the code of the enclave who owns the page. For the purpose of this check, each enclave is identified by the index of the EPC page that stores the enclave's SECS (§ I.5.1.3). The current enclave's identifier is stored

in the CR\_ACTIVE\_SECS microcode register during enclave entry. This register is compared against the enclave identifier stored in the EPCM entry corresponding to the EPC page targeted by the address translation.

Third, some EPC pages cannot be accessed by software. Pages that hold SGX internal structures, such as a SECS, a TCS (§ I.5.2.4), or a VA (§ I.5.5.2) must only be accessed by SGX's microcode, which uses physical addresses and bypasses the address translation unit, including the PMH. Therefore, the PMH rejects address translations targeting these pages.

Blocked (§ I.5.5.1) EPC pages are in the process of being evicted (§ I.5.5), so the PMH must not create new TLB entries targeting them.

Next, an enclave's EPC pages must always be accessed using the virtual addresses associated with them when they were allocated to the enclave. Regular EPC pages, which can be accessed by software, are allocated to enclaves using the EADD (§ I.5.3.2) instruction, which reads in the page's address in the enclave's virtual address space. This address is stored in the LINADDR field in the corresponding EPCM entry. Therefore it is sufficient for the PMH to is to ensure that LINADDR in the address translation's target EPCM entry equals the virtual address that caused the TLB miss which invoked the PMH.

At this point, the PMH's security checks have completed, and the address translation result will definitely be added to the TLB. Before that happens, however, the SGX extensions to the PMH apply the access restrictions in the EPCM entry for the page to the address translation result. While the public SGX documentation we found did not describe this process, there is a straightforward implementation that fulfills SGX's security requirements. Specifically, the TLB entry bits P, W, and XD can be AND-ed with the EPCM entry bits R, W, and X.

### 2.2.2 EPCM Entry Representation

Most EPCM entry fields have obvious representations. The exception is the LINADDR and ENCLAVESECS fields, described below. These

representations explain SGX's seemingly arbitrary limit on the size of an enclave's virtual address range (ELRANGE).

The SGX patents disclose that the LINADDR field in an EPCM entry stores the virtual page number (VPN, § I.2.5.1) of the corresponding EPC page's expected virtual address, relative to the ELRANGE base of the enclave that owns the page.

The representation described above reduces the number of bits needed to store LINADDR, assuming that the maximum ELRANGE size is significantly smaller than the virtual address size supported by the CPU. This desire to save EPCM entry bits is the most likely motivation for specifying a processor model-specific ELRANGE size, which is reported by the CPUID instruction.

The SDM states that the ENCLAVESECS field of an EPCM entry corresponding to an EPC page indicates the SECS of the enclave that owns the page. Intel's patents reveal that the SECS address in ENCLAVESECS is represented as a physical page number (PPN, § I.2.5.1) relative to the start of the EPC. Effectively, this relative PPN is the 0-based EPC page index.

The EPC page index representation saves bits in the EPCM entry, assuming that the EPCM size is significantly smaller than the physical address space supported by the CPU. The ISCA 2015 SGX tutorial slides mention an EPC size of 96MB, which is significantly smaller than the physical addressable space on today's typical processors, which is  $2^{36}$  -  $2^{40}$  bytes.

#### 2.2.3 PMH Hardware Modifications

The SDM describes the memory access checks performed after SGX is enabled, but does not provide any insight into their implementation. Intel's patents hint at three possible implementations that make different cost-performance tradeoffs. This section summarizes the three approaches and argues in favor of the implementation that requires the fewest hardware modifications to the PMH.

All implementations of SGX's security checks entail adding a pair of memory type range registers (MTRRs, § I.2.11.4) to the PMH. These registers are named the Secure Enclave Range Registers (SERR)

in Intel's patents. Enabling SGX on a logical processor initializes the SERR to the values of the Protected Memory Range Registers (PMRR, § I.5.1).

Furthermore, all implementations have the same behavior when a logical processor is outside enclave mode. The memory type range described by the SERR is enabled, causing a microcode assist to trigger for every address translation that resolves inside the PRM. SGX's implementation uses the microcode assist to replace the address translation result with an address that causes memory access transactions to be aborted.

The three implementations differ in their behavior when the processor enters enclave mode (§ I.5.4) and starts executing enclave code.

The alternative that requires the least amount of hardware changes sets up the PMH to trigger a microcode assist for every address translation. This can be done by setting the SERR to cover the whole of physical memory (e.g., by setting the mask to zero, and the base to a non-zero value). In this approach, the microcode assist implements all enclave mode security checks illustrated in Figure 2.1.

A speedier alternative adds a pair of registers to the PMH that represents the current enclave's ELRANGE and modifies the PMH so that, in addition to checking physical addresses against the SERR, it also checks the virtual addresses going into address translations against ELRANGE. When either check is true, the PMH invokes the microcode assist used by SGX to implement its memory access checks. Assuming the ELRANGE registers use the same base / mask representation as variable MTRRs, enclave exits can clear ELRANGE by zeroing both the base and the mask. This approach uses the same microcode assist implementation, minus the ELRANGE check that moves into the PMH hardware.

The second alternative described above has the benefit that the microcode assist is not invoked for enclave mode accesses outside EL-RANGE. However, § I.5.2.1 argues that an enclave should treat all virtual memory addresses outside ELRANGE as untrusted storage, and only use that memory to communicate with software outside the enclave. Taking this into consideration, well-designed enclaves would

spend relatively little time performing memory accesses outside EL-RANGE. Therefore, this second alternative is unlikely to obtain performance gains that are worth its cost.

The last and most performant alternative would entail implementing the access checks shown in Figure 2.1 in hardware. Similarly to the address translation FSM, the hardware would only invoke a microcode assist when a security check fails and a Page Fault needs to be handled.

The high-performance implementation described above avoids the cost of microcode assists for all TLB misses, assuming well-behaved system software. In this association, a microcode assist results in a Page Fault, which triggers an Asynchronous Enclave Exit (AEX, § I.5.4.3). The cost of the AEX dominates the performance overhead of the microcode assist.

While this last implementation looks attractive, one needs to realize that TLB misses occur quite infrequently, so a large improvement in the TLB miss speed translates into a much less impressive improvement in overall enclave code execution performance. Taking this into consideration, it seems unwise to commit to extensive hardware modifications in the PMH before SGX gains adoption.

# 2.3 SGX Security Check Correctness

In § 2.2.1, we argued that SGX's security guarantees can be obtained by modifying the Page Miss Handler (PMH, § I.2.11.5) to block undesirable address translations from reaching the TLB. This section builds on the result above and outlines a correctness proof for SGX's memory access protection.

Specifically, we outline a proof for the following invariant. At all times, the TLB entries in every logical processor are be consistent with the SGX security policy. By the argument in § 2.2.1, the invariant translates into an assurance that all memory accesses performed by software obey SGX's security model. The high-level proof structure is presented because it helps understand how the SGX security checks come together. By contrast, a detailed proof

would be incredibly tedious, and would do very little to boost the reader's understanding of SGX.

### 2.3.1 Top-Level Invariant Breakdown

We first break down the above invariant into specific cases based on whether a logical processor (LP) is executing enclave code or not, and on whether the TLB entries translate virtual addresses in the current enclave's ELRANGE (§ I.5.2.1). When the processor is outside enclave mode, ELRANGE can be considered to be empty. This reasoning yields the three cases outlined below.

- 1. At all times when an LP is outside enclave mode, its TLB may only contain physical addresses belonging to DRAM pages outside the PRM.

- 2. At all times when an LP is inside enclave mode, the TLB entries for virtual addresses outside the current enclave's ELRANGE must contain physical addresses belonging to DRAM pages outside the PRM.

- 3. At all times when an LP is in enclave mode, the TLB entries for virtual addresses inside the current enclave's ELRANGE must match the virtual memory layout specified by the enclave author.

The first two invariant cases can be easily proven independently for each LP, by induction over the sequence of instructions executed by the LP. For simplicity, the reader can assume that instructions are executed in program mode. While the assumption is not true on processors with out-of-order execution (§ I.2.10), the arguments presented here also hold when the executed instruction sequence is considered in retirement order, for reasons that will be described below.

An LP will only transition between enclave mode and non-enclave mode at a few well-defined points, which are EENTER (§ I.5.4.1), ERESUME (§ I.5.4.4), EEXIT (§ I.5.4.2), and Asynchronous Enclave Exits (AEX, § I.5.4.3). According to the SDM, all transition points flush the TLBs and the out-of-order execution pipeline. In other words, the

TLBs are guaranteed to be empty after every transition between enclave mode and non-enclave mode, so we can consider all these transitions to be trivial base cases for our induction proofs.

While SGX initialization is not thoroughly discussed, the SDM mentions that loading some Model-Specific Registers (MSRs, § I.2.4) triggers TLB flushes, and that system software should flush TLBs when modifying Memory Type Range Registers (MTRRs, § I.2.11.4). Given that the space of possible SGX implementations described in § 2.2.3 entails adding a MTRR, it is safe to assume that enabling SGX mode also results in a TLB flush and out-of-order pipeline flush, and can be used by our induction proof as well.

The base cases in the induction proofs are serialization points for out-of-order execution, as the pipeline is flushed during both enclave mode transitions and SGX initialization. This makes the proofs below hold when the program order instruction sequence is replaced with the retirement order sequence.

The first invariant case holds because while the LP is outside enclave mode, the SGX security checks added to the PMH (§ 2.2.1, Figure 2.1) reject any address translation that would point into the PRM before it reaches the TLBs. A key observation for proving the induction step of this invariant case is that the PRM never changes after SGX is enabled on an LP.

The second invariant case can be proved using a similar argument. While an LP is executing an enclave's code, the SGX memory access checks added to the PMH reject any address translation that resolves to a physical address inside the PRM, if the translated virtual address falls outside the current enclave's ELRANGE. The induction step for this invariant case can be proven by observing that a change in an LP's current ELRANGE is always accompanied by a TLB flush, which results in an empty TLB that trivially satisfies the invariant. This follows from the constraint that an enclave's ELRANGE never changes after it is established, and from the observation that the LP's current enclave can only be changed by an enclave entry, which must be preceded by an enclave exit, which triggers a TLB flush.

The third invariant case is best handled by recognizing that the Enclave Page Cache Map (EPCM, § I.5.1.2) is an intermediate representation for the virtual memory layout specified by the enclave authors. This suggests breaking down the case into smaller sub-invariants centered around the EPCM, which will be proven in the subsections below.

- 1. At all times, each EPCM entry for a page that is allocated to an enclave matches the virtual memory layout desired by the enclave's author.

- 2. Assuming that the EPCM contents is constant, at all times when an LP is in enclave mode, the TLB entries for virtual addresses inside the current enclave's ELRANGE must match EPCM entries that belong to the enclave.

- An EPCM entry is only modified when there is no mapping for it in any LP's TLB.

The second and third invariant combined prove that all TLBs in an SGX-enabled computer always reflect the contents of the EPCM, as the third invariant essentially covers the gaps in the second invariant. This result, in combination with the first invariant, shows that the EPCM is a bridge between the memory layout specifications of the enclave authors and the TLB entries that regulate what memory can be accessed by software executing on the LPs. When further combined with the reasoning in § 2.2.1, the whole proof outlined here results in an end-to-end argument for the correctness of SGX's memory protection scheme.

### 2.3.2 EPCM Entries Reflect Enclave Author Design

This subsection outlines the proof for the following invariant. At all times, each EPCM entry for a page that is allocated to an enclave matches the virtual memory layout desired by the enclave's author.

A key observation, backed by the SDM pseudocode for SGX instructions: all instructions that modify the EPCM pages allocated to an enclave are synchronized using a lock in the enclave's SECS. This entails the existence of a time ordering of the EPCM modifications associated with an enclave. We prove the invariant stated above using a proof by induction over this sequence of EPCM modifications.

EPCM entries allocated to an enclave are created by instructions that can only be issued before the enclave is initialized, specifically ECREATE (§ I.5.3.1) and EADD (§ I.5.3.2). The contents of the EPCM entries created by these instructions contributes to the enclave's measurement (§ I.5.6), together with the initial data loaded into the corresponding EPC pages.

§ I.3.3.3 argues that we can assume that enclaves with incorrect measurements do not exist, as they will be rejected by software attestation. Therefore, we can assume that the attributes used to initialize EPCM pages match the enclave authors' memory layout specifications.

EPCM entries can be evicted to untrusted DRAM, together with their corresponding EPC pages, by the EWB (§ I.5.5.4) instruction. The ELDU / ELDB (§ I.5.5) instructions reload evicted page contents and metadata back into the EPC and EPCM. By induction, we can assume that an EPCM entry matches the enclave author's specification when it is evicted. Therefore, if we can prove that the EPCM entry that is reloaded from DRAM is equivalent to the entry that was evicted, we can conclude that the reloaded entry matches the author's specification.

A detailed analysis of the cryptographic primitives used by the SGX design to protect the evicted EPC page contents and its associated metadata is outside the scope of this work. Summarizing the description in § I.5.5, the contents of evicted pages is encrypted using AES-GMAC (§ I.3.1.3), which is an authenticated encryption mechanism. The MAC tag produced by AES-GMAC covers the EPCM metadata as well as the page data, and includes a 64-bit version that is stored in a version tree whose nodes are Version Array (VA, (§ I.5.5.2) pages.

Assuming no cryptographic weaknesses, SGX's scheme does appear to guarantee the confidentiality, integrity, and freshness of the EPC page contents and associated metadata while it is evicted to untrusted memory. It follows that EWB will only reload an EPCM entry if the contents is equivalent to the contents of an evicted entry.

The equivalence notion invoked here is slightly different from perfect equality, in order to account for the allowable operation of evicting an EPC page and its associated EPCM entry, and then reloading the page contents to a different EPC page and a different EPCM entry, as illustrated in Figure I.5.10. Loading the contents of an EPC page at a different physical address than it had before does not break the virtual memory abstraction, as long as the contents is mapped at the same virtual address (the LINEARADDRESS EPCM field), and has the same access control attributes (R, W, X, PT EPCM fields) as it had when it was evicted.

The rest of this section enumerates the address translation attacks prevented by the MAC verification that occurs in ELDU / ELDB. This is intended to help the reader develop some intuition for the reasoning behind using the page data and all EPCM fields to compute and verify the MAC tag.

The most obvious attack is prevented by having the MAC cover the contents of the evicted EPC page, so the untrusted OS cannot modify the data in the page while it is stored in untrusted DRAM. The MAC also covers the metadata that makes up the EPCM entry, which prevents the more subtle attacks described below.

The enclave ID (EID) field is covered by the MAC tag, so the OS cannot evict an EPC page belonging to one enclave, and assign the page to a different enclave when it is loaded back into the EPC. If EID was not covered by authenticity guarantees, a malicious OS could read any enclave's data by evicting an EPC page belonging to the victim enclave, and loading it into a malicious enclave that would copy the page's contents to untrusted DRAM.

The virtual address (LINADDR) field is covered by the MAC tag, so the OS cannot modify the virtual memory layout of an enclave by evicting an EPC page and specifying a different LINADDR when loading it back. If LINADDR was not covered by authenticity guarantees, a malicious OS could perform the exact attack shown in Figure I.3.24 and described in § I.3.7.3.

The page access permission flags (R, W, X) are also covered by the MAC tag. This prevents the OS from changing the access permission bits in a page's EPCM entry by evicting the page and loading it back in. If the permission flags were not covered by authenticity guarantees, the OS could use the ability to change EPCM access permissions to facilitate exploiting vulnerabilities in enclave code. For example, exploiting a stack overflow vulnerability is generally easier if OS can make the stack pages executable.

The nonce stored in the VA slot is also covered by the MAC. This prevents the OS from mounting a replay attack that reverts the contents of an EPC page to an older version. If the nonce would not be covered by integrity guarantees, the OS could evict the target EPC page at different times  $t_1$  and  $t_2$  in the enclave's life, and then provide the EWB outputs at  $t_1$  to the ELDU / ELDB instruction. Without the MAC verification, this attack would successfully revert the contents of the EPC page to its version at  $t_1$ .

While replay attacks look relatively benign, they can be quite devastating when used to facilitate double spending.

# 2.3.3 TLB Entries for ELRANGE Reflect EPCM Contents

This subsection sketches a proof for the following invariant. At all times when an LP is in enclave mode, the TLB entries for virtual addresses inside the current enclave's ELRANGE must match EPCM entries that belong to the enclave. The argument makes the assumption that the EPCM contents is constant, which will be justified in the following subsection.

The invariant can be proven by induction over the sequence of TLB insertions that occur in the LP. This sequence is well-defined because an LP has a single PMH, so the address translation requests triggered by TLB misses must be serialized to be processed by the PMH.

The proof's induction step depends on the fact that the TLB on hyper-threaded cores (§ I.2.9.4) is dynamically partitioned between the two LPs that share the core, and no TLB entry is shared between the LPs. This allows our proof to consider the TLB insertions associated with one LP independently from the other LP's insertions, which means we don't have to worry about the state (e.g., enclave mode) of the other LP on the core.

The proof is further simplified by observing that when an LP exits enclave mode, both its TLB and its out-of-order instruction pipeline are flushed. Therefore, the enclave mode and current enclave register values used by address translations are guaranteed to match the values obtained by performing the translations in program order.

Having eliminated the complexities associated with hyper-threaded (§ I.2.9.4) out-of-order (§ I.2.10) execution cores, it is easy to see that the security checks outlined in Figure 2.1 and § 2.2.1 ensure that TLB entries that target EPC pages are guaranteed to reflect the constraints in the corresponding EPCM entries.

Last, the SGX access checks implemented in the PMH reject any address translation for a virtual address in ELRANGE that does not resolve to an EPC page. It follows that memory addresses inside ELRANGE can only map to EPC pages which, by the argument above, must follow the constraints of the corresponding EPCM entries.

## 2.3.4 EPCM Entries are Not In TLBs When Modified

In this subsection, we outline a proof that an EPCM entry is only modified when there is no mapping for it in any LP's TLB.. This proof analyzes each of the instructions that modify EPCM entries.

For the purposes of this proof, we consider that setting the BLOCKED attribute does not count as a modification to an EPCM entry, as it does not change the EPC page that the entry is associated with, or the memory layout specification associated with the page.

The instructions that modify EPCM entries in such a way that the resulting EPCM entries have the VALID field set to true require that the EPCM entries were invalid before they were modified. These instructions are ECREATE (§ I.5.3.1), EADD (§ I.5.3.2), EPA (§ I.5.5.2), and ELDU / ELDB (§ I.5.5). The EPCM entry targeted by any these instructions must have had its VALID field set to false, so the invariant proved in the previous subsection implies that the EPCM entry had no TLB entry associated with it.

Conversely, the instructions that modify EPCM entries and result in entries whose VALID field is false start out with valid entries. These instructions are EREMOVE (§ I.5.3.4) and EWB (§ I.5.5.4).

The EPCM entries associated with EPC pages that store Version Arrays (VA, § I.5.5.2) represent a special case for both instructions mentioned above, as these pages are not associated with any enclave. As these pages can only be accessed by the microcode used to implement SGX, they never have TLB entries representing them. Therefore, both EREMOVE and EWB can invalidate EPCM entries for VA pages without additional checks.

EREMOVE only invalidates an EPCM entry associated with an enclave when there is no LP executing in enclave mode using a TCS associated with the same enclave. An EPCM entry can only result in TLB translations when an LP is executing code from the entry's enclave, and the TLB translations are flushed when the LP exits enclave mode. Therefore, when EREMOVE invalidates an EPCM entry, any associated TLB entry is guaranteed to have been flushed.

EWB's correctness argument is more complex, as it relies on the EBLOCK / ETRACK sequence described in § I.5.5.1 to ensure that any TLB entry that may have been created for an EPCM entry is flushed before the EPCM entry is invalidated.

Unfortunately, the SDM pseudocode for the instructions mentioned above leaves out the algorithm used to verify that the relevant TLB entries have been flushed. Thus, we must base our proof on the assumption that the SGX implementation produced by Intel's engineers matches the claims in the SDM. In § 2.4, we propose a method for ensuring that EWB will only succeed when all LPs executing an enclave's code at the time when ETRACK is called have exited enclave mode at least once between the ETRACK call and the EWB call. Having proven the existence of a correct algorithm by construction, we can only hope that the SGX implementation uses our algorithm, or a better algorithm that is still correct.

#### 2.4 Tracking TLB Flushes

This section proposes a straightforward method that the SGX implementation can use to verify that the system software plays its part correctly in the EPC page eviction (§ I.5.5) process. Our method

meets the SDM's specification for EBLOCK (§ I.5.5.1), ETRACK (§ I.5.5.1) and EWB (§ I.5.5.4).

The motivation behind this section is that, at least at the time of this writing, there is no official SGX documentation that contains a description of the mechanism used by EWB to ensure that all Logical Processors (LPs, § I.2.9.4) running an enclave's code exit enclave mode (§ I.5.4) between an ETRACK invocation and a EWB invocation. Knowing that there exists a correct mechanism that has the same interface as the SGX instructions described in the SDM gives us a reason to hope that the SGX implementation is also correct.

Our method relies on the fact that an enclave's SECS (§ I.5.1.3) is not accessible by software, and is already used to store information used by the SGX microcode implementation (§ 2.1.3). We store the following fields in the SECS. tracking and done-tracking are Boolean variables. tracked-threads and active-threads are non-negative integers that start at zero and must store numbers up to the number of LPs in the computer. lp-mask is an array of Boolean flags that has one member per LP in the computer. The fields are initialized as shown in Figure 2.2.

#### ECREATE(SECS)

▷ Initialize the SECS state used for tracking.

- 1 SECS.  $tracking \leftarrow FALSE$

- 2 SECS. done-tracking  $\leftarrow$  FALSE

- $3 \quad SECS . active-threads \leftarrow 0$

- 4 SECS . tracked-threads  $\leftarrow 0$

- 5  $SECS \cdot lp\text{-}mask \leftarrow 0$

Figure 2.2: The algorithm used to initialize the SECS fields used by the TLB flush tracking method presented in this section.

The active-threads SECS field tracks the number of LPs that are currently executing the code of the enclave who owns the SECS. The field is atomically incremented by EENTER (§ I.5.4.1) and ERESUME (§ I.5.4.4) and is atomically decremented by EEXIT (§ I.5.4.2) and Asynchronous Enclave Exits (AEXs, § I.5.4.3). Asides from helping

track TLB flushes, this field can also be used by EREMOVE (§ I.5.3.4) to decide when it is safe to free an EPC page that belongs to an enclave.

As specified in the SDM, ETRACK activates TLB flush tracking for an enclave. In our method, this is accomplished by setting the *tracking* field to TRUE and the *done-tracking* field to FALSE.

When tracking is enabled, tracked-threads is the number of LPs that were executing the enclave's code when the ETRACK instruction was issued, and have not yet exited enclave mode. Therefore, executing ETRACK atomically reads active-threads and writes the result into tracked-threads. Also, lp-mask keeps track of the LPs that have exited the current enclave after the ETRACK instruction was issued. Therefore, the ETRACK implementation atomically zeroes lp-mask. The full ETRACK algorithm is listed in Figure 2.3.

```

▷ Abort if tracking is already active.

1 if SECS . tracking = TRUE

2 then return SGX-PREV-TRK-INCMPL

▷ Activate TLB flush tracking.

3 SECS . tracking ← TRUE

4 SECS . done-tracking ← FALSE

```

5 SECS . tracked-threads  $\leftarrow$  ATOMIC-READ(SECS . active-threads)

6 for  $i \leftarrow 0$  to MAX-LP-ID

ETRACK(SECS)

7 **do** Atomic-Clear(SECS . lp-mask[i])

Figure 2.3: The algorithm used by ETRACK to activate TLB flush tracking.

When an LP exits an enclave that has TLB flush tracking activated, we atomically test and set the current LP's flag in *lp-mask*. If the flag was not previously set, it means that an LP that was executing the enclave's code when ETRACK was invoked just exited enclave mode for the first time, and we atomically decrement *tracked-threads* to reflect

this fact. In other words, *lp-mask* prevents us from double-counting an LP when it exits the same enclave while TLB flush tracking is active.

Once *active-threads* reaches zero, we are assured that all LPs running the enclave's code when ETRACK was issued have exited enclave mode at least once, and can set the *done-tracking* flag. Figure 2.4 enumerates the steps taken during an enclave exit.

```

ENCLAVE-EXIT(SECS)

\triangleright Track an enclave exit.

1 ATOMIC-DECREMENT(SECS . active-threads)

2 if ATOMIC-TEST-AND-SET(

SECS . lp-mask[\text{LP-ID}])

3 then ATOMIC-DECREMENT(

SECS . tracked-threads)

4 if SECS . tracked-threads = 0

5 then SECS . done-tracking \leftarrow \text{TRUE}

```

**Figure 2.4:** The algorithm that updates the TLB flush tracking state when an LP exits an enclave via **EEXIT** or AEX.

Without any compensating measure, the method above will incorrectly decrement *tracked-threads*, if the LP exiting the enclave had entered it after ETRACK was issued. We compensate for this with the following trick. When an LP starts executing code inside an enclave that has TLB flush tracking activated, we set its corresponding flag in *lp-mask*. This is sufficient to avoid counting the LP when it exits the enclave. Figure 2.5 lists the steps required by our method when an LP enters an enclave.

With these algorithms in place, EWB can simply verify that both tracking and done-tracking are TRUE. This ensures that the system software has triggered enclave exits on all LPs that were running the enclave's code when ETRACK was executed. Figure 2.6 lists the algorithm used by the EWB tracking verification step.

Last, EBLOCK marks the end of a TLB flush tracking cycle by clearing the *tracking* flag. This ensures that system software must go through

ENCLAVE-ENTER(SECS)

- 1 Atomic-increment (SECS . active-threads)

- 2 Atomic-set(SECS. lp-mask[LP-ID])

Figure 2.5: The algorithm that updates the TLB flush tracking state when an LP enters an enclave via EENTER or ERESUME.

another cycle of ETRACK and enclave exits before being able to use EWB on the page whose BLOCKED EPCM field was just set to TRUE by EBLOCK. Figure 2.7 shows the details.

Our method's correctness can be easily proven by arguing that each SECS field introduced in this section has its intended value throughout enclave entries and exits.

# 2.5 Enclave Signature Verification

Let m be the public modulus in the enclave author's RSA key, and s be the enclave signature. Since the SGX design fixes the value of the public exponent e to 3, verifying the RSA signature amounts to computing the signed message  $M=s^3 \mod m$ , checking that the value meets the PKCS v1.5 padding requirements, and comparing the 256-bit SHA-2 hash inside the message with the value obtained by hashing the relevant fields in the SIGSTRUCT supplied with the enclave.

This section describes an algorithm for computing the signed message while only using subtraction and multiplication on large non-negative integers. The algorithm admits a significantly simpler implementation than the typical RSA signature verification algorithm, by avoiding the use of long division and negative numbers. The description here is essentially the idea in [Gueron, 2011], specialized for e = 3.

The algorithm provided here requires the signer to compute the  $q_1$  and  $q_2$  values shown below. The values can be computed from the public information in the signature, so they do not leak any additional information about the private signing key. Furthermore, the algorithm

```

EWB-VERIFY(virtual-addr)

```

- 1  $physical-addr \leftarrow TRANSLATE(virtual-addr)$

- $2 \quad epcm\text{-}slot \leftarrow \texttt{EPCM-SLOT}(physical\text{-}addr)$

- 3 **if** EPCM[slot]. BLOCKED = FALSE

- 4 then return SGX-NOT-BLOCKED

- 5  $SECS \leftarrow \text{EPCM-ADDR}($  EPCM[slot]. ENCLAVESECS)

- > Verify that the EPC page can be evicted.

- 6 **if** SECS. tracking = FALSE

- 7 then return SGX-NOT-TRACKED

- 8 **if** SECS. done-tracking = FALSE

- 9 then return SGX-NOT-TRACKED

Figure 2.6: The algorithm that ensures that all LPs running an enclave's code when ETRACK was executed have exited enclave mode at least once.

verifies the correctness of the values, so it does not open up the possibility for an attack that relies on supplying incorrect values for  $q_1$  and  $q_2$ .

$$q_1 = \left\lfloor \frac{s^2}{m} \right\rfloor$$

$$q_2 = \left\lfloor \frac{s^3 - q_1 \times s \times m}{m} \right\rfloor$$

Due to the desirable properties mentioned above, it is very likely that the algorithm described here is used by the SGX implementation to verify the RSA signature in an enclave's SIGSTRUCT (§ I.5.7.1).

The algorithm given by Figure 2.8 computes the signed message  $M = s^3 \mod m$ , while also verifying that the given values of  $q_1$  and  $q_2$  are correct. The latter is necessary because the SGX implementation of signature verification must handle the case where an attacker attempts to exploit the signature verification implementation by supplying invalid values for  $q_1$  and  $q_2$ .

```

EBLOCK(virtual-addr)

1 physical-addr \leftarrow TRANSLATE(virtual-addr)

2 epcm-slot \leftarrow EPCM-SLOT(physical-addr)

3 if EPCM[slot]. BLOCKED = TRUE

4 then return SGX-BLKSTATE

5 if SECS. tracking = TRUE

6 then if SECS. done-tracking = FALSE

7 then return SGX-ENTRYEPOCH-LOCKED

8 SECS. tracking \leftarrow FALSE

9 EPCM[slot]. BLOCKED \leftarrow TRUE

```

Figure 2.7: The algorithm that marks the end of a TLB flushing cycle when EBLOCK is executed.

- 1. Compute  $u \leftarrow s \times s$  and  $v \leftarrow q_1 \times m$ .

- 2. If u < v, abort.  $q_1$  must be incorrect.

- 3. Compute  $w \leftarrow u v$ .

- 4. If  $w \geq m$ , abort.  $q_1$  must be incorrect.

- 5. Compute  $x \leftarrow w \times s$  and  $y \leftarrow q_2 \times m$

- 6. If x < y, abort.  $q_2$  must be incorrect.

- 7. Compute  $z \leftarrow x y$ .

- 8. If  $z \geq m$ , abort.  $q_2$  must be incorrect.

- 9. Output z.

**Figure 2.8:** An RSA signature verification algorithm specialized for the case where the public exponent is 3. s is the RSA signature and m is the RSA key modulus. The algorithm uses two additional inputs,  $q_1$  and  $q_2$ .

The rest of this section proves the correctness of the RSA signature verification.

## 2.5.1 Analysis of Steps 1 - 4

Steps 1-4 in the algorithm check the correctness of  $q_1$  and use it to compute  $s^2 \mod m$ . The key observation to understanding these steps is recognizing that  $q_1$  is the quotient of the integer division  $s^2/m$ .

Having made this observation, we can use elementary division properties to prove that the supplied value for  $q_1$  is correct if and only if the following property holds.

$$0 \le s^2 - q_1 \times m < m$$

We observe that the first comparison,  $0 \le s^2 - q_1 \times m$ , is equivalent to  $q_1 \times m \le s^2$ , which is precisely the check performed by step 2. We can also see that the second comparison,  $s^2 - q_1 \times m < m$  corresponds to the condition verified by step 4. Therefore, if the algorithm passes step 4, it must be the case that the value supplied for  $q_1$  is correct.

We can also plug  $s^2$ ,  $q_1$  and m into the integer division remainder definition to obtain the identity  $s^2 \mod m = s^2 - q_1 \times m$ . However, according to the computations performed in steps 1 and 3,  $w = s^2 - q_1 \times m$ . Therefore, we can conclude that  $w = s^2 \mod m$ .

#### 2.5.2 Analysis of Steps 5 - 8

Similarly, steps 5-8 in the algorithm check the correctness of  $q_2$  and use it to compute  $w \times s \mod m$ . The key observation here is that  $q_2$  is the quotient of the integer division  $(w \times s)/m$ .

We can convince ourselves of the truth of this observation by using the fact that  $w=s^2 \mod m$ , which was proven above, by plugging in the definition of the remainder in integer division, and by taking advantage of the distributivity of integer multiplication with respect to addition.

$$\left\lfloor \frac{w \times s}{m} \right\rfloor = \left\lfloor \frac{(s^2 \mod m) \times s}{m} \right\rfloor$$

$$= \left\lfloor \frac{(s^2 - \lfloor \frac{s^2}{m} \rfloor \times m) \times s}{m} \right\rfloor$$

$$= \left\lfloor \frac{s^3 - \lfloor \frac{s^2}{m} \rfloor \times m \times s}{m} \right\rfloor$$

$$= \left\lfloor \frac{s^3 - q_1 \times m \times s}{m} \right\rfloor$$

$$= \left\lfloor \frac{s^3 - q_1 \times s \times m}{m} \right\rfloor$$

$$= q_2$$

By the same argument used to analyze steps 1-4, we use elementary division properties to prove that  $q_2$  is correct if and only if the equation below is correct.

$$0 \le w \times s - q_2 \times m \le m$$

The equation's first comparison,  $0 \le w \times s - q_2 \times m$ , is equivalent to  $q_2 \times m \le w \times s$ , which corresponds to the check performed by step 6. The second comparison,  $w \times s - q_2 \times m < m$ , matches the condition verified by step 8. It follows that, if the algorithm passes step 8, it must be the case that the value supplied for  $q_2$  is correct.

By plugging  $w \times s$ ,  $q_2$  and m into the integer division remainder definition, we obtain the identity  $w \times s \mod m = w \times s - q_2 \times m$ . Trivial substitution reveals that the computations in steps 5 and 7 result in  $z = w \times s - q_2 \times m$ , which allows us to conclude that  $z = w \times s \mod m$ .

In the analysis for steps 1-4, we have proven that  $w=s^2 \mod m$ . By substituting this into the above identity, we obtain the proof that the algorithm's output is indeed the desired signed message.

$$z = w \times s \mod m$$

$$= (s^2 \mod m) \times s \mod m$$

$$= s^2 \times s \mod m$$

$$= s^3 \mod m$$

## 2.5.3 Implementation Requirements

The main advantage of SGX's RSA signature verification is that it relies on the implementation of very few arithmetic operations on large integers. The maximum integer size that needs to be handled is twice the size of the modulus in the RSA key used to generate the signature.

Steps 1 and 5 use large integer multiplication. Steps 3 and 7 use integer subtraction. Steps 2, 4, 6, and 8 use large integer comparison. The checks in steps 2 and 6 guarantee that the results of the subtractions performed in steps 3 and 7 will be non-negative. It follows that the algorithm will never encounter negative numbers.

## 2.6 Key Hierarchy and Derivation

According to Intel's patents, the SGX implementation relies on a complex key derivation process rooted on global secret keys in the CPU circuitry, and on secrets embedded in the processor's eFUSEs. eFUSE information can be extracted efficiently (Chipworks quotes \$50-250k for extracting the entire eFUSE contents from an Intel i5 processor), so some of the eFUSE secrets are encrypted with a master key (referred to as a "global wrapping logic key" in the patents).

The SGX patents describe two "logic keys" embedded in the CPU's circuitry, which are the same for all CPUs in a stepping, making them essentially global keys. The global wrapping logic key (GWK) is a 128-bit AES key, and it is used to encrypt a subset a 256-bit A.x value used to re-create the CPU's EPID key, and a 128-bit  $pre\text{-}seed\ key\ \theta$ . The eFUSEs also contain a 128-bit  $pre\text{-}seed\ key\ 1$  and a 32-bit EPID group ID, which are stored in cleartext.

[Shanbhogue et al., 2015], which describes mechanisms for protecting SGX keys in the presence of hardware debuggers, states that some hardware secrets are stored in "metal tie-ups and tie-downs", while other secrets are stored in e-fuses or in *physically unclonable function* (PUF) circuits [Gassend et al., 2002]. [Brickell and Li, 2014, Gotze et al., 2014a] state that the GWK is embedded into a chip using "metal tie-ups and tie-downs", and is shared by all chips manufactured from the same mask set.

The SGX patents state that encrypting the eFUSE secrets by the logic key makes them harder to extract via hardware monitoring tools, and protects them while in transit to the CPU during the manufacturing process. This assumes that it is very expensive to obtain the global key from a CPU, by virtue of the low feature size. [Gotze et al., 2014a] expresses concerns that the GWK can be reverse-engineered.

[Gotze et al., 2014a,b] disclose that SGX processors also employ a PUF, which generates a symmetric key that is used during the provisioning process. Specifically, at an early provisioning stage, the PUF key is encrypted with the GWK and transmitted to the key generation server. At a later stage, the key generation server encrypts the chip's fuse key material with the PUF key, and transmits it to the chip. The PUF key increases the cost of obtaining a chip's fuse key material, as an attacker must compromise both provisioning stages in order to be able to decrypt the fuse key material.

The SDM [Int, 2015b] mentions a 16-byte CPU security version number (SVN), which contains the version numbers of various TCB components, and is a source in the key derivation process. The patents further specify that the SVN register is made up of (most likely 8-bit) sections that contain the SVNs of each layer in the SGX initialization process, and that each initialization step sets the corresponding section to its SVN, and then locks it for the duration of the power-up cycle.

Intel's patents disclose that the key derivation process uses 128-bit AES in ECB mode as a pseudo-random function (PRF). When an SVN is an input to a key derivation process, a *PRF loop* is used, where the PRF is applied to a constant.

[Anati et al., 2013] confirms that the attestation uses Intel's EPID [Brickell and Li, 2009] group signature scheme.

The Intel patents indicate that EREPORT's KeyID is initialized to a random value on each processor power cycle, and is incremented after  $2^{32}$  AES operations that use the value. They also indicate that each EREPORT may increment the KeyID by 1.

Neither the ISCA 2015 SGX tutorial nor the SDM mention the DAK described above. However, an Intel-sponsored book on the Management Engine (ME) [Ruan, 2014], which is the closest thing available to an official documentation for the ME, mentions that the ME contains e-fuses that store an EPID key which is used by the virtual TPM's software attestation feature.

Many aspects in the description of the ME's EPID key match the SGX patents' depiction of the DAK. Both sources use the same compressed representation of the EPID key. Also, both documents mention that the EPID key is encrypted with an AES key.