# CACHE-BASED SIDE CHANNELS: MODERN ATTACKS AND DEFENSES

# BY

# MENGJIA YAN

## DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2019

# Urbana, Illinois

# Doctoral Committee:

Professor Josep Torrellas, Chair

Assistant Professor Christopher W. Fletcher

Professor Darko Marinov

Professor Joel Emer, Massachusetts Institute of Technology/NVIDIA

Professor Ruby B. Lee, Princeton University

Assistant Professor Adam Morrison, Tel Aviv University

#### ABSTRACT

Security and trustworthiness are key considerations in designing modern processor hardware. It has been shown that, among various data leakage attacks, *side channel attacks* are one of the most effective and stealthy ones. In a side channel attack, an attacker can steal encryption keys, monitor keystrokes, or reveal a user's personal information by leveraging the information derived from the side effects of a program's execution. These side effects include timing information, micro-architecture states, power consumption, electromagnetic leaks and even sound.

This thesis studies the important type of micro-architecture side channel attacks that exploit the shared cache hierarchies. Recently, we have witnessed ever more effective cachebased side channel attack techniques and the serious security threats posed by these attacks. It is urgent for computer architects to redesign processors and fix these vulnerabilities promptly and effectively.

We address the cache-based side channel security problems in two ways. First, as modern caches are temporally and spatially shared across different security domains, the shared cache hierarchy offers a broad attack surface. It provides attackers a number of ways to interfere with a victim's execution and cache behavior which, in turn, significantly increase side channel vulnerabilities. We study the role of cache interference in different cache attacks and propose effective solutions to mitigate shared cache attacks by limiting malicious interference.

According to our analysis, in a multi-level cache hierarchy, creating "inclusion victims" is the key in a successful attack, since they give an attacker visibility into a victim's private cache. Based on this important observation, we present a secure hierarchy-aware cache replacement policy (SHARP) to defeat cache attacks on inclusive cache hierarchies by eliminating inclusion victims. In addition, we show that inclusion victims also exist in non-inclusive cache hierarchies, and that the non-inclusive property is insufficient to stave off cache-based side channel attacks. We design the first two conflict-based cache attacks targeting the directory structure in a non-inclusive cache hierarchy. We prove that the directory structure is actually the unified attack surface for all types of cache hierarchies, including inclusive, non-inclusive and exclusive ones. To address this problem, we present the first scalable secure directory design (SecDir) to eliminate inclusion victims by restructuring the directory organization.

Second, cache-based side channel attacks play an important role in *transient* execution attacks, leading to arbitrary information leakage and the violation of memory isolation.

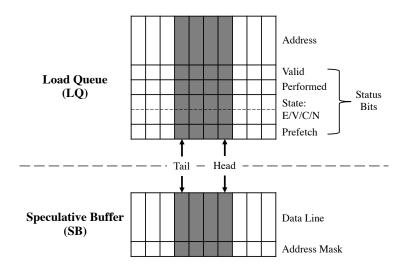

Specifically, in transient execution attacks, speculative execution induces the execution of instructions in incorrect paths. Such instructions potentially access secrets, leaving side effects in the cache hierarchy before being squashed. We study how to effectively defend against transient execution attacks on cache hierarchies by hiding the side effects of transient load instructions. We call our scheme "Invisible Speculation" (*InvisiSpec*). It is the *first* robust hardware defense mechanism against transient cache-based side channel attacks for multiprocessors.

For my family.

#### ACKNOWLEDGMENTS

This Ph.D. journey is a precious chapter in my life. I am really happy that, after the six years, I have become a more mature researcher and a more persistent person, and I am still passionate about research and life as before. This Ph.D. journey is full of challenges. I could not make it here without the support and help from many people.

First and foremost, I am grateful to my advisor Josep Torrellas. Josep kindly accepted me as a member in the i-acoma research group, when I was naive about research and had a very weak technical background. I learned almost everything about research from him. Recently, I even found myself sometimes thinking in his way and speaking in his tone. Besides all the guidance I got from him, I really appreciate that he was extremely patient with me. He always patiently listened to my ideas, even the premature and incorrect ones, and constantly encouraged me to speak up during discussions. Especially in the first three years, when I made slow progress and felt upset, Josep provided a supportive environment for me to develop skills and build confidence. Learning how to do research can take a very long time. If Josep had not been that nice to me, and if he had not allowed me to take time, I might have given up. Thanks Josep for all the support.

Second, I would like to thank Chris Fletcher, my mentor and closest collaborator. My research productivity suddenly boosted up after Chris joined the University of Illinois at Urbana-Champaign (UIUC). It was great fun to work with Chris on all the projects. Many times when I came up with a small idea and went to discuss with Chris, he could see strong merits in the idea and provide insightful feedback to transform the idea into a revolutionary one. He is quick-minded, super positive and full of energy. More importantly, he knows the magic of turning research into an enjoyable thing. Thanks Chris for showing me this new aspect of research.

Besides, I am fortunate to have Adam Morrison, Joel Emer, Ruby Lee and Darko Marinov serve on my thesis committee. All of them played important roles in my Ph.D. journey. Adam has been a very close collaborator and has provided a lot of valuable feedback to my work. He was the first person who pointed out the consistency problem in an InvisiSpec-style defense solution. Joel is my role model. His Gandalf-style research philosophy and noble character have influenced me ever since I worked with him. Ruby's pioneering works on cache-based side channels have led me to this research problem and inspired multiple of my works. I had a lot of fun working with Darko, and I was always impressed by his humour and unique style of mentoring. If possible, I wish I could keep working and learning from

them in the future.

Next, I would like to thank my colleagues in the i-acoma group. It was great fun to spend the six years with these nice people, namely Bhargava Gopireddy, Dimitrios Skarlatos, Yasser Shalabi, Thomas Shull, Jiho Choi, Wooil Kim, Raghavendra Pothukuchi, Antonio Garcia, Zhangxiaowen Gong, Azin Heidarshenas, Apostolos Kokolis and Serif Yesil. Together, we fought for paper deadlines and "cried" for paper rejections. I'm grateful to them for being my colleagues and friends. I would like to especially thank Yasser, Bhargava and Tom for helping me submit my first MICRO paper. In the last several hours before the MICRO submission deadline in 2016, I could not do much since I got a serious headache. They were nice enough to offer help, working on my paper until the last minute to fix as many problems as possible. The submission could not have happened without their generous help. Thanks Yasser, Bhargava and Tom. I hope the young students and future students will also be able to leverage the support and continue the great work in the i-acoma group.

I also want to express my appreciation to a lot of people outside of the i-acoma group who have helped me to complete this thesis. I would like to thank Fangfei Liu, who impressed me with her passion about side-channel attacks and defenses when we first met. A brief conversation with her triggered my initial interest in this problem. I thank Neil Wen and Read Sprabery for being co-authors of my papers. They are amazing and I learned a lot about system and software engineering from them. I thank Professor Michael Bailey for offering the best security course (CS461) in the department. The course showed me the fascinating world of security problems. Also, I would like to thank Nima Honarmand for his help in the very first project that I participated in. Nima's quest for perfection turned out to be the best training for me on conducting academic experiments and data collection. Special thanks to my dear friends, Tarun Prabhu, Bilge Acun, Pinlei Chen, Yunhui Long and Ying Chen, who helped me survive the extremely cold winters in Champaign.

Finally, I would like to thank my boyfriend Xuhao and my parents. Xuhao and I have been long-distance with twelve-hour time difference for the past four years, but he made me feel that he was always around me. He encouraged me to think bigger and motivated me to work harder. I might have delayed my graduation without his encouragement. Also, I would like to thank my parents for their unconditional love and support. Words cannot express my appreciation for what they have done for me since my birth. I know that they are always proud of me no matter what I achieve.

# TABLE OF CONTENTS

| CHAPT | TER 1 INTRODUCTION 1                                          |

|-------|---------------------------------------------------------------|

| 1.1   | The Problem: Cache-Based Side Channel Attacks                 |

| 1.2   | Challenges in Defending Against Cache Attacks                 |

| 1.3   | Thesis Contributions and Organization                         |

| СНАРТ | TER 2 BACKGROUND AND RELATED WORK 8                           |

| 2.1   | Modern Processor and Cache Organization                       |

| 2.2   | Cache-Based Side Channel Attacks                              |

| 2.3   | Countermeasures Against Cache-Based Side Channel Attacks      |

| 2.4   | Countermeasures Against Transient Execution Attacks           |

| СНАРТ | TER 3 SHARP                                                   |

| 3.1   | Attack Analysis                                               |

| 3.2   | SHARP Design                                                  |

| 3.3   | Discussion                                                    |

| 3.4   | Evaluation                                                    |

| 3.5   | Conclusion                                                    |

| СНАРТ | TER 4 DIRECTORY ATTACKS                                       |

| 4.1   | The Challenge of Non-Inclusive Caches                         |

| 4.2   | Constructing Eviction Sets                                    |

| 4.3   | Reverse Engineering the Directory Structure                   |

| 4.4   | Attack Strategies                                             |

| 4.5   | Evaluation                                                    |

| 4.6   | Conclusion                                                    |

| СНАРТ | TER 5 SECDIR                                                  |

| 5.1   | Attack Analysis                                               |

| 5.2   | SecDir Design Overview                                        |

| 5.3   | SecDir Directory Operation                                    |

| 5.4   | Victim Directory Design                                       |

| 5.5   | Dicussion: VD Timing Considerations                           |

| 5.6   | A Possible Design of SecDir                                   |

| 5.7   | Evaluation                                                    |

| 5.8   | Conclusion                                                    |

| СНАРТ | TER 6 INVISISPEC                                              |

| 6.1   | Understanding Transient Execution Attacks Comprehensively 103 |

| 6.2   | InvisiSpec Design                                             |

| 6.3   | Detailed InvisiSpec Design                                    |

| 6.4   | Security Analysis                         | ر21         |

|-------|-------------------------------------------|-------------|

| 6.5   | Evaluation                                | 22          |

| 6.6   | Conclusion                                | .30         |

| СНАРТ | ER 7 CONCLUSION                           | 131         |

| APPEN | DIX A CACHE TELEPATHY                     | 133         |

|       | Background on DNN and DNN Privacy Attacks |             |

| A.2   | Threat Model                              | 136         |

| A.3   | Attack Overview                           | 137         |

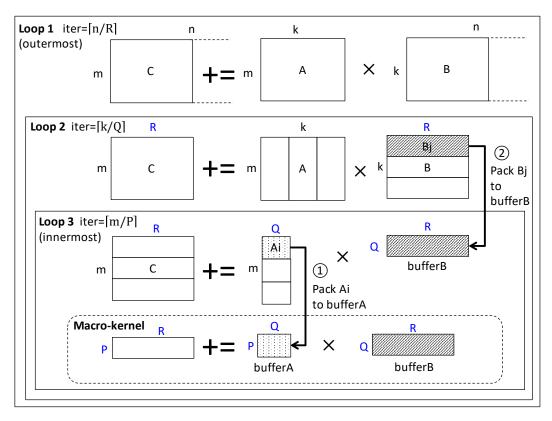

| A.4   | Mapping DNNs to Matrix Parameters         | 139         |

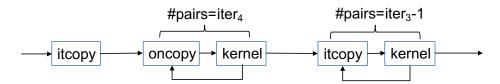

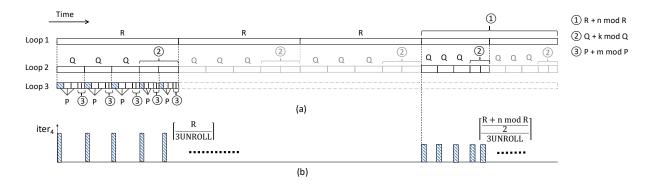

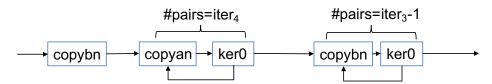

| A.5   | Attacking Matrix Multiplication           | ι45         |

| A.6   | Generalization of the Attack on GEMM      | 51          |

| A.7   | Experimental Setup                        | <u>د</u> 52 |

| A.8   | Evaluation                                | 153         |

| A.9   | Countermeasures                           | 61          |

| A.10  | Conclusion                                | 61          |

| REFER | ENCES 1                                   | 163         |

#### CHAPTER 1: INTRODUCTION

Security and trustworthiness are key considerations in designing modern processor hardware. It has been shown that, among various data leakage attacks, side channel attacks are one of the most effective and stealthy ones. The potential threats of side channel attacks were discussed by Butler W. Lampson in the early 1970s [1]. However, the problem did not get high attention in the computer architecture community until the late 2000s, when the first cache-based side channel attack successfully broke the AES encryption algorithm [2]. In the beginning of 2018, these attacks suddenly became an urgent threat after the disclosure of the first two transient execution attacks, i.e., Spectre [3] and Meltdown [4]. These attacks can completely break the fundamental software security mechanism: memory isolation. Important secret information can be leaked in these attacks, such as encryption keys in a cryptography algorithm, passwords stored in a password manager or browser, personal photos, emails, and personal health information.

To the best of our knowledge, there does not exist a strict definition for side channel attacks. Generally speaking, in computer security, a side channel attack leaks information from the *side effects* of a victim program's execution on a computer system. These side effects include timing information, micro-architecture states, power consumption, electromagnetic leaks, and even sound. For instance, in a keyboard acoustic side channel attack, an adversary learns what a victim is typing based on the sound produced by keystrokes.

This thesis is concerned with the important type of side channel attack that exploits the shared cache hierarchies. This attack is called *cache-based side channel attack* (or *cache attack* for short). Among all the side channels, caches offer one of the most broad and problematic attack surfaces. In a cache-based side channel attack [5–7], an attacker obtains secret information from a victim based on the interaction between victim's execution and cache states. More specifically, most attacks exploit the difference in the access times of cache hits and misses. It is extremely challenging to eliminate cache side channels efficiently, mainly because caches are essential to processor performance, and timing difference is an intrinsic property of cache structures [8].

#### 1.1 THE PROBLEM: CACHE-BASED SIDE CHANNEL ATTACKS

There exist many variations of cache-based side channel attacks. To better understand what exactly a cache attack is, we start with an intuitive example, and then summarize the common attack procedure.

**Algorithm 1.1:** Victim code in a cache-based side channel attack example.

**Input:** secret s, public array parray

- 1 Function victim(s):

- $\mathbf{2} \mid \text{load } parray[s]$

- 3 End Function

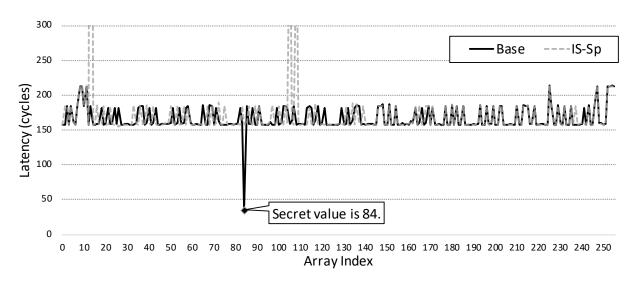

In our example, the attacker and the victim are in different security domains. The attacker and the victim share a public data array parray, but only the victim can access the secret value s. The size of each element in parray is the same as the size of a cache block. Algorithm 1.1 lists the snippet of code executed by the victim. The victim uses the secret value s as an index to access the public array parray. Assume that the cache is initially empty and all the elements in parray are located in main memory. When the victim executes the memory access instruction (line 2), the processor inserts the cache line addressed by parray[s] into the cache. As a result, the cache state is changed by the victim in a secret-dependent way.

The attacker in this example tries to steal the secret value s using a cache-based side channel attack. The attacker accesses each element in parray and measures the access latency. Since there exists a big timing difference between a cache hit and a cache miss, the attacker can use the access latency to infer the cache state. Specifically, the attacker will get a short access latency when accessing parray[s], and a long latency when accessing other elements. Therefore, the index that exhibits the shortest access latency is the secret value s.

The above example shows that a cache-based side channel attack consists of two procedures: 1) a victim program performs secret-dependent memory accesses, which change the state of the cache; and 2) an attacker program extracts the secret by detecting the state of the cache. All the cache attacks follow the two procedures, while the concrete actions in the two procedures can vary a lot. For example, the secret-dependent access performed by the victim can be an instruction in a correct execution path, or it can be an instruction in an incorrect execution path that is speculatively executed and has to be squashed later. The latter case happens in a transient execution attack. In terms of the detection strategies, an attacker could detect the cache state based on the latency of a single cache access, the latency of multiple accesses, or the execution time of the victim program. Moreover, it has been shown that attackers can detect not only cache occupancy state, but also coherence state [9] and replacement information state [10].

#### 1.2 CHALLENGES IN DEFENDING AGAINST CACHE ATTACKS

Given the variety of cache-based side channel attacks, it is necessary to understand the root cause of the attacks and the main challenges in designing effective defense solutions.

Micro-architecture side channels are due to processor optimizations that create detectable side effects. Processor hardware has traditionally been aggressively optimized for performance and energy efficiency, without taking security into consideration. Furthermore, many optimizations are made transparent to the software for programmability purposes. These optimizations have made processors fast and efficient, but they have also introduced many exploitable side effects, such as timing variations. An obvious example is caches, which are fast on-chip storage structures. They were introduced to improve performance and naturally created faster paths to access data. However, the faster access paths that we leverage for performance are exactly the exploitable side effects used in most cache-based side channel attacks.

We now consider the critical challenges in defeating cache-based side channel attacks. From a hardware design perspective, modern caches are spatially and temporally shared by different programs, regardless of whether they are in the same security domain or not. Thus, shared caches have become a broad attack surface and provide attackers with a number of ways to interfere with the victim's execution.

Given the recent expansion of cloud computing and web applications, it has never been easier than today for attackers to achieve co-location with victims in the same machine. On one hand, popular cloud platforms, such as Amazon EC2 [11], Google Cloud [12], and Microsoft Azure [13], provide convenient ways for users to access computing resources. Many companies are using cloud services to deploy their applications, given the configuration flexibility and reduced maintenance cost involved. Even though cloud computing uses virtual machines [14] and containers [15] to provide software-level isolation, the cache hardware is largely unaware of security domains. On the other hand, modern web applications are becoming dynamic and interactive, hosting programs written in high-level languages. It has become easy for potentially malicious applications to run on users' private desktops or mobile devices, as they merely require the user to click a link to access a website. Even though these applications are guarded by software isolation techniques and execute within sandboxes, the domain information is not communicated to the cache management modules in hardware. In short, both trends give attackers good chances to co-locate in the same computing machine as victim applications [16,17], and achieve temporal and spatial sharing of cache hierarchies.

Obviously, a potential solution to close this channel is to disable cache sharing. Unfor-

tunately, trivially disabling sharing can cause system resource underutilization and serious performance overhead. Disabling spatial sharing seriously hurts system throughput, as the maximum number of parallel virtual processes is limited by the physical resources. Disabling temporal sharing can significantly increase latency, as cache states have to be reset upon every switch of security domains.

From a software development perspective, a potential solution to close the channel is to make cache access traces oblivious of any secret. For example, a vulnerable program can be transformed by adding redundant memory accesses, so that cache states are changed in the same way irrespective of the value of the secret. Even though this approach generally suffers from serious performance overhead, it is effective and it has been used to fix vulnerabilities in several important cryptography algorithms. However, recent transient execution attacks have called such software defense solutions into question.

In transient execution attacks, attackers exploit hardware speculation to cause the execution of instructions in incorrect paths. These instructions potentially access secrets, leaving side effects on the cache hierarchy before being squashed. These instructions are outside of the scope of what programmers and compilers can reason about. Without controlling which memory access instructions are executed by the processor, software-only defenses become ineffective.

In summary, we consider that the challenge of defending against cache-based side channel attacks is two-fold. From the hardware design perspective, caches offer a broad attack surface mainly due to the temporal and spatial sharing of cache hierarchies across different security domains. From the software development perspective, software defense solutions become ineffective because speculative execution can cause execution to proceed in ways that were not intended by the programmer or compiler.

#### 1.3 THESIS CONTRIBUTIONS AND ORGANIZATION

Given the aforementioned challenge in defending against cache-based side channel attacks, this thesis proposes secure hardware processor designs to effectively and efficiently address the side channel vulnerabilities of modern cache hierarchies.

This thesis makes two main contributions. First, we study the role of cache interference in different cache attacks and propose effective solutions to mitigate shared cache attacks by limiting malicious interference. Caches offer a broad attack surface, mainly because modern cache hierarchies are temporally and spatially shared by different security domains. The shared cache hierarchy provides attackers a number of ways to interfere with a victim's

execution and cache behavior.

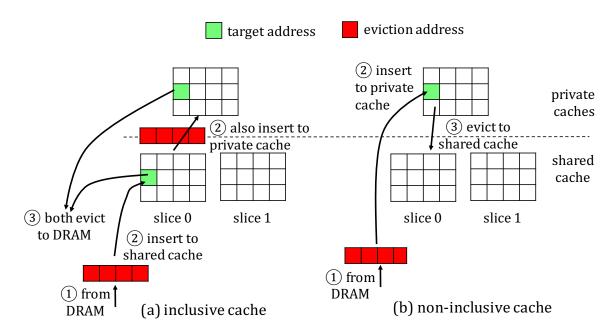

Based on our analysis, in a multi-level cache hierarchy, evicting lines from the private cache of the victim (i.e., creating "inclusion victims") is the key in a successful attack. This is because inclusion victims give an attacker visibility into a victim's private cache and provide useful information. Based on this important observation, we present a secure hierarchy-aware cache replacement policy (SHARP), which defeats cache attacks on inclusive cache hierarchies by eliminating inclusion victims. In addition, we show that inclusion victims also exist in non-inclusive cache hierarchies, and that the non-inclusive property is insufficient to stave off cache-based side channel attacks. We design the first two conflict-based cache attacks targeting the directory structure in a non-inclusive cache hierarchy. We prove that the directory structure is actually a unified attack surface for all types of cache hierarchies, including inclusive, non-inclusive and exclusive ones. To address this problem, we present the first scalable secure directory (SecDir) design to eliminate inclusion victims by restructuring the directory organization.

Second, we study how to effectively defend against transient (i.e., speculative) execution attacks in the cache hierarchies. Cache-based side channel attacks play an important role in transient execution attacks, leading to arbitrary information leakage and the violation of memory isolation. Specifically, in transient execution attacks, speculative execution causes the execution of instructions in incorrect paths. We present "Invisible Speculation" (InvisiSpec) to hide the side effects of transient load instructions. It is the first robust hardware defense mechanism against transient cache-based side channel attacks for multiprocessors.

The thesis is organized as follows.

Chapter 2 – Background and Related Work This chapter starts by providing a brief background on modern micro-architecture features and cache hierarchy designs. We then describe a generalized attack schema of cache-based side channel attacks. Based on key procedures in the attack schema, we go through a deep dive of two taxonomies. Finally, we review related work on countermeasures against cache attacks.

Chapter 3 – SHARP This chapter presents a secure hierarchy-aware cache replacement policy (SHARP) that enables an efficient and practical defense mechanism against cachebased side channel attacks for inclusive cache hierarchies. We observe that when a cross-core cache attack happens, the attacker evicts the victim's line from the shared cache, and also from the private cache of the victim process, creating an "inclusion victim". Creating inclusion victims is the key for the attacker to gain visibility into the victim's private cache. Consequently, to disable cache attacks, we propose to alter the line replacement algorithm of

the shared cache to prevent a process from creating inclusion victims in the caches of cores running other processes. SHARP is an efficient defense mechanism, which requires minor hardware modifications and induces negligible average performance degradation. The work is published in ISCA 2017 [18].

Chapter 4 – Directory Attacks This chapter presents the first two directory-based side channel attacks on non-inclusive cache hierarchies. As modern caches move away from inclusive cache hierarchies to non-inclusive ones, previous cache attack strategies have been called into doubt, mainly due to the assumption that attackers should be unable to create "inclusion victims". However, we find that, in a non-inclusive cache, inclusion victims can be created via directory conflicts. We present *directory attacks* and prove that the directory can be used to bootstrap conflict-based cache attacks on any cache hierarchy, including inclusive, non-inclusive and exclusive ones. We demonstrate the directory attacks by extracting key bits during RSA operations in GnuPG on a state-of-the-art non-inclusive Intel Skylake-X server. The work appears in SP 2019 [19].

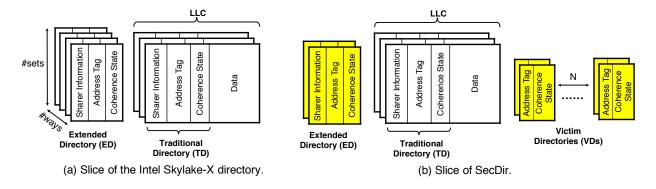

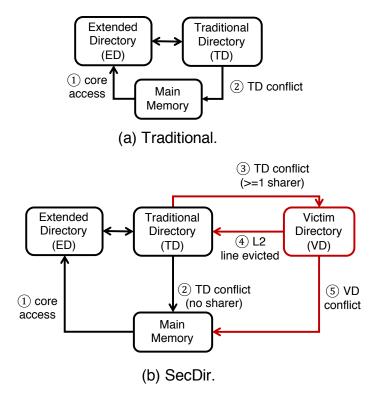

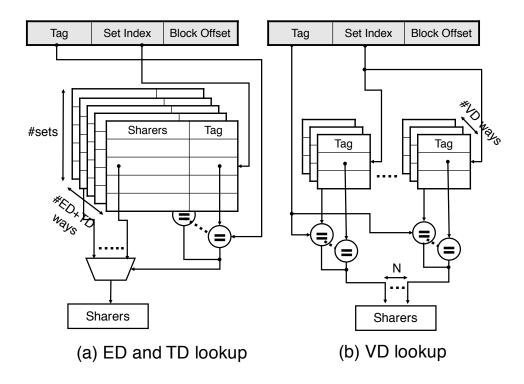

Chapter 5 – SecDir This chapter presents the first design of a scalable secure directory (SecDir). In the previous chapter, we showed the need to redesign directories for security. However, in an environment with many cores, it is hard or expensive to block directory interference. To address this problem, we propose SecDir, a secure directory design, to eliminate inclusion victims by restructuring the directory organization. SecDir takes part of the storage used by a conventional directory and re-assigns it to per-core private directory areas used in a victim-cache manner called Victim Directories (VDs). The partitioned nature of VDs prevents directory interference across cores, defeating directory side channel attacks. We show that SecDir has a negligible performance overhead and is area efficient. The work is published in ISCA 2019 [20].

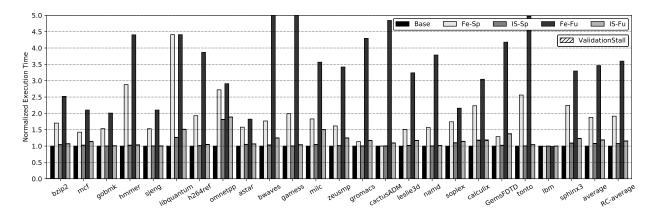

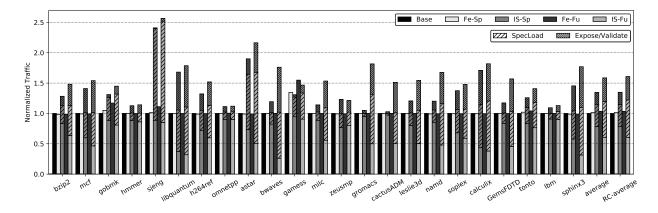

Chapter 6 – InvisiSpec This chapter presents the first robust hardware defense mechanism against transient cache-based side channel attacks for multiprocessors. It has been shown that hardware speculation offers a major surface for micro-architectural side channel attacks. Unfortunately, defending against speculative execution attacks is challenging. We propose InvisiSpec, a novel strategy to defend against transient cache attacks in multiprocessors by making speculation invisible in the data cache hierarchy. In InvisiSpec, unsafe speculative loads read data into a speculative buffer, without modifying the cache hierarchy. When the loads become safe, InvisiSpec makes them visible to the rest of the system. We show that InvisiSpec has modest performance overhead and is able to defend against

future transient execution attacks where any speculative load can pose a threat. This work is published in MICRO 2018 [21].

Chapter 7 – Conclusion This chapter summarizes the results of the thesis and discusses future research directions.

Appendix A – Cache Telepathy This appendix presents another example of cache-based side channel attacks that target Deep Neural Networks (DNNs). A DNN's architecture (i.e., its hyper-parameters) broadly determines the DNN's accuracy and performance, and is often confidential. We propose Cache Telepathy, an efficient mechanism to help obtain a DNN's architecture using the cache side channel. We evaluate our attack by attacking VGG and ResNet DNNs. We show that our attack is effective in helping obtain the architectures by very substantially reducing the search space of the target DNN architectures. This work appears in USS 2020 [22].

#### CHAPTER 2: BACKGROUND AND RELATED WORK

#### 2.1 MODERN PROCESSOR AND CACHE ORGANIZATION

# 2.1.1 Memory Hierarchy and Basic Cache Structures

Modern high-performance processors contain multiple levels of caches that store data and instructions for fast access. The cache structures closer to the core, such as the L1, are the fastest, and are called higher-level caches. The ones farther away from the core and closer to main memory are slower, and are called lower-level caches. High-performance processors typically feature two levels of private caches (L1 and L2), followed by a shared L3 cache—also referred to as LLC for last-level cache.

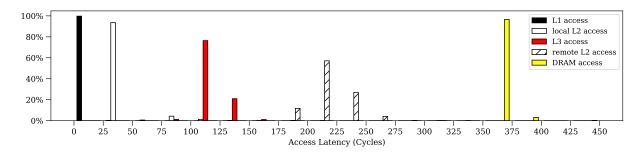

The L1 cache is designed to be small (e.g., 32-64KB) and to respond very fast, typically within a few cycles. The L2 cache is slightly bigger (e.g., 256KB-1MB) and takes around 10-20 cycles. Finally, the LLC is designed to be large (e.g., several to tens of MBs) and has a latency of 40-60 cycles. The LLC latency is still much lower than the main memory access latency, which is on the order of 200-300 cycles.

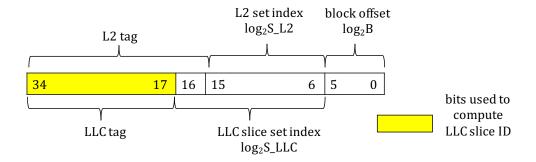

A cache consists of the data array, which stores the data or code, and the tag array, which stores the high-order bits of the addresses of the data or code. The cache is organized in a number of cache lines, each one of size B bytes. The cache is typically set-associative, with S sets and W ways. A cache line occupies one way of a cache set. The set in which a cache line belongs is determined by its address bits. A memory address is shown in Figure 2.1.

Figure 2.1: Example of a memory address broken down into tag, index, and block offset bits. The actual bit field sizes correspond to the L2 and the LLC slice of the Intel Skylake-X system. We refer to the LLC slice set index as the LLC set index in this thesis.

The lower  $\log_2 B$  bits indicate the *block offset* within a cache line. The next  $\log_2 S$  bits form the index of the set that the cache line belongs to. The remaining bits of the address

form the tag. The tags of all the lines present in the cache are stored in the tag array. When a load or store request is issued by the core, the tag array of the L1 cache is checked to find out if the data is present in the cache. If it is a hit, the data is sent to the core. If it is a miss, the request is sent to the L2 cache. Similarly, if the request misses in L2 it is further sent to the LLC and then to main memory. Note that, generally, lower levels of the cache hierarchy have more sets than higher levels. In that case, cache lines that map to different LLC sets may map to the same L2 set, due to the pigeonhole principle.

## 2.1.2 Multi-core Cache Organization

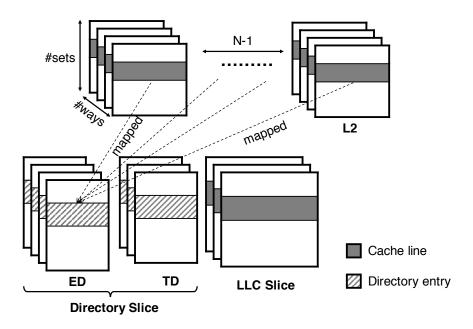

The LLC in a modern multi-core is usually organized into as many slices (partitions) as the number of cores. Such an organization, shown in Figure 2.2, is helpful to keep the design modular and scalable. Each slice has an associativity of  $W_{\text{slice}}$  and contains  $S_{\text{slice}}$  sets.  $S_{\text{slice}}$  is 1/N the total number of sets in the LLC, where N is the number of cores.

| Core 0 | LLC<br>Slice 0 | LLC<br>Slice 4 | Core 4 |

|--------|----------------|----------------|--------|

| Core 1 | LLC<br>Slice 1 | LLC<br>Slice 5 | Core 5 |

| Core 2 | LLC<br>Slice 2 | LLC<br>Slice 6 | Core 6 |

| Core 3 | LLC<br>Slice 3 | LLC<br>Slice 7 | Core 7 |

Figure 2.2: Example of a sliced LLC design with 8 cores.

Processors often use an undocumented hash function to compute the slice ID to which a particular line address maps to. The hash function is designed to distribute the memory lines uniformly across all the slices. In the absence of knowledge about the hash function used, a given cache line can be present in any of the slices. Therefore, from an attacker's perspective, the effective associativity of the LLC is  $N \times W_{\rm slice}$ . The hash function used in Intel's Sandybridge processor has been reconstructed in prior work [23], and found to be an xor of selected address bits. The slice hash function for the Skylake-X is more complex.

We now discuss two important cache design choices, and the tradeoffs behind them.

Inclusiveness The LLC can be either *inclusive*, exclusive, or *non-inclusive* of the private caches. In an inclusive LLC, the cache lines in private L2 caches are also present in the LLC, whereas in an exclusive LLC, a cache line is never present in both the private L2 caches and

in the LLC. Finally, in a non-inclusive LLC, a cache line in the private L2 caches may or may not be present in the LLC.

The inclusive design wastes chip area and power due to the replication of data. Typically, as the number of cores increases, the LLC size must increase, and hence the average LLC access latency increases [24, 25]. This suggests the use of large L2s, which minimize the number of LLC accesses and, therefore, improve performance. However, increasing the L2 size results in a higher waste of chip area in inclusive designs, due to the replication of data. The replication of data can be as high as the L2 capacity times the number of cores. Therefore, non-inclusive cache hierarchies have recently become more common. For example, the most recent server processors by Intel use non-inclusive caches [26, 27]. AMD has always used non-inclusive L3s in their processors [28].

Cache Coherence and Directories When multiple cores read from or write to the same cache line, the caches should be kept coherent to prevent the use of stale data. Therefore, each cache line is assigned a state to indicate whether it is shared, modified, invalid, etc. A few state bits are required to keep track of this per-line state in hardware in the cache tag array or directory.

Two types of hardware protocols are used to maintain cache coherence—snoop-based and directory-based. The snoop-based protocols rely on a centralized bus to order and broadcast the different messages and requests. As the number of cores is increased, the centralized bus quickly proves to be a bottleneck. Therefore, most modern processors use a directory-based protocol, which uses point-to-point communication. In a directory-based protocol, a directory structure is used to keep track of which cores contain a copy of a given line in their caches, and whether the line is dirty or clean in those caches.

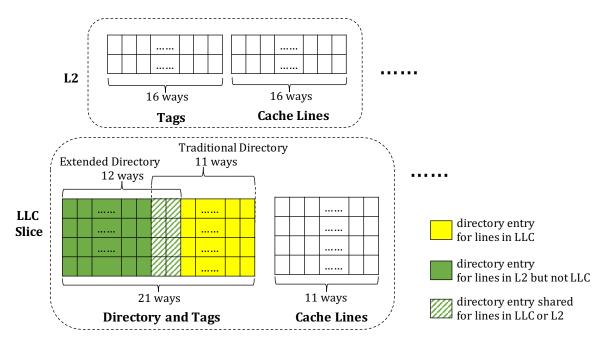

In an inclusive LLC design, the directory information can be conveniently co-located with the tag array of the LLC slice. Since the LLC is inclusive of all the private caches, the directory state of all the cache lines in any private cache is present in such a directory. The hardware can obtain the list of sharer cores of a particular line by simply checking the line's directory entry in the LLC. There is no need to query all the cores. However, the directory in a non-inclusive cache hierarchy design is more complicated.

#### 2.1.3 Out-of-order and Speculative Execution

Dynamically-scheduled processors [29] execute data-independent instructions in parallel, out of program order, and thereby exploit instruction-level parallelism [30] to improve performance. Instructions are *issued* (enter the scheduling system) in program order, *complete*

(execute and produce their results) possibly out of program order, and finally retire (irrevocably modify the architected system state) in program order. In-order retirement is implemented by queueing instructions in program order in a reorder buffer (ROB) [31], and removing a completed instruction from the ROB only once it reaches the ROB head, i.e., after all prior instructions have retired.

Speculative execution is the execution of an instruction before its validity can be made certain. If, later, the instruction turns out to be valid, it is eventually retired, and its speculative execution has improved performance. Otherwise, the instruction will be squashed and the processor's state rolled back to the state before the instruction. (At the same time, all of the subsequent instructions in the ROB also get squashed.) Strictly speaking, an instruction executes speculatively in an out-of-order processor if it executes before it reaches the head of the ROB.

There are multiple reasons why a speculatively-executed instruction may end up being squashed. One reason is that a preceding branch resolves and turns out to be mispredicted. Another reason is that, when a store or a load resolves the address that it will access, the address matches that of a later load that has already obtained its data from that address. Another reason is memory consistency violations. Finally, other reasons include various exceptions and the actual squash of earlier instructions in the ROB.

Memory Consistency and Its Connection to Speculation A memory consistency model (or memory model) specifies the order in which memory operations are performed by a core, and are observed by other cores, in a shared-memory system [32]. When a store retires, its data is deposited into the write buffer. From there, when the memory consistency model allows, the data is merged into the cache. We say that the store is *performed* when the data is merged into the cache, and becomes observable by all the other cores. Loads can read from memory before they reach the ROB head. We say that the load is *performed* when it receives data. Loads can read from memory and be performed out of order—i.e., before earlier loads and stores in the ROB are. Out-of-order loads can lead to memory consistency violations, which the core recovers from using the squash and rollback mechanism of speculative execution [33].

Total Store Order (TSO) [34,35] is the memory model of the x86 architecture. TSO forbids all observable load and store reorderings except store→load reordering, which is when a load bypasses an earlier store to a different address. Implementations prevent observable load→load reordering by ensuring that the value a load reads when it is performed remains valid when the load retires. This guarantee is maintained by squashing a load that has performed, but not yet retired, if the core receives a cache invalidation request for (or suffers

a cache eviction of) the line read by the load. Store—store reordering is prevented by using a FIFO write buffer, ensuring that stores perform in program order. If desired, store—load reordering can be prevented by separating the store and the load with a fence instruction, which does not complete until all prior accesses are performed. Atomic instructions have fence semantics.

Release Consistency (RC) [36] allows any reordering, except across synchronization instructions. Loads and stores may not be reordered with a prior acquire or with a subsequent release. Therefore, RC implementations squash performed loads upon receiving an invalidation of their cache line only if there is a prior non-retired acquire, and have a non-FIFO write buffer.

## 2.2 CACHE-BASED SIDE CHANNEL ATTACKS

Cache-based side channel attacks (cache attacks for short) are serious threats to secure computing, and have been demonstrated on a variety of platforms, from mobile devices [37] and desktop computers [5, 38] to server deployments [6, 39, 40]. Side channel attacks bypass software isolation mechanisms and are difficult to detect. They can be used to steal coarse-grained information such as when a user is typing [37] down to much more fine-grained information such as a user's behavior on the web [41], and even RSA [6, 42] and AES [5,40,43–45] encryption keys. Jakub Szefer [7] presented an in-depth analysis of various micro-architectural side channels and a comprehensive survey of existing defense proposals before the year of 2016.

In this section, we start with a classical cache attack example on the RSA encryption algorithm [42]. We then discuss a generalized attack schema, which is applicable to any cache attack. Based on key procedures in the attack schema, we go through a deep dive of two taxonomies, which define the defense scopes of this thesis.

# 2.2.1 An Example of Cache Attacks

A common type of cache-based side channel attack involves a victim process and an attacker process. It usually consists of an offline phase and an online phase. In the offline phase, the attacker identifies *target addresses*, which are addresses whose access patterns can leak secret information about the victim's program. Target addresses can be identified by analyzing the victim's program manually or with automatic tools [46, 47]. In the online phase, the attacker observes the victim's access patterns on target addresses and deduce the value of secret information.

# **Algorithm 2.1:** Square-and-multiply exponentiation.

```

Input: base b, modulo m, exponent e = (e_{n-1}...e_0)_2

Output: b^e \mod m

1 r = 1

2 for i = n - 1 downto 0 do

3 \begin{vmatrix} r = sqr(r) \\ r = mod(r, m) \end{vmatrix}

5 \begin{vmatrix} if e_i == 1 \text{ then} \\ r = mul(r, b) \\ r = mod(r, m) \end{vmatrix}

8 \begin{vmatrix} end \\ end \\ end \\ end \\ end \\ end \\ end

```

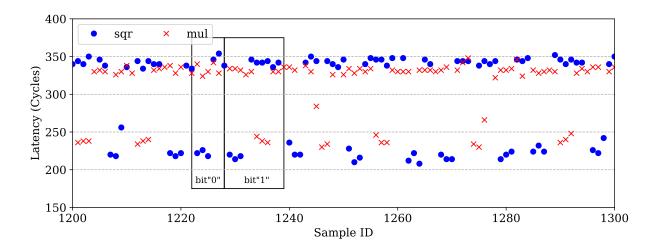

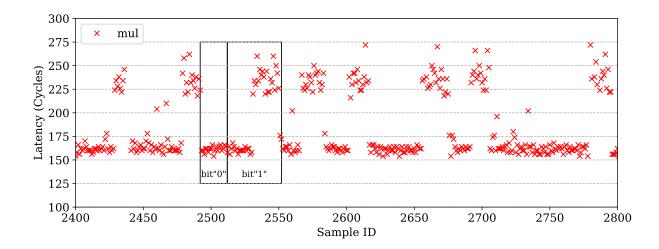

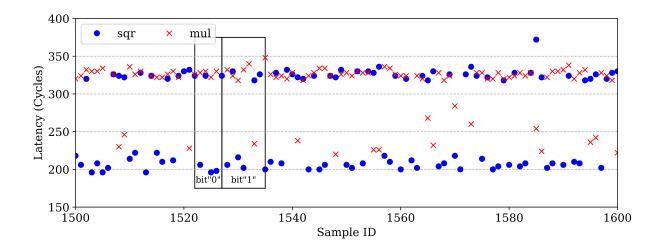

Algorithm 2.1 shows the Square-and-Multiply algorithm [42] from GnuPG version 1.4.13, which is vulnerable to side channel attacks. In the process of computing its output, the algorithm iterates over exponent bits from high to low. For each bit, it performs a sqr and mod operation. Then, if the exponent bit is "1", the algorithm performs a mul and a mod operation that are otherwise skipped. Effective target addresses are the entry points of the sqr function in Line 3 (which tells that the iteration is executed) and of the mul function in Line 6 (which tells that the bit is "1"). By observing access pattern on target addresses, the attacker can recover all the bits in the exponent.

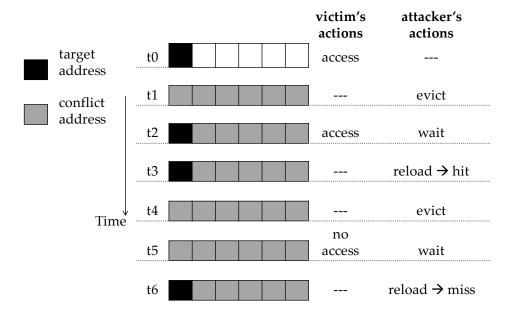

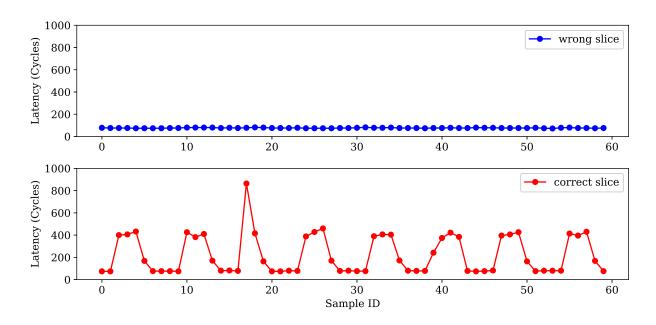

Figure 2.3: Evict+reload attack example.

There exist many different ways for an attacker to observe a victim's cache access patterns. We show an evict+reload [46] attack as an example. In this attack, the attacker and victim processes share the target addresses — possibly because they use a shared library or due to page deduplication [48]. The attack consists of multiple attack cycles, and each attack cycle involves three steps: evict, wait and reload. Figure 2.3 shows a timeline of the state of the 6 cache lines in a set of a 6-way set-associative cache.

At time t0, the victim loads a line with the target address into the cache (black square). At time t1, the attacker accesses 6 different addresses which are mapped to the same cache set. The 6 cache lines are brought into the cache, fill the set (gray squares), and evict the target line from the cache. Next, the attacker idles and waits a designated amount of time to allow the victim to potentially access the target address. In this example, at time t2, the victim does perform an access and brings the target address back to the cache. At time t3, the attacker reloads the target address and measures its access latency. The attacker gets a cache hit, as the victim accessed the target address during the waiting interval.

The next attack cycle repeats the evict, wait, and reload steps (times t4, t5, and t6). This time, the victim does not access the target address and the attacker records a cache miss. The latency of the reload access is longer than before. The example shows that the attacker can figure out whether the victim has accessed the target address during the wait interval based on the access latency of the reload operation. By repeating the attack cycle for multiple times, the attacker can collect a trace of the victim's accesses.

# 2.2.2 Generalized Attack Schema

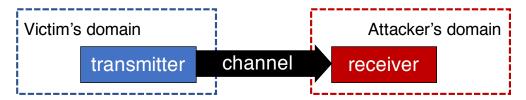

The example above can be generalized as an attack schema<sup>1</sup> shown in Figure 2.4. The schema provides a good abstraction to understand the common procedures that are involved in any cache-based side channel attack.

Figure 2.4: Cache attack schema involves two procedures: 1) the transmitter changes cache states in a secret-dependent way; and 2) the receiver detects the cache states and extracts the secret.

<sup>&</sup>lt;sup>1</sup>The attack schema was first proposed by Kiriansky et al. [10]. The schema can be used to describe side channels other than cache states, such as branch predictors and TLBs.

As shown in Figure 2.4 the attacker application and the victim application exist in different security domains. Memory isolation techniques at the software layer guarantee that the attacker cannot directly access private information inside the victim's domain. However, information can be leaked via the side effects of the victim's execution on the computing system, including the cache hierarchy.

The generalized side channel attack schema involves two procedures. First, a victim program performs secret-dependent memory accesses, which change the states of the cache. We call these memory accesses transmitters. The transmitters modify the cache states based on secret information, forming detectable side channels that can be observed outside of the victim's domain. Second, an attacker program extracts the secret by detecting the states of the cache. The cache states that can be leveraged by attackers include cache occupancy state, coherence state [9] and replacement information state [10].

#### 2.2.3 Classifications of Cache Attacks

We now discuss two taxonomies of cache-based side channel attacks. The taxonomies help define the defense scopes for later chapters.

# Active and Passive Cache Attacks

We classify cache-based side channel attacks into active and passive cache attacks (Table 2.1), based on whether the attack interferes with the channel states before the transmitters execute. In an active cache attack, the attacker leverages the spatial and temporal sharing of cache hierarchies to bring the cache into a desired state before the execution of transmitters, so that it is able to control the way that transmitters interact with the cache. However, a passive attack does not involve such an interfere operation. It has been shown that active attacks are more effective towards a wider range of victim applications than passive ones.

We consider why the interfere operation is important. As discussed in Section 2.2.2, a critical procedure in a successful cache attack is that the transmitters make detectable changes to the cache state. However, many times, without the attacker's interference on the cache state, the transmitters do not cause observable changes. For example, assume that a transmitter tries to access a target cache line to bring it into the cache, but the target line was already present in the cache before the access happens. In this case, the transmitter's execution will not change the cache occupancy state, and thus cannot create a detectable side channel. Active attacks address this problem by interfering with the cache state. For example, in the

evict+reload (Section 2.2.1) attack, every time before the transmitter executes, the attacker resets the cache state by evicting the target line from the cache. In this way, the transmitter will cause a cache miss, and the processor will insert the target line to the cache, leading to detectable changes to the cache occupancy state.

|         | Evict Strategies | Attacks                                             |

|---------|------------------|-----------------------------------------------------|

| Active  | Conflict-based   | prime+probe [2], evict+reload [46], evict+time [38] |

|         |                  | alias-driven attack [49], evict+prefetch [50]       |

| Active  | Flush-based      | flush+reload [48], flush+flush [51],                |

|         |                  | invalidate+transfer [28], flush+prefetch [50]       |

| Passive | _                | cache collision attack [45]                         |

Table 2.1: Classification of cache-based side channel attacks based on whether the attack interferes with the channel states before the transmitters execute.

Generally, an attack cycle in an active attack follows three steps: interfere, wait and analyze.

- 1) Interfere: The attacker brings cache into a desired state so that the execution of transmitters can cause detectable side effects. A common approach is to evict target lines from the level of cache in which they are resident.

- According to the approach used in the *Interfere* step, we can further classify attack strategies into conflict-based and flush-based (Table 2.1). When using conflict-based strategies, the attacker creates cache conflicts to evict cache lines containing target addresses. Specifically, it accesses multiple addresses that map to the same cache set as a target address. Often, these addresses are called *conflict addresses*. When using flush-based strategies, the attacker can access the target addresses e.g., when the target addresses are in shared libraries. The attacker simply executes clflush instructions to evict the target addresses from the cache [52]. clflush guarantees that the addresses are written back to memory and invalidated from the cache.

- 2) Wait: The attacker waits a time period during which the victim may access the target address. The waiting interval of the Wait step is carefully configured [48]. It should be precisely long enough for the victim to access a target address exactly once before the Analyze step. If the interval is too long, the attacker gets only one observation for multiple accesses to the target address by the victim. If the interval is too short, the chances of overlapping the Interfere or Analyze step with the victim's target address access increases. In both cases, the accuracy of the attack decreases.

3) Analyze: the attacker determines whether the target address was accessed in the Wait step. There are several ways to accomplish this goal, including measuring the access time of either the target or conflict addresses (prime+probe [2, 6, 40] and flush+reload [41,48]), measuring the execution time of the victim program (evict+time [5, 38]), or reading values in main memory to see if the writebacks of cache lines have occurred (alias-driven attack [49]).

Different from an active attacker, a passive attacker does not interfere with the cache state when the victim executes. It simply monitors the victim's cache accesses or execution time, which may be affected by reuses or conflicts of cache lines within the victim itself (i.e., self-reuse and self-conflict). An example is the cache-collision attack [45].

The defense mechanisms presented in Chapter 3 and Chapter 5 target active cache attacks. The attacks presented in Chapter 4 are conflict-based cache attacks.

## Non-transient and Transient Cache Attacks

Spectre [3], Meltdown [4] and follow-up attacks [21,53–58] based on speculative execution, or more precisely transient [59] execution, have significantly increased hardware vulnerabilities. Depending on whether the transmitter in a cache attack is a transient instruction, i.e., a speculative instruction bound to squash, we can classify cache-based side channel attacks into transient and non-transient cache attacks.

In a non-transient cache attack, the transmitter execution is intended by the programmer. However, in a transient cache attack, the transmitter is executed due to incorrect speculation and is not intended by the programmer. Such instructions are out the scope of what compilers or programmers can reason about.

Theoretically, memory trace oblivious programming [60] is an effective mitigation towards non-transient cache attacks. Specifically, this technique changes the vulnerable code by adding redundant memory accesses, so that the transmitters will not cause secret-dependent cache state changes. However, the transmitters used in transient cache attacks can not be controlled by the software. Thus, traditional software defense solutions become ineffective in transient cache attacks.

The defense mechanism in Chapter 6 targets transient cache attacks.

#### 2.3 COUNTERMEASURES AGAINST CACHE-BASED SIDE CHANNEL ATTACKS

In this section, we review related work on defending against side channel attacks on shared cache hierarchies, followed by a discussion on detection techniques. We classify defense mechanisms into two categories, isolation-based and randomization-based.

**Isolation-based Defenses** Isolation-based defense mechanisms rely on cache partitioning techniques to block unintended cache interference. There are two types of cache-partitioning techniques depending on the total number of partitions required.

The first type partitions the cache into as many regions as the number of security domains. Static way-partition [61] provides isolation by statically assigning certain cache ways to each security domain. Unfortunately, this approach can introduce serious performance overhead, since the cache cannot be dynamically shared. Moreover, when the number of cores is higher than the cache associativity, some cores cannot get a cache partition, resulting in serious under-utilization of core resources. Note that it is very common to run a high number of processes from different security domains on modern servers, which calls for scalable defense solutions.

DAWG [10], SecDCP [62] and NoMo cache [63] are dynamic way-partitioning techniques. These mechanisms can dynamically adjust the number of ways for each security domain to avoid cache under-utilization. However, when the number of security domains is higher than the cache associativity, they are forced to re-assign cache ways from one domain to another. These re-assignment operations can leak cache occupancy information from the victim to the attacker.

The second type of partitioning technique, used by CATalyst [64] and StealthMem [65], partitions the cache into two regions, i.e., a security-sensitive region and a non-secure shared region. The first region is reserved for security-sensitive data accesses. Cache interference within the security region is blocked via page coloring. The non-secure region can be dynamically shared by other applications. Unfortunately, both approaches require programmers to provide information about security-sensitive data or instruction accesses. Such information is not easy to obtain for many applications.

Randomization-based Defenses There are several mitigation techniques that rely on the randomization of the address mapping logic or system timing components. Newcache [66, 67], CEASER [68] and RPcache [69] randomize the mapping of addresses to cache sets to prevent the attacker from evicting target lines from caches. For example, CEASER dynamically remaps cache lines, so that the attacker cannot find an effective group of addresses that are mapped to the same set as the target address. However, these techniques can only reduce the bandwidth of cache attacks, instead of eliminating them. The attacker can still perform the evict operation when it accesses enough lines across a large number of cache sets. Liu et al. [70] proposed the Random Fill cache architecture for the L1 cache to defeat the cache-collision attack. However, this approach may suffer from substantial performance degradation if applied to the much larger last-level cache.

TimeWarp [71] and FuzzyTime [72] disrupt timing measurements by adding noise to the system clock. They can protect against attacks which measure cache access latency and execution time, but they are unable to prevent alias-driven attacks [49]. Furthermore, they hurt benign programs that require a high-precision clock.

Techniques to Detect Cache Attacks Several approaches have been proposed to detect cache-based side channel attacks. Chiappetta et al. [73] detect side channels based on the correlation of last-level cache accesses between victim and attacker processes. HexPADS [74] detects side channel attacks by the frequent cache misses caused by the attacker process. These heuristic approaches are not robust, and tend to suffer high false positives and false negatives. CC-Hunter [75] and ReplayConfusion [76] can effectively detect cache-based covert channel attacks. The main challenge in designing detection mechanisms is to achieve low false positives and low false negatives together. Consider an advanced attacker who mimics the behavior of benign applications and communicates secrets using an extremely low bandwidth. Most of the existing detection mechanisms are likely to miss such attacks.

# 2.4 COUNTERMEASURES AGAINST TRANSIENT EXECUTION ATTACKS

Wang et al. [77] pointed out that control speculation can enable new covert and side channels. Later, in January 2018, the disclosure of Spectre [3] and Meltdown [4] highlighted the broad attack surfaces offered by speculative execution in modern processors. Thereafter, transient execution attacks and defenses have become an active research problem. A systematization of transient execution attacks and defenses is presented by Canella et al. [59]. We review software-based defense solutions, followed by hardware-based ones.

Software-based Solutions Existing software-based solutions use two strategies to mitigate transient execution attacks. First, most software-based solutions block information leakage by limiting potentially malicious speculative execution. The immediate mitigations after the disclosure of Spectre and Meltdown were to place serializing instructions such as 1fence after sensitive branches [78,79], or replace branches with non-speculative cmovs. Alternative

approaches to limit speculative execution include introducing extra data-dependencies or control-dependencies between instructions, such as masking index bits before array look-ups or using return trampolines [80]. These solutions have performance, usability, or completeness issues. To reduce the performance overhead, oo7 [81] uses taint analysis to identify the branches that can be controlled by attackers, and only blocks the speculative execution of those branches.

Second, other software-based solutions aim to block interference between different security domains by providing better isolation. KAISER [82] proposes a practical kernel address isolation mechanism. It creates a shadow page table which only contains user-space mappings. When a process is running in user mode, the shadow page table is used, and thus, the user mode cannot obtain any information about kernel-space mappings. While KAISER claims to be able to close all hardware side channels on kernel address information, follow-on work [83] demonstrates that information leakage is still possible via a small set of kernel-space mappings in the shadow table, which are essential to handle system calls and interrupts. As another example, the Chrome web browser and V8 used to rely on language-enforced isolation, where untrusted code is sandboxed and executed in the same process as trusted code. Mcilroy et al. proposed to shift this isolation mechanism to process-based isolation [84].

Hardware-based Solutions Existing hardware defense mechanisms can also be classified into two categories. The first category focuses on limiting the side effects of transient instructions. InvisiSpec [21] and SafeSpec [85] prevent transient instructions from changing cache states, and use a shadow structure to hold speculative state for caches and TLBs. However, SafeSpec does not handle cache coherence or memory consistency model issues and, therefore, cannot support multi-threaded workloads. A relatively more aggressive approach is CleanupSpec [86], which allows speculative load instructions to change cache states and "undo" the changes upon misspeculations. These approaches introduce modest performance overhead, but require extensive changes to both the core and the memory subsystem.

Instead of introducing extensive hardware changes, a straightforward solution is to delay the execution of speculative instructions. However, conservatively delaying all speculative instructions can incur serious performance overhead. Several mechanisms have been proposed to address this performance problem by selectively delaying instructions. Conditional Speculation [87] and Delay-on-Miss [88] delay speculative load instructions only if they miss the L1 cache. Context-Sensitive Fencing [89] and ConTExT [90] use traditional taint tracking in cache and memory, and prevent user-marked secrets from being used by transient instructions. NDA [91] and SpecShield [92] restrict propagation of any data to speculative instructions that could form a side channel. They propose multiple design variants with

different performance-security tradeoffs. STT [93] proposes a novel form of taint tracking mechanism to identify transiently-accessed data and prevent such data from reaching side channels. In addition, STT provides a comprehensive study of all variants of side channels on speculative microarchitectures.

The second category aims to provide isolation of various hardware resources assuming that the attacker and the victim are in different security domains. Cache partitioning techniques [10,62,64] all fall in this category. MI6 [94] extends isolation to more realistic memory hierarchies, which have MSHRs and page walks.

#### CHAPTER 3: SHARP

This chapter presents Secure Hierarchy-Aware cache Replacement Policy (SHARP), an efficient and practical defense mechanism against cache-based side channel attacks for inclusive cache hierarchies. The design of SHARP is based on an important observation: in a cross-core cache-based side channel attack, creating "inclusion victims" is the key for the attacker to gain visibility into the victim's private cache. Consequently, we alter the line replacement algorithm of the shared cache to prevent a process from creating inclusion victims in the caches of cores running other processes. SHARP requires minor hardware modifications and induces negligible average performance degradation.

Shared caches offer a broad attack surface for side channel attacks, mainly due to the spatial and temporal sharing of cache hierarchies across different security domains. This chapter studies the most effective type of cache attack, namely, active cache-based side channel attacks (Section 2.2.3) in a cross-core setup, where attacker and victim processes execute on different cores, sharing the L2 or L3 cache of an inclusive cache hierarchy. The reason for the attack's effectiveness is that it leverages widely-used commodity hardware, and is relatively easy to set up. Our goal is to defeat cross-core active cache attacks by blocking cache interference.

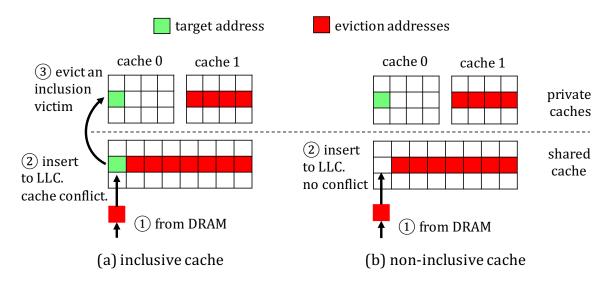

We make the following observation: in an inclusive cache hierarchy, it is easy for the attacker to evict the target line from the private cache of the core running the victim process. This is because, if the line is in the shared cache, it is also practically always in the private cache of the core running the victim process. The reason is the tight timing requirements to mount a successful attack. Then, when the attacker evicts the line from the shared cache, the line is also automatically evicted from the private cache of the core running the victim process, creating an *inclusion victim*.

Some authors have studied the impact of inclusion victims on performance (e.g., [95,96]). However, in most designs, the cache replacement algorithm in the shared cache only uses information on shared cache hits and misses, and is oblivious of hits in the private caches.

The main proposal of this chapter is to alter the shared cache replacement algorithm to prevent a process from creating inclusion victims in the caches of cores running other processes. The attacker is unable to evict the target address from the shared cache and, hence, cannot glimpse any information on the victim's access patterns. Note that cache attacks do not always use load instructions to force the eviction of a victim's target addresses

from the cache; sometimes they use an instruction called clflush. Hence, our proposal also involves a slightly modified clflush instruction to thwart these attacks.

We call our proposal SHARP (Secure Hierarchy-Aware cache Replacement Policy). SHARP requires minimal hardware modifications. It works for all existing applications without requiring any code modifications. Finally, it induces negligible average performance degradation.

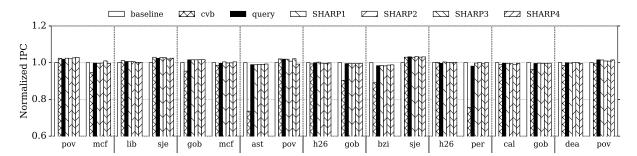

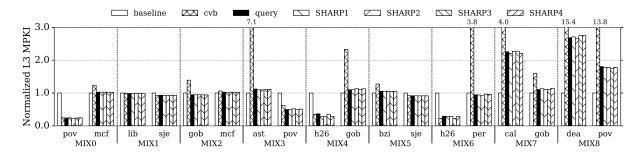

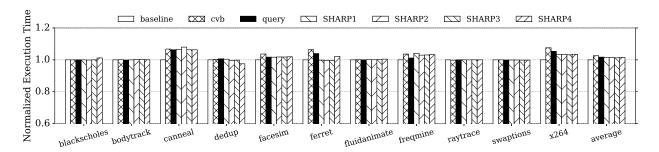

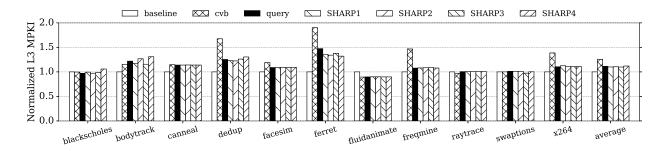

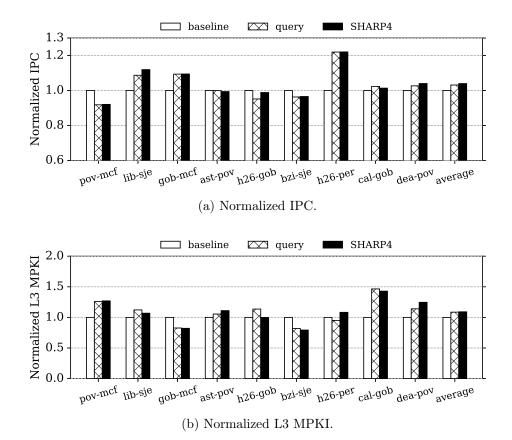

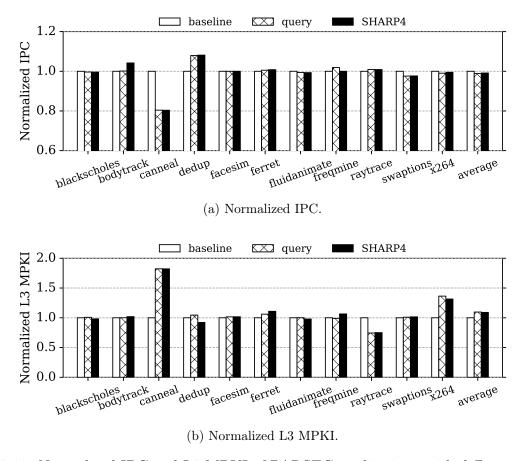

To validate SHARP, we implement it in a cycle-level full-system simulator and test it against real-world attacks. SHARP effectively protects against these attacks. In addition, we run many workloads from SPEC and PARSEC applications to evaluate SHARP's impact on performance.

The contributions of this chapter are:

- The insight that, to effectively prevent cache attacks in an inclusive cache hierarchy, we can alter the shared cache replacement algorithm to prevent a process from inducing inclusion victims on other processes.

- The design of SHARP, which consists of a new cache line replacement scheme and a slightly modified clflush instruction.

- A simulation-based evaluation of SHARP that shows that it is effective against realworld attacks, and induces negligible average performance degradation.

## 3.1 ATTACK ANALYSIS

As discussed in Section 2.2.3, an active cache-based side channel attack always involves an "interfere" step. In this section, we analyze the two interfere strategies.

#### 3.1.1 Conflict-based Attacks

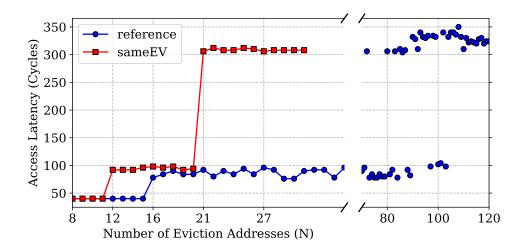

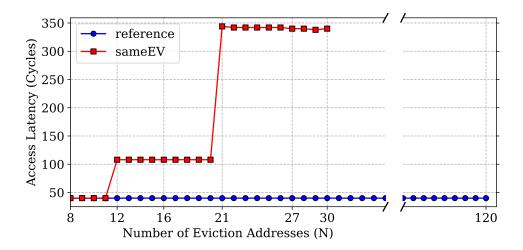

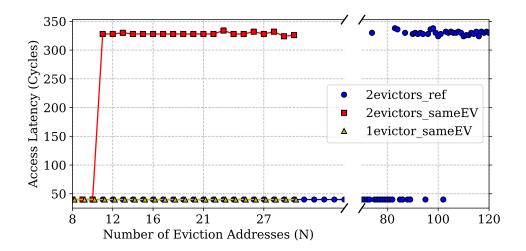

We find that all successful conflict-based attacks share two traits: (1) they generate inclusion victims in the private cache of the core running the victim thread, and (2) they exploit modern cache line replacement policies that do not properly defend against malicious creation of inclusion victims.

Consider the first trait. As discussed in Section 2.2.3, an attack cycle in an active cache attack follows three steps: interfere, wait and analyze. Existing conflict-based attacks generate inclusion victims in the private cache of the victim process' core. This is because the duration of an attack cycle between consecutive interfere steps is usually very short — on the order of several thousand cycles. Attacks use such short cycles to reduce the noise in the

analyze step. As a result, if the victim accesses the target addresses during the wait step, then such addresses will typically remain in the victim's private cache by the next interfere step. Hence, when the attacker performs the interfere step, it generates inclusion victims in the private cache of the victim's core.

The second trait concerns the fact that deployed cache line replacement algorithms and deployed algorithms for inserting referenced lines in the replacement priority list, do not take into consideration the possible creation of inclusion victims. This makes commercial systems vulnerable to conflict-based attacks.

Recent proposals (e.g., [97–100]) take into account the requesting core ID when deciding what line in the set to replace, or what priority in the replacement list to assign to the referenced line. However, they do it to improve resource allocation or to enhance performance, and do not try to eliminate inclusion victims. Only the TLA cache management proposal [96] uses some hints that try to minimize the probability of creating inclusion victims. However, since TLA is focused on performance, it does not guarantee the elimination of inclusion victims and, hence, cannot provide security guarantees.

#### 3.1.2 Flush-based Attacks

The x86 clflush instruction invalidates a specific address from all levels of the cache hierarchy [52]. The invalidation is broadcasted throughout the cache coherence domain. If, at any cache, the line is dirty, it is written to memory before invalidation. In user space, clflush is used to handle memory inconsistencies such as in memory-mapped I/O and self-modifying codes. In kernel space, clflush is used for memory management, e.g., to flush from the caches all the lines belonging to a page that is being swapped out.

Flush-based attacks rely on the clflush instruction to evict target addresses from the cache. Entirely disabling the use of such instruction is impractical due to both legacy issues and valid use cases. However, we make a key observation about the legitimate uses of clflush: in user mode, clflush is only really needed in uses that update memory locations. Specifically, it is needed to handle the case when the value of a location in caches is more up-to-date than the value of the same location in main memory. In such cases, clflush brings the memory to the right state.

We argue that there is no need to use clflush in user mode for pages that are read-only or executable, such as those that contain shared library code. Allowing the use of clflush in these pages only makes the system vulnerable to flush-based attacks.

#### 3.2 SHARP DESIGN

Secure Hierarchy-Aware cache Replacement Policy (SHARP) is composed of a new cache replacement scheme to protect against conflict-based cache attacks, and a slightly modified clflush instruction to protect against flush-based cache attacks. In the following, we discuss SHARP's two components, and then give some examples of defenses.

## 3.2.1 Protecting Against Conflict-based Attacks

To protect against conflict-based attacks, SHARP's main idea is to alter a shared cache's replacement algorithm to minimize the number of inclusion victims that a process induces on other processes. The goal is to prevent an attacker process from replacing shared-cache lines from the victim process that would create inclusion victims in the private caches of the victim process' core. The result is that the attacker cannot create a conflict-based cache attack.

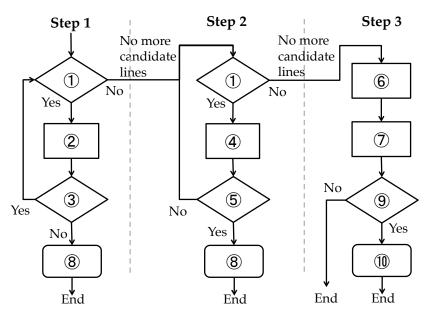

Assume that a requesting process R (potentially an attacker) wants to load a line into a set of the shared cache that is full. The hardware has to find a victim line to be evicted. The high level operation of the SHARP replacement algorithm is shown in Figure 3.1. It has three steps. In Step 1, SHARP considers each line of the set at a time  $(\mathfrak{D})$ , in the order based on its replacement priority. For each line, it checks if the line is in any private cache  $(\mathfrak{D})$ - $(\mathfrak{D})$ . As soon as a line is found that is not in any private cache, it is used as the replacement victim  $(\mathfrak{D})$ . Victimizing this line will not create any inclusion victim. If no such line is found, the algorithm goes to Step 2.

In Step 2, SHARP considers again each line of the set at a time  $(\mathfrak{D})$ , in the order based on its replacement priority. For each line, it checks if the line is present only in the private cache of  $R(\mathfrak{F})$ – $(\mathfrak{S})$ . As soon as one such line is found, it is used as the replacement victim  $(\mathfrak{S})$ . Evicting this line will at worst create an inclusion victim in R. No other process will be affected. If no such line is found, the algorithm goes to Step 3.

In Step 3, SHARP increments a per-core local alarm event counter (6) and selects a random line as the replacement victim (7). In this case, SHARP may create a replacement victim in a process that is being attacked. For this reason, when the alarm event counter of any core reaches a threshold (9), a processor interrupt is triggered (6). The operating system is thus notified that there is suspicious activity currently in the system. Any relatively low value of the threshold suffices, as a real attacker will produce many alarms to be able to obtain any substantial information. In the worst case, a smart attacker, who is aware of the threshold used by SHARP, can bypass the protection of SHARP by lowering the attack

- ① More lines to consider?

- (2)(4) Obtain information on the presence of the line in private caches

- ③ Is the line in any private cache?

- ⑤ Is the line present only in the requester's private cache?

- (6) Increment the alarm counter

- (7) Evict a random line

- (9) Is alarm counter > threshold?

- Generate interrupt

Figure 3.1: SHARP replacement algorithm.

bandwidth. We discuss potential attack strategies and the maximum attack bandwidth in Section 3.3.

From this discussion, we see that SHARP has very general applicability, requires no code modification (unlike [64,65]), and does not partition the cache among processes (unlike [62, 101]). It allows multiple processes to dynamically share the entire shared cache, while transparently protecting against conflict-based side channel attacks.

SHARP requires hardware modifications to implement its replacement policy. Specifically, SHARP must be aware of what lines within the shared cache are present in the private caches. Such information is needed in operations ② and ④ of Figure 3.1. In the subsequent subsections, we present three different ways of procuring this information.

Using Core Valid Bits In SHARP, each line in the shared cache is augmented with a bitmap with as many bits as cores. The bit for core i is set if the line is present in core i's private cache. These are the *Presence* bits used in directory-based protocols [102]. For example, in Intel, they are used in multicores since the Nehalem microarchitecture [103], where they are called Core Valid Bits (CVB).

In this first design, SHARP simply leverages these bits to determine the information needed in operations ② and ④ of Figure 3.1. Note, however, that these bits carry conservative information. This means that if bit i is set, core i may have the line in its private cache, while if bit i is clear, core i is guaranteed not to have the line in its private cache. Such conservatism stems from silent evictions of non-dirty lines from private caches; these evictions do not update the CVB bits. As a result, the CVB bits will still show the evicting core as having a copy of the line in its private cache. Overall, this conservatism will cause Steps 2 and 3 in Figure 3.1 to be executed more often than in a precise scheme. However, correctness is not compromised.

Using Queries A shortcoming of the previous design is that it often ends-up assuming that shared cache lines are present in more private caches than they really are. As a result, a process may unnecessarily fail to find a victim in Step 1 and end-up victimizing its own lines in Step 2, or unnecessarily fail to find a victim in Step 2 and end-up raising an exception.

To solve this problem, this second SHARP design extends the first one with core queries. Specifically, Step 1 in Figure 3.1 proceeds as usual; it often finds a victim. In Step 2, however, as each line is examined in order based on its replacement priority, the SHARP hardware queries the private caches of the cores that have the CVB bit set for the line, to confirm that the bit is indeed up to date.

The CVBs of the line are refreshed with the outcome of the query. With the refresh, the CVBs may show that, in reality, the line is in no private cache, or only in the private cache of the requesting processor. In this case, the line is victimized and the replacement algorithm terminates; there is no need to examine the other lines.

As a line's CVBs are refreshed, the line is considered to be accessed, and is placed in its corresponding position in the replacement priority. This is done to ensure that such a line is not considered and refreshed again in the very near future.

This design generally delivers higher performance than the first one. The reason is that the queries of private caches refresh the CVB bits, obtaining a more accurate state of the system for the future. Note that the queries are typically hidden under the latency of the memory access that triggered them in the first place.

Similar query-based schemes have been proposed in the past. They have been used to reduce inclusion victims with the aim of improving performance [96].

Using Core Valid Bits and Queries A limitation of the previous design is that it does not scale well. For multicores with many cores, the latency of the queries may not be hidden by the cache miss latency. Moreover, the traffic induced by the queries may slow down other

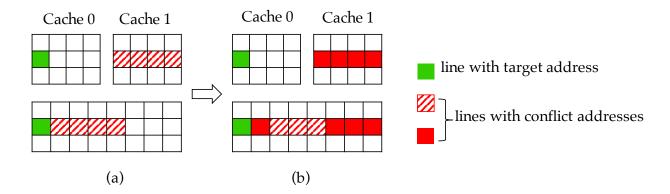

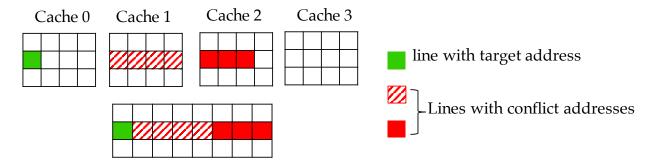

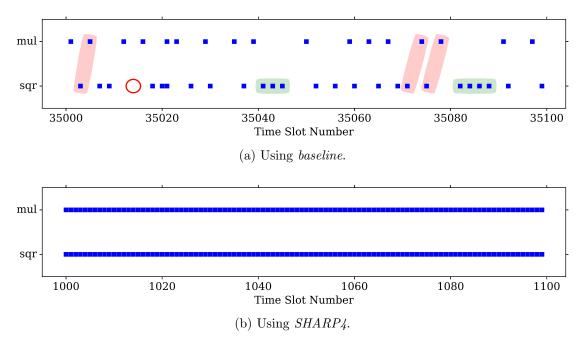

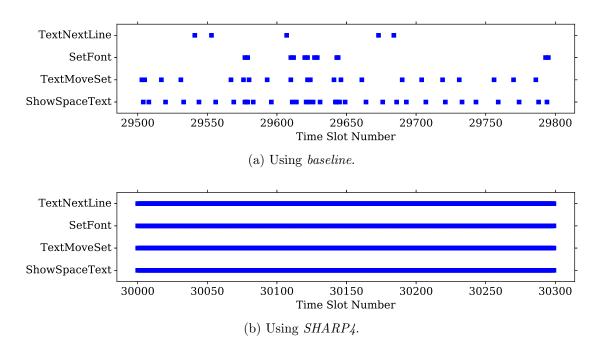

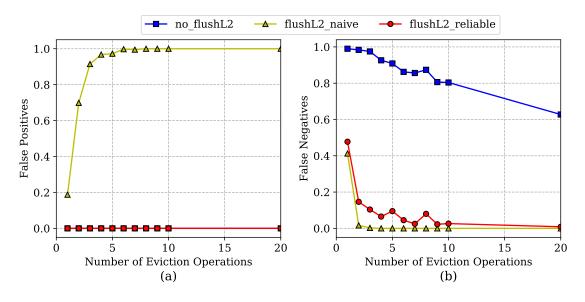

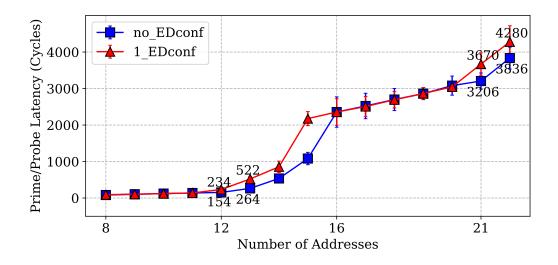

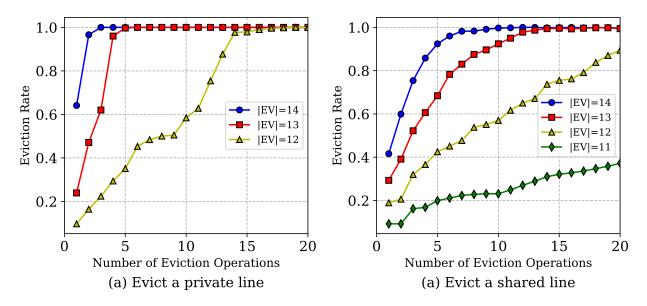

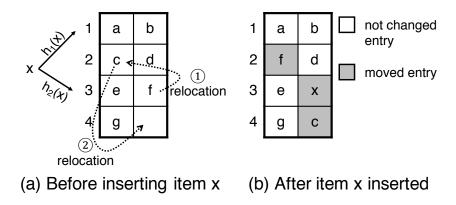

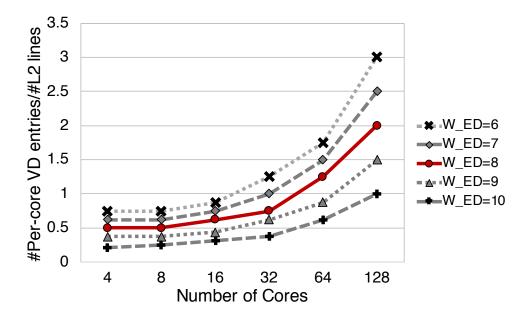

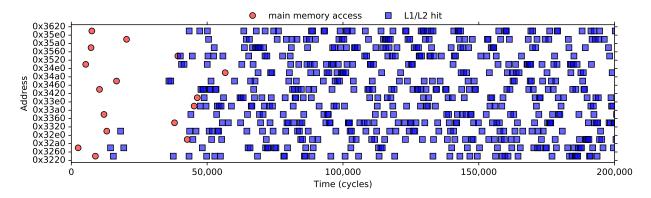

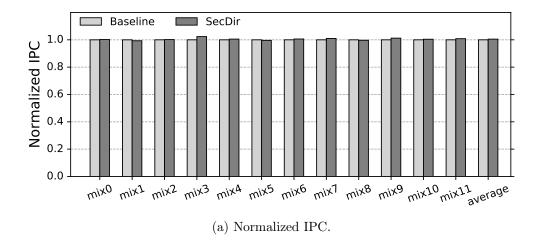

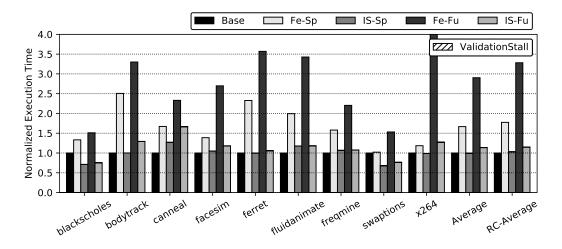

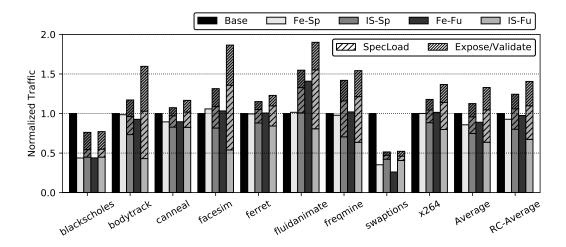

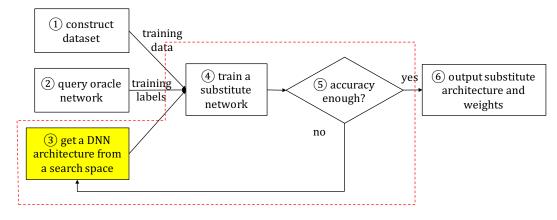

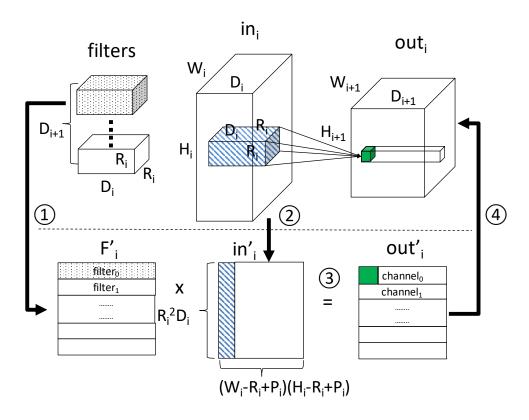

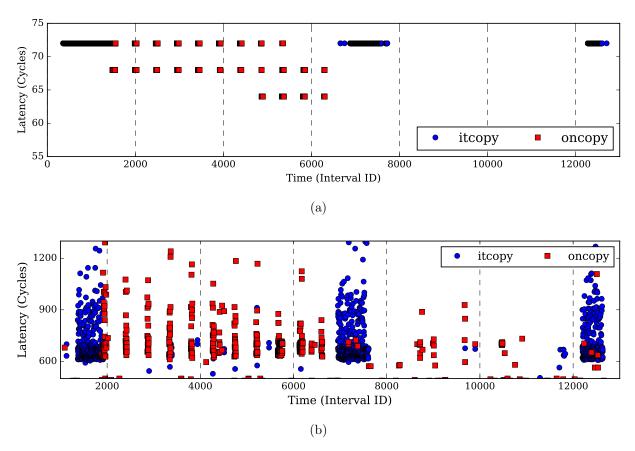

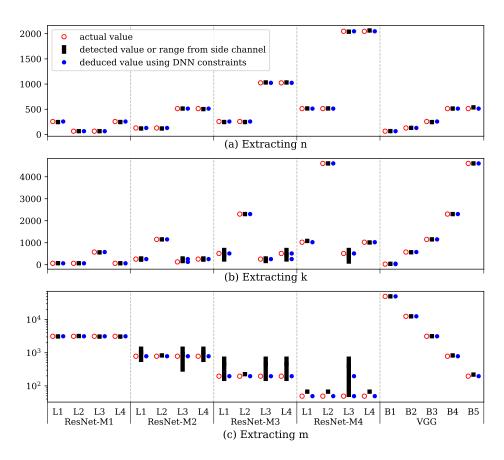

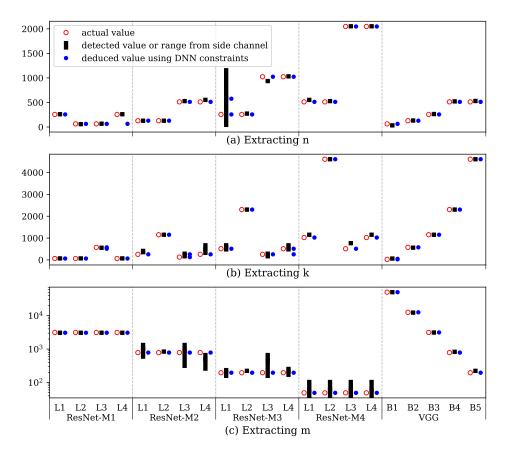

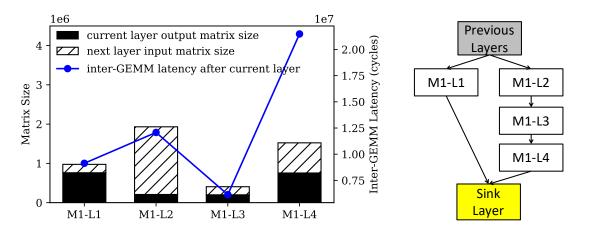

network requests. Consequently, we present a third SHARP design that reduces the number of queries.