### Don't Mesh Around: Side-Channel Attacks and Mitigations on Mesh Interconnects

Miles Dai\*, Riccardo Paccagnella\*, Miguel Gomez-Garcia, John McCalpin, Mengjia Yan

#### **Microarchitectural Attack Surfaces**

#### **Microarchitectural Attack Surfaces**

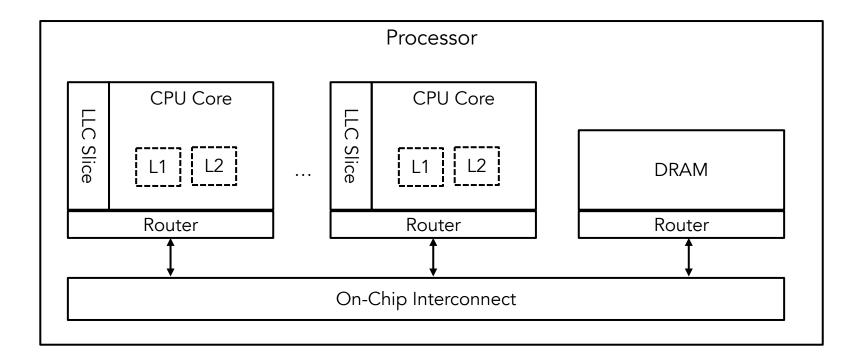

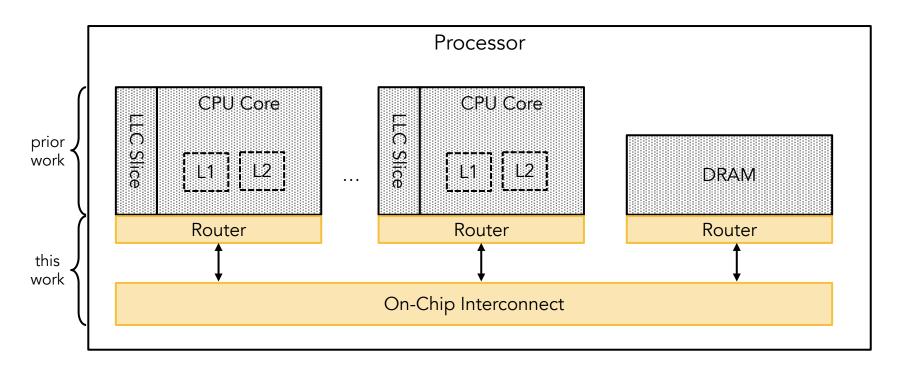

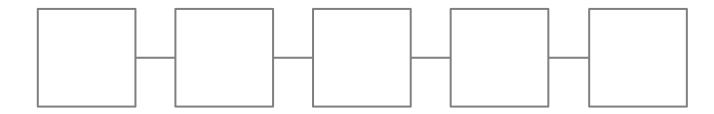

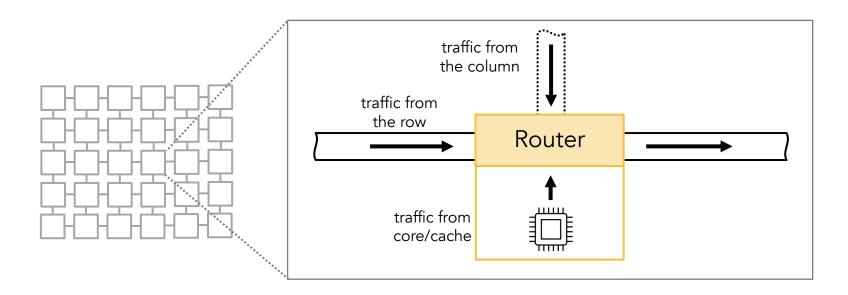

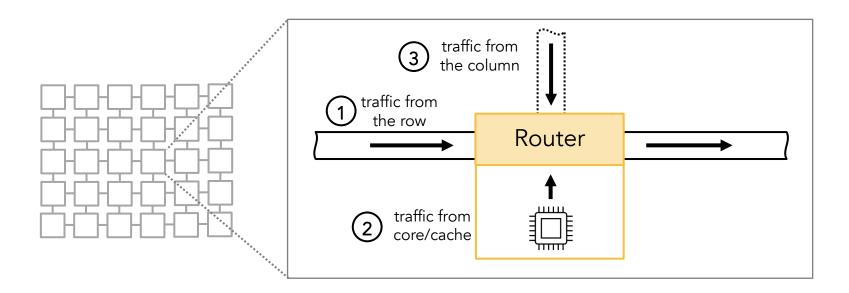

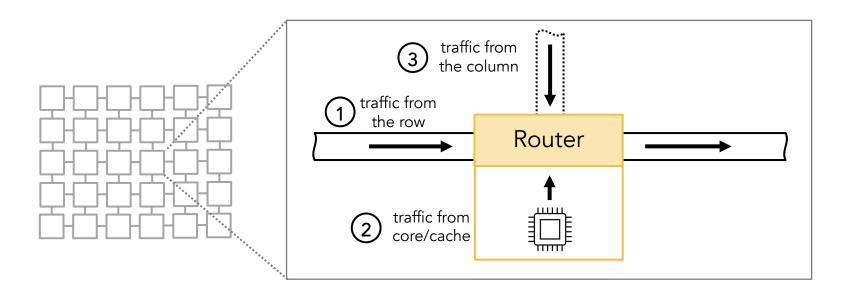

#### **On-Chip Interconnects**

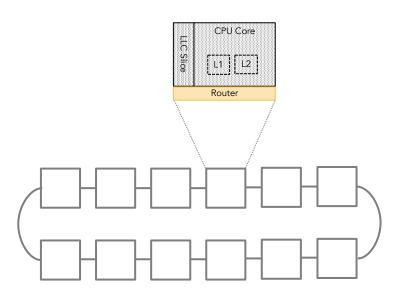

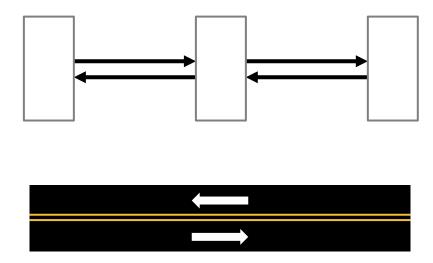

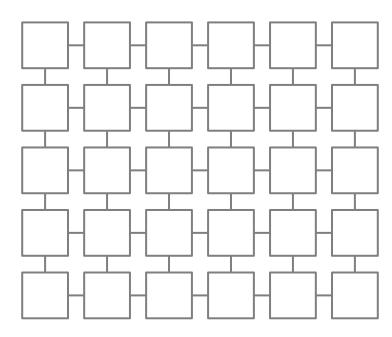

Ring Interconnect

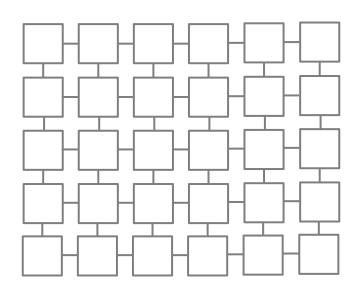

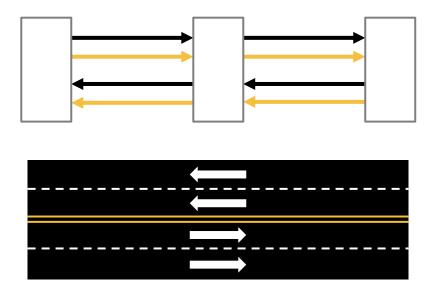

Mesh Interconnect

### **Mesh Interconnect Challenges**

### **Research Questions**

- Is it feasible to construct attacks by only exploiting contention on a mesh interconnect?

- Are there non-invasive approaches that can mitigate these attacks without requiring hardware modifications?

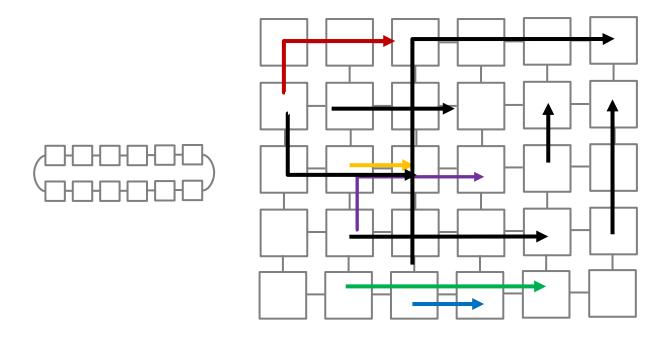

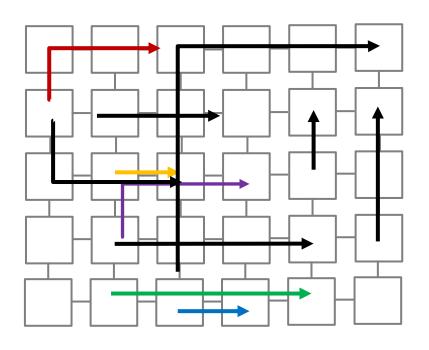

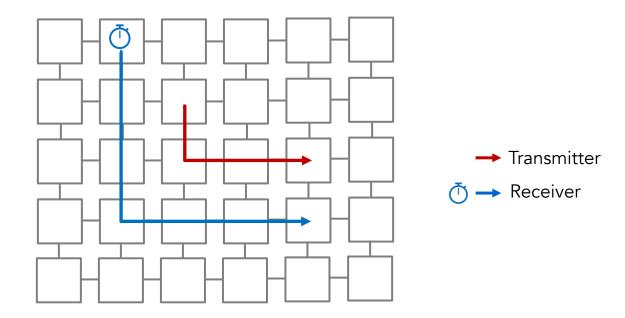

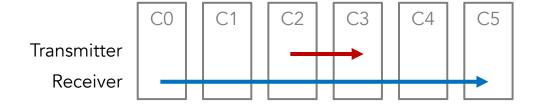

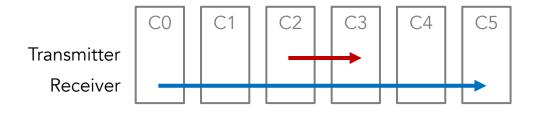

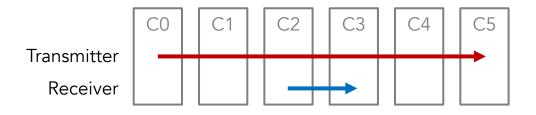

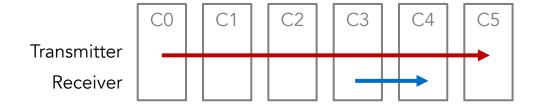

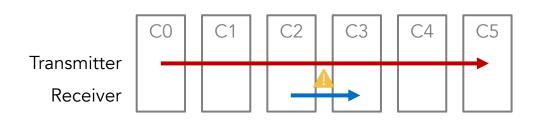

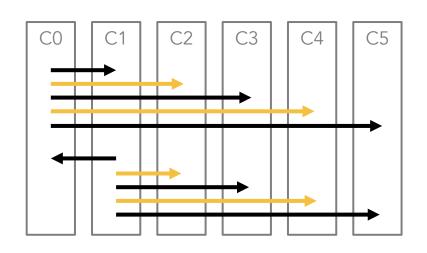

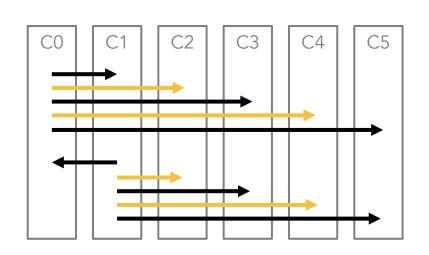

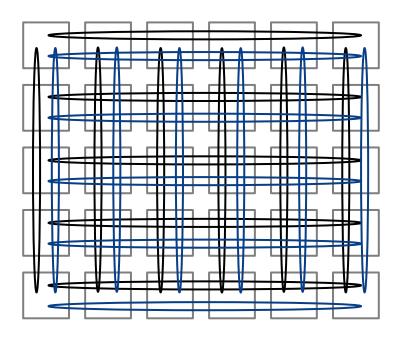

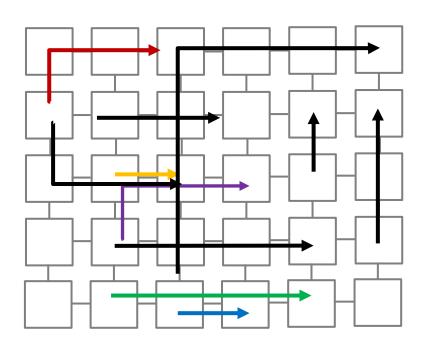

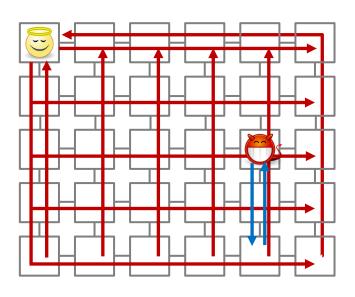

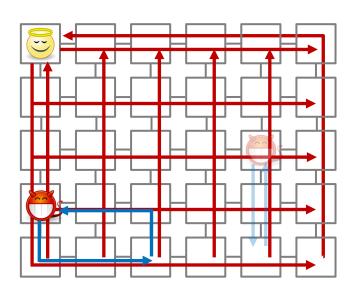

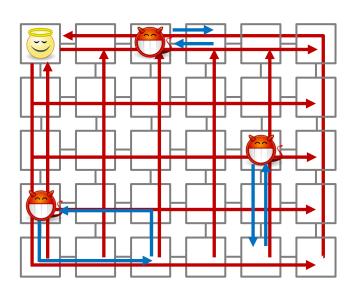

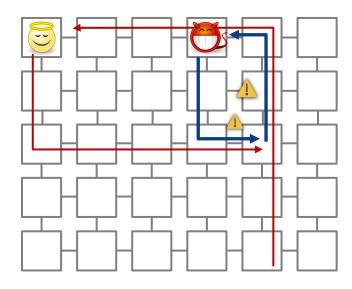

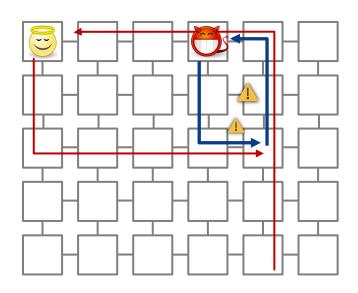

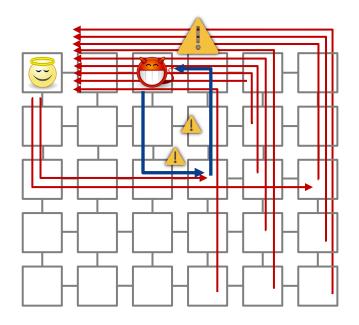

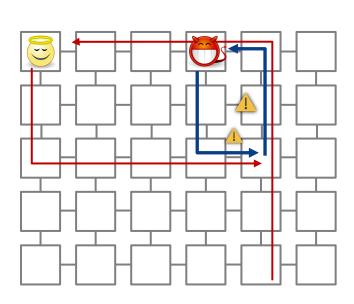

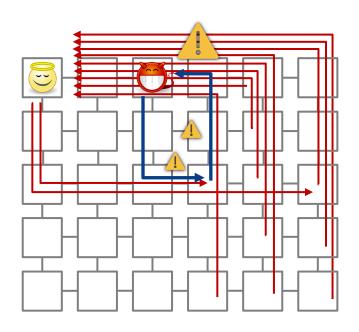

Overlapping paths

Same direction

Overlapping paths

Same direction

In practice, overlapping flows in same direction do not always cause contention!

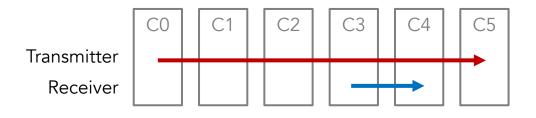

Contention

No contention

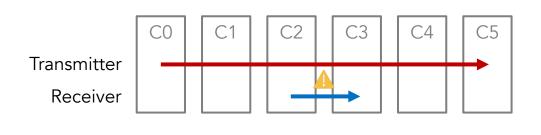

16

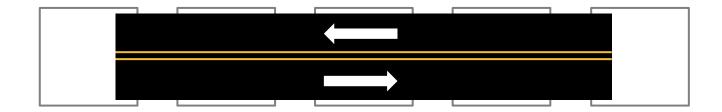

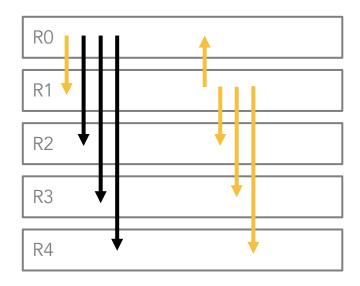

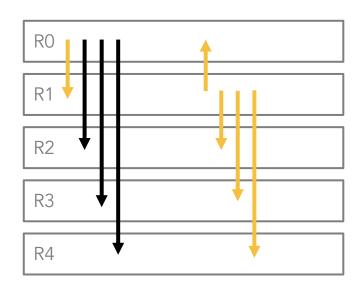

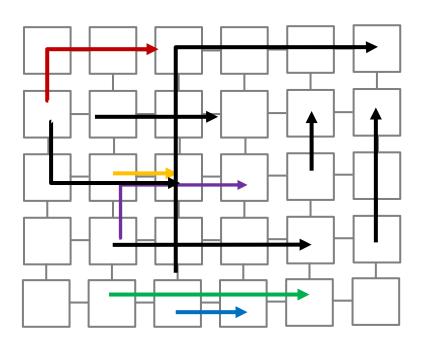

Transmitter traffic must have higher priority to delay receiver traffic.

Contention

No contention

Two lanes per direction

Traffic must travel on the same lane to contend.

### **Research Questions**

- Is it feasible to construct attacks by only exploiting contention on a mesh interconnect?

- Are there non-invasive approaches that can mitigate these attacks without requiring hardware modifications?

#### **Research Questions**

- Is it feasible to construct attacks by only exploiting contention on a mesh interconnect?

- Are there non-invasive approaches that can mitigate these attacks without requiring hardware modifications?

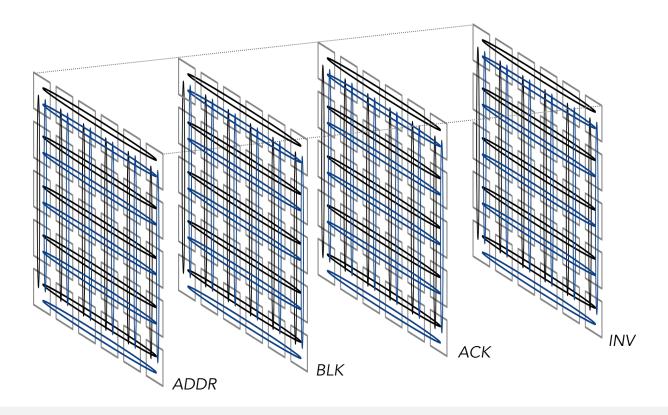

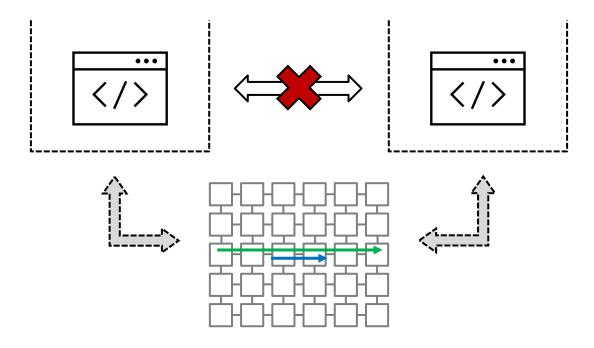

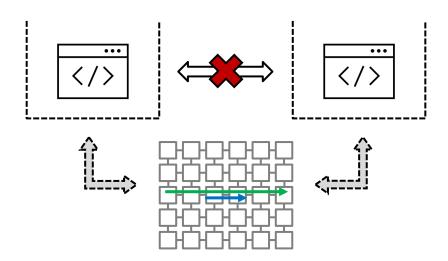

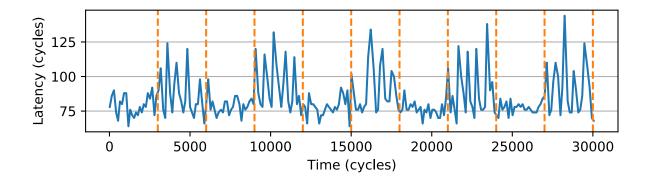

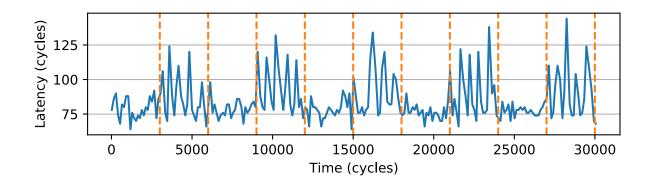

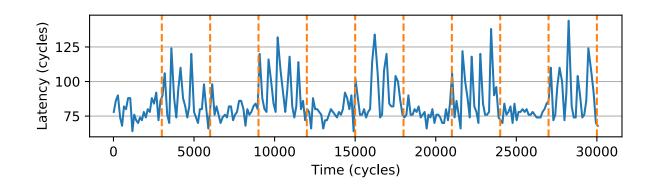

- Transmit "1" → mesh contention

- Transmit "0"  $\rightarrow$  idle

- Transmit "1" → mesh contention

- Transmit "0"  $\rightarrow$  idle

- Transmit "1" → mesh contention

- Transmit "0"  $\rightarrow$  idle

Channel Capacity over 1.5 Mbps!

- Transmit "1" → mesh contention

- Transmit "0" → idle

Channel Capacity over 1.5 Mbps!

Works across VMs!

```

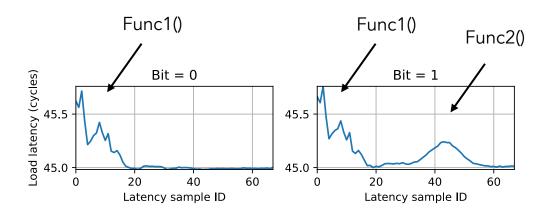

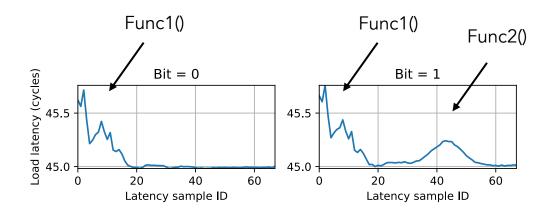

for bit b in secret key do

Func1();

if b == 1 then

Func2();

```

Used in vulnerable RSA and ECDSA implementations

```

1 for bit b in secret key do

2 Func1();

3 if b == 1 then

4 Func2();

```

Used in vulnerable RSA and ECDSA implementations

More details in the paper

```

1 for bit b in secret key do

2 Func1();

3 if b == 1 then

4 Func2();

```

Used in vulnerable RSA and ECDSA implementations

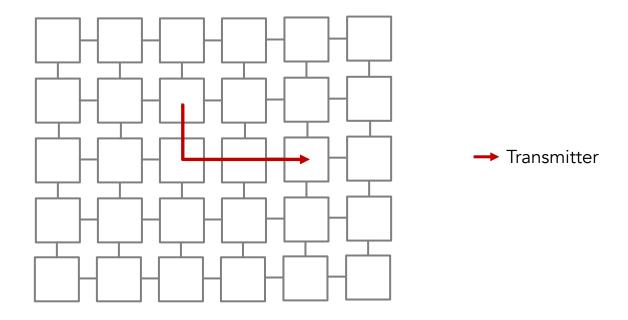

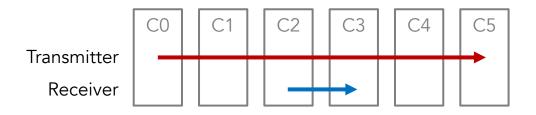

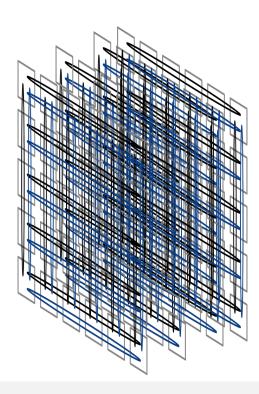

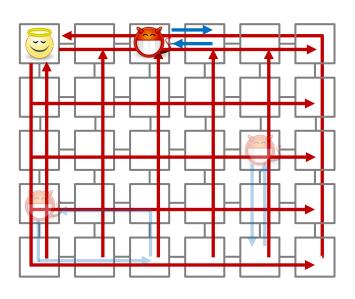

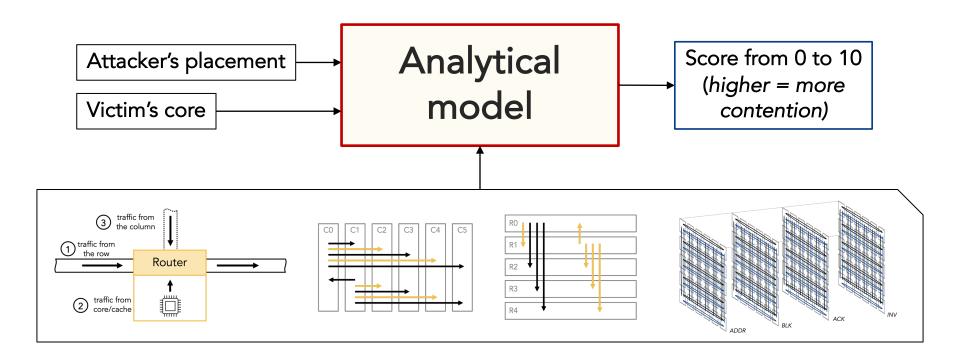

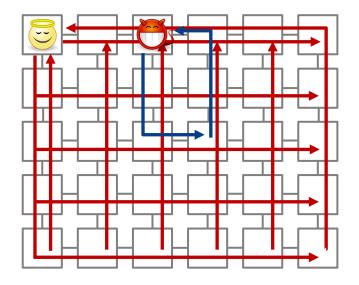

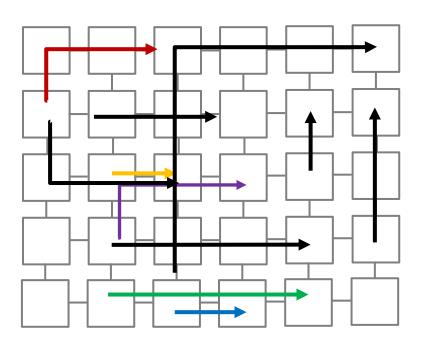

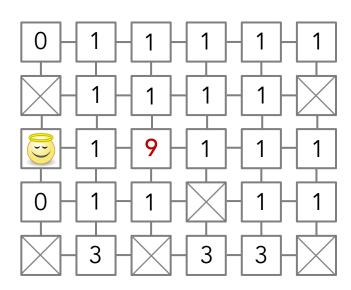

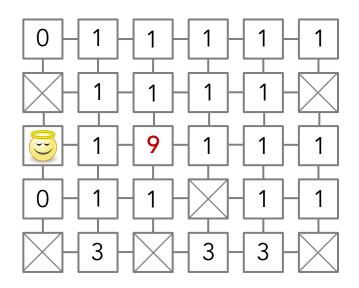

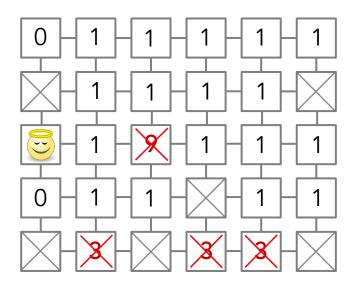

Best attacker placement?

Best attacker placement?

Best attacker placement?

- Best attacker placement?

- 23 cores \* 25 slices = 575 attacker placement options!

- Best attacker placement?

- 23 cores \* 25 slices = 575 attacker placement options!

We construct an *analytical* model to rank placements

Score = 1

## **Research Questions**

- Is it feasible to construct attacks by only exploiting contention on a mesh interconnect?

- Are there non-invasive approaches that can mitigate these attacks without requiring hardware modifications?

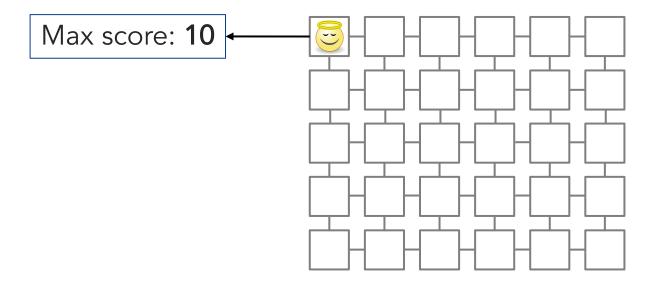

# Impact of the Victim's Core

# Impact of the Victim's Core

## Impact of the Victim's Core

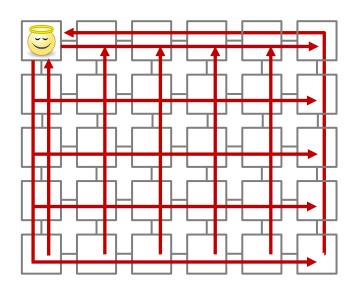

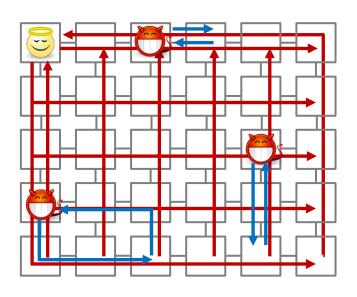

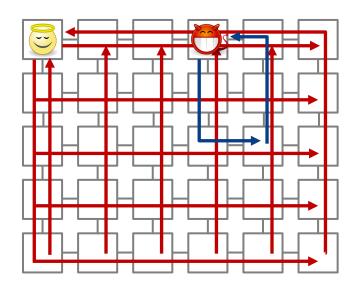

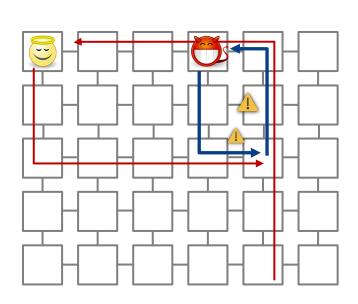

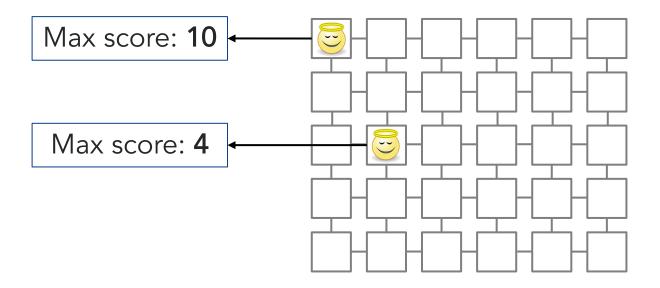

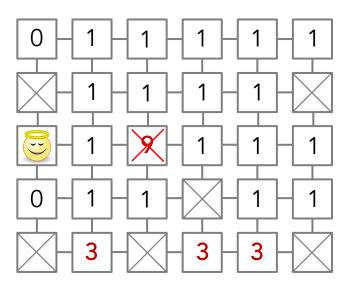

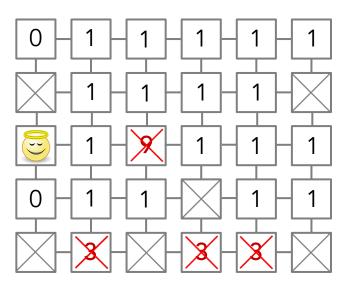

# **Mitigation Insight #1**

Max score: ?

Max score: 9

Max score: 9

Can we prevent the attacker from taking good placements?

Max score: 9

Max score: 3

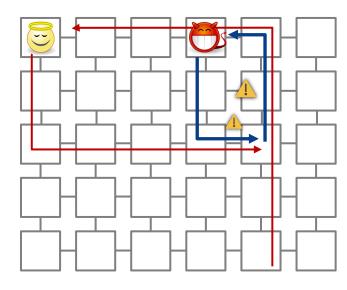

Max score: 9

Max score: 3

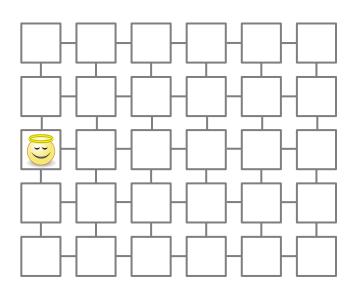

Max score: 1

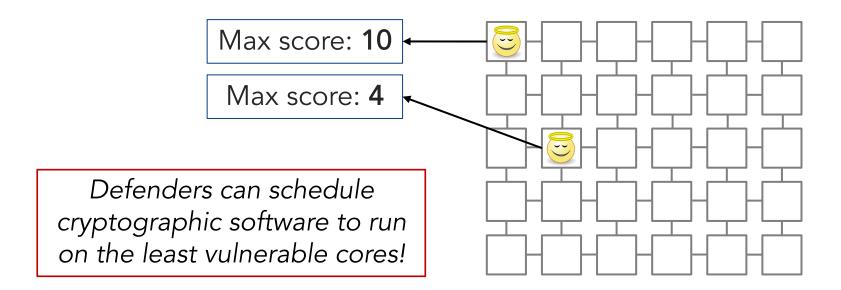

# Mitigation Insight #2

Max score: 3

Max score: 1

Defenders can reserve certain cores for the victim's security domain!

### **Conclusion**

- On-chip interconnects remain an overlooked microarchitectural attack surface, ignored by existing "domain isolation" defenses.

- This work demonstrates the feasibility of side channel attacks on the mesh interconnect.

- This work offers new insights into mitigating these attacks without changing the hardware.

https://github.com/CSAIL-Arch-Sec/dont-mesh-around