MULTICS STAFF BULLETIN-54

TO:

Distribution

FROM:

N. I. Morris

DATE:

June 12, 1972

SUBJECT:

Memory Map for Follow-On Multics System

This document obsoletes MSB-47.

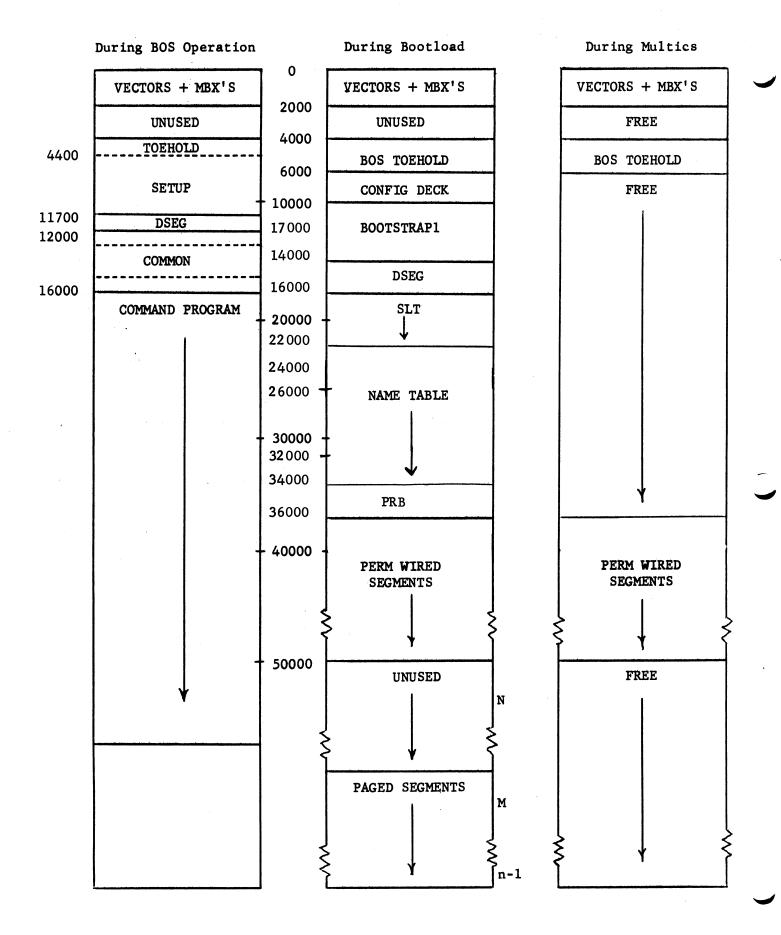

This document describes how primary memory will be utilized for the follow-on system. It describes how bootstrapl and BOS lay out the data at bootload time and also how the memory is used during normal Multics operation and normal BOS operation. Reference is made to core blocks which are in units of 1024 word blocks of memory configured.

During its operation, bootstrapl lays out memory as shown below:

| BLOCK NUMBER (S) | ADDRESSES | USE                        |

|------------------|-----------|----------------------------|

| 0                | 0         | INTERRUPT VECTOR           |

|                  | 100       | FAULT VECTOR               |

|                  | 200       | INTERRUPT TRANSFER PAIRS   |

|                  | 300       | INTERRUPT SCU PAIRS        |

|                  | 400       | FAULT TRANSFER PAIRS       |

|                  | 500       | FAULT SCU PAIRS            |

|                  | 600       | DN355 MAILBOX              |

|                  | 1100      | PROCESSOR INITIALIZE AREA  |

|                  | 1200      | BULK STORE MAILBOX         |

|                  | 1400      | IOM (IMW AREA AND MAILBOX) |

| 1             | 2000  | UNUSED (CAN BE RESERVED FOR FUTURE EXPANSION OF IOM's AND DN355's.) |

|---------------|-------|---------------------------------------------------------------------|

| 2             | 4000  | BOS TOEHOLD                                                         |

| 3             | 6000  | CONFIGURATION DECK                                                  |

| 4,5           | 10000 | BOOTSTRAP1                                                          |

| 6             | 14000 | TEMPORARY DESCRIPTOR SEGMENT                                        |

| 7,8,          | 14000 | SLT                                                                 |

| 9,10,11,12,13 | 22000 | NAME TABLE                                                          |

| 14            | 34000 | PHYSICAL RECORD BUFFER                                              |

| 15_N-1        | 36000 | PERM WIRED                                                          |

| N-M-1         |       | FREE                                                                |

| <b>M</b> -n-1 |       | PAGED SEGMENTS                                                      |

|               |       |                                                                     |

Where N and M depend on the particular system being bootloaded.

After initialization certain pages are freed (added to the paging pool) and the layout appears as follows:

| 0      | 0     | AS ABOVE (MEX's + VECTORS) |

|--------|-------|----------------------------|

| 1      | 2000  | FREE (FOR PAGING)          |

| 2      | 4000  | AS ABOVE (BOS)             |

| 3→14   | 6000  | FREE (FOR PAGING)          |

| 15→N-1 | 36000 | PERM WIRED                 |

| Nn-1   |       | FREE (FOR PAGING)          |

## When BOS is running, it utilizes memory as follows:

| 0     | 0             | AS ABOVE (MBX's + VECTORS) |

|-------|---------------|----------------------------|

| 1     | 2000          | UNUSED                     |

| 2,3,4 | 4000          | BOS TOEHOLD                |

|       | 4400          | SETUP (BOS MAIN CONTROL)   |

|       | 11700         | DESCRIPTOR SEGMENT         |

| 5,6   | 12000         | BOS COMMON AREA            |

|       | <b>12</b> 000 | SAVED MACHINE CONDITIONS   |

|       | 12400         | BOS INTERNAL VARIABLES     |

| •     | 14000         | CONFIGURATION DECK         |

| 7-22  | 16000         | COMMAND PROGRAM            |

The following Diagrams are meant to describe the three memory layouts: