# Supplement to the 645 Processor Manual

# MASSACHUSETTS INSTITUTE OF TECHNOLOGY INFORMATION PROCESSING CENTER

May 22, 1973

#### SUMMARY OF THE H6180 PROCESSOR

#### INTRODUCTION

This memo presents a summary of the H6180 processor from the point of view of the subsystem writer who must write or debug code at the assembly language level. The H6180 processor represents an extension and general cleanup of the H645, and this memo assumes that the reader is reasonably familiar with the H645.\*

Experience with the H645 and the Multics system has uncovered a number of areas in which performance and maintainability could be substantially improved with certain deviations from the H645 specification. The following areas were felt to be of sufficient importance to warrant changes to the H645 specification.

- 1. Hardware aids for improved compatibility with standard H600 and H6000 line software.

- 2. Refinements to the paging and segmentation mechanisms to improve overall system performance.

- 3. Complete implementation of the Multics protection ring mechanism in the H6180 processor to improve system performance and reduce software complexity.

- 4. Incorporation of the H6080 Extended Instruction Set (EIS)\* within the H6180 processor. The EIS provides a comprehensive set of instructions for bit and character string manipulation as well as decimal arithmetic.

These changes are described in detail on the following pages.

<sup>\*</sup>For more information, refer to the Honeywell Model 645 Processor Reference Manual and the Series 6000 Extended Instruction Set Processor manual.

#### 1. Hardware Compatibility with H600/H6000

The issue of compatibility with product line software is really two issues stemming from two distinctly different motivations. One issue is that of "stand-alone compatiblity" which allows the running of standard product line software (e.g., GCOS, T and D monitor, etc.) on a stand-alone machine. The other issue is that of "slave program compatibility" which allows for the efficient execution of H600/6000 slave programs under the control of the Multics system. A compatibility switch on the H6180 processor handles the problem of stand-alone compatibility while a program-settable mode is provided as a software aid in handling the problem of slave program compatibility.

#### 2. Modifications to the Paging and Segmentation Hardware

The H6180 contains a number of modifications to the H645 paging and segmentation hardware to improve the performance of the Multics software and to simplify some areas now felt to have been overdesigned in the H645. The changes to the H645 specification are summarized below and are described in more detail later in this memo.

- 2.1 The address field in the segment descriptor word is extended to a full 24-bit absolute address to allow page tables (and unpaged segments) to begin on any main memory address. This modification allows the software a great deal more flexibility in the allocation of page table space and greatly reduces the amount of main storage reserved for page tables.

- 2.2 The processor supports only a single page size rather than the two page sizes supported by the H645. However, provision is made to allow the page size to be modified by field engineering in an orderly and well understood fashion.

- 2.3 Each of the eight address base registers (now called Pointer Registers) of the H6180 processor is extended to contain both a segment number and a word number portion. The H645 concept of internal and external base registers and control fields is dropped. Each of the eight address base registers on the H6180 processor behaves as a 645 base register pair. In addition, each of the new address base registers contains a bit offset field for use by the new EIS instructions.

- 2.4 Some minor changes have been made to the definition of the 645 master and slave modes which are renamed respectively to be the privileged and unprivileged modes to avoid confusion with H6000 terminology. A minor change has also been made in the treatment of execute-only segments to allow entry at locations other than zero.

2.5 The access control information contained in the H645 page table word (not used in Multics) has been removed. In the H6180, all access control is implemented in the segment descriptor word.

# 3. Hardware Implementation of Multics Ring Protection

The Multics concept of protection rings, ring crossing and argument validation has been implemented as an integral part of the segmentation hardware on the H6180 processor. The hardware implementation of rings is really a further modification to the H645 segmentation hardware. However, the modification is introduced separately at this point since it involves perhaps the most significant deviation from the H645 specification and, as such, deserves somewhat more motivation. In the H645 version of Multics, the ring protection mechanism is, of necessity, completely simulated by the Multics software. The H645 Multics maintains, in parallel, separate descriptor segments for each ring of each process. The ring crossing is simulated by a rather costly and complex fault processing mechanism which includes the copying and validation of argument pointers and the switching of descriptor segments to simulate the effect of switching rings. The cost of the current simulation amounts to approximately 5 to 10 percent of the useful chargeable CPU time and contributes substantially to the overall complexity of the system. H6180 processor, ring crossing and argument validation are handled directly by the hardware without costly software intervention. As a result, a call to an inner ring requires no more CPU time than a call to a procedure in the same ring.

## 4. The Extended Instruction Set

The H6080 and the H6180 include instructions for string manipulation and decimal arithmetic. The eight address registers of the H6080 are a direct subset of the eight address base registers of the H6180 processor (also extended to contain bit offset fields).

The H6180 permits Multics programs to take full advantage of the new instructions in a manner which is sympathetic to the Multics environment. In addition, H6080 slave programs which use the new instructions will be able to continue to run efficiently under Multics.

## SLAVE PROGRAM COMPATIBILITY WITH THE H6000 SERIES

Many H635 and H6000 slave programs can be run on the H645 version of Multics (e.g., GCOS and the Dartmouth System). The H635 (or H6000) slave program is loaded into a single paged segment and Multics library programs are provided to intercept faults generated by the 635 program and provide the user-callable functions of the GCOS or DTSS supervisor. This technique works quite well for most slave programs. However, a number of 635 slave programs (particularly subsystems such as BASIC and the DTSS debugger) make indirect use of the H635 Base Address Register (BAR) by calling the supervisor to set the BAR to span a subset of the current user core image (e.g., to protect the subsystem from its user). In the H645 there is no general and effecient way to simulate the address relocation and protection of the BAR within a single paged segment. Therefore an H600/6000 BAR compatibility mode is provided on the H6180 which operates in the following manner when the H6180 is set to run in Multics mode.

- 1. A program-settable indicator is introduced to control the use of the BAR. The normal and usual setting of this indicator is ON, and in this state the contents of the BAR is ignored. When the indicator is OFF, the processor is said to be in BAR mode.

- When the processor is in BAR mode, the word number of each computed address is checked against the bound field of the BAR and augmented by the BAR base field. This operation cannot be interrupted and is done before the address is used to select the proper page table word. A boundary violation causes a "store" fault.

- 3. The contents of the BAR are settable by the normal H6000 LBAR instruction which is <u>unprivileged</u> when the H6180 is in Multics mode.

- 4. The BAR mode is turned on by the Transfer and Set Slave (TSS) instruction. (The contents of the BAR apply only to the final effective address of the TSS instruction.) The TSS instruction is also unprivileged in Multics mode.

- 5. The BAR mode is exited by a fault or an interrupt, and can only be reentered by an RCU or TSS instruction.

Many H600/6000 slave programs are written to expect certain externally generated faults and interrupts (e.g., timer runout) to be reflected to the slave program through a software-simulated fault vector. To avoid race conditions these programs commonly use bit 28 of the instruction word to inhibit external faults and interrupts. Furthermore, such programs are unprepared to handle interrupts in mid-instruction. So that H600/6000 slave programs can be run efficiently under Multics, the function of the BAR mode is extended as follows.

6. When in BAR mode, an unprivileged program (e.g., a 635 slave program) is allowed to inhibit interrupts via the use of bit 28 of the instruction word. In any mode, asynchronous interrupts encountered in mid-instruction are delayed until the instruction is complete. (In fact interrupt sampling is done only after an instruction pair completes execution, i.e., after most "odd" instructions.)

#### SEGMENTATION ON THE H6180

This section describes the segmentation hardware of the H6180. In most respects, the mechanism is quite similar to the H645 appending hardware with the addition of some refinements to improve the performance of the system software. The single substantial deviation from the H645 specification is the addition of hardware to implement the Multics protection ring mechanism.

#### 1. The Descriptor Segment Base Register (DSBR)

As in the H645 the base of the descriptor segment is located through the DSBR which on the H6180 specifies the following information.

| ADDR | BND | U | STACK |

|------|-----|---|-------|

| L    |     |   |       |

DSBR.ADDR

specifies the full 24-bit address of the first double word of either a page table (for a paged descriptor segment) or the first location of the descriptor segment itself (for an unpaged descriptor segment).

DSBR.BND

specifies the highest 0 mod 16 descriptor segment address which can be accessed without causing an out of bounds fault.

DSBR.U

specifies whether the descriptor segment is paged (= 0) or unpaged (= 1).

DSBR.STACK

is used in conjunction with the new CALL6 instruction. Whenever the H6180 processes a CALL6 instruction which requires the processor to switch to an inner ring (an inward call), the segment number of the stack for the inner (target) ring is computed by concatenating DSBR.STACK to the left of the ring number of the target ring. For example, if DSBR.STACK is 57 (octal) and the target ring is 3, the H6180 will compute the segment number of the stack for the target ring as 573 (octal). This facility is required to allow ring crossing to be fully automatic and places certain requirements on the segment numbers assigned to segments used as stacks.

# 2. The Segment Descriptor Word (SDW)

As in the H645 each segment (when active in main storage and known to a process) is described to the processor by a segment descriptor word (SDW) which is located by using the segment number of the segment as an index into the descriptor segment of the process. To accomodate the hardware-implemented ring crossing and argument validation and other changes, the SDW has been extended to the 72-bit double word described below.

| word | 0 | ADDR  |   | Rl | R2 | R3 | F | FC |  |    |   |

|------|---|-------|---|----|----|----|---|----|--|----|---|

| word | 1 | BOUND | R | E  | W  | P  | U | GΧ |  | CI | . |

SDW.ADDR (0-23) Is a full 24-bit absolute address and specifies the core address of either a page table (for a paged segment) or the first location of an unpaged segment.

SDW.Rl (24-26) Specifies the highest ring number of the read/write bracket for this segment (0-Rl, see (3) on rings and ring brackets).

SDW.R2 (27-29) Specifies the highest ring number of the read/execute bracket of this segment (R1-R2, see (3)).

SDW.R3 (30-32) Specifies the highest ring number of the call bracket of this segment ((R2+1) - R3, see (3)).

SDW.F (33)

Is a directed fault indicator and if off (= 0) specifies that the processor is to execute the directed fault specified in the FC field (see below).

SDW.FC (34-35) Indicates (if F is off) which of the 4 directed faults (DF0-DF3) the processor is to execute. (Note that the 645 provided for 8 directed faults.)

SDW.BOUND (1-14) Is the boundary field and indicates the highest 16-word block of the segment which can be addressed without causing an out-of-bounds fault. If the high order 14 bits of an address to this segment is greater than the value of the boundary field, an out-of-bounds fault is generated. boundary field could be maintained to the nearest word but special checks would have to be made for instructions which reference two or more continguous words.) A boundary field of 14 bits is chosen because some instructions (e.g., the new version of STB) reference up to 16 contiguous words. A further implication is that the software is expected to allocate unpaged segments on a zero mod 16 word boundary.

SDW.R (15)

Is the read-permit indicator. Data fetches by other segments are permitted to this segment only if this indicator is on (= 1) and if the processor is executing in a ring less than or equal to R2 (i.e., within the read/write or read/execute bracket, see (3)).

SDW.E (16)

Is the execute-permit indicator. Instruction fetches from this segment are permitted only if this indicator is on (= 1) and if the processor is executing in a ring greater than or equal to Rl and less than or equal to R2 (i.e., within the read/execute bracket, see below). Note that when the E indicator is on and the R indicator is off, the segment is to be treated as an "execute-only" procedure segment. execute-only procedure segment is permitted to reference data within itself (i.e., within the same segment) in spite of the lack of the read indicator. However, read permission is denied to other segments. (Note: targets of XEC and XED instructions can exist in segments with only the R bit on.)

SDW.W (17)

Is the write-permit indicator. Attempts to store into this segment are honored only if this indicator is on (= 1) and if the processor is executing in a ring less than or equal to Rl (i.e., within the read/write bracket, see below).

SDW.P (18)

Is the privileged mode indicator. If this indicator is on (= 1) and if the processor is executing in ring 0, the procedure segment is permitted to execute privileged instructions and inhibit interrupts under control of bit 28. Privileged procedures need no further powers and are subject to all other access checking (read, write permission bounds checking, etc.). Since privileged procedures can only be executed in ring 0, it is no longer necessary to limit calls to privileged procedures to enter via word 0 of the segment.

SDW.U (19)

Indicates whether the segment is paged (= 0) or unpaged (= 1). If the segment is unpaged, ADDR is the full absolute address of the first word (word 0) of the segment. If the segment is paged, ADDR is the full absolute address of the beginning of the page table for the segment.

SDW.G (20)

Is the gate indicator and if off (= 0) any call to this segment from a different segment must be directed to an address value less than the value of the CL field (see below).

SDW.CL (22-35)

Is the call limiter. If G is off any external transfer to this segment via the new CALL6 instruction (described below) must be directed to a word number less than the value of this field.

#### 3. Rings and Ring Brackets

A Multics process consists of procedure and data segments which are all directly addressable through the descriptor segment of that process. However, a process may only access a segment when the process is running at an appropriate level of privilege. For example, all of the segments of the hardcore supervisor are shared and accessible to all Multics processes but only when executing at the highest level of privilege.

The Multics system allows segments to be grouped into an ordered set of collections called rings in which segments requiring the highest level of privilege to reference can only be accessed from within the innermost ring of the set. Each ring is identified with a ring number designating the required level of privilege necessary to access segments in that ring. In Multics, the ring with the highest privilege is ring 0 which contains the procedures and data bases of the hardcore supervisor. Each user process has at least two rings, one for the hardcore supervisor and one for user programs and data. The user process may generate more rings (levels of lesser privilege) if desired.

Frequently, it is useful to allow a segment to be accessible in more than one ring. For example, it is often useful for a data base which is writeable in an inner ring to be readable in an outer ring. For this reason, the concept of ring brackets were introduced.

The access of a user to a specific segment is controlled by two quantities: the access attributes (e.g., read, execute, write) and the ring brackets. The ring brackets of a segment are specified by three integers (R1, R2 and R3) each of which must be greater than or equal to the preceding number. The first number (R1) specifies the top (highest ring number) of the read/write bracket, the second number (R2) specifies the top of the read/execute bracket and the last number (R3) specifies the top of the call bracket.

# 3.1 The Read/Write Bracket (Rings 0-R1)

Attempts to read or write a segment by a procedure executing in a ring within the read/write bracket are allowed if the appropriate (read or write) access indicators are on for the segment being referenced. Execution of a procedure in a ring within this bracket is permitted only at the top of the read/write bracket (R1) which is also the bottom of the read/execute bracket. Note that the highest ring from which a segment can be written is specified by R1. As a result, the data in the segment is no more reliable than the procedure segments which operate in that ring.

# 3.2 The Read/Execute Bracket (Rings R1-R2)

Attempts to read or execute (transfer to) a segment by a procedure executing in a ring within the read/execute bracket are allowed if the appropriate (read and execute) indicators are on for the segment being referenced. Writing of a segment within its read/execute bracket is permitted only from the ring at the bottom of the bracket (R1) which is also the top of the read/write bracket. If R2 is equal to R1 the read/execute bracket specifies a single ring (R1).

# 3.3 The Call Bracket (Rings (R2 + 1) - R3)

Attempts to call a (procedure) segment from another segment executing in a ring above the read/execute bracket, but within the call bracket of the procedure to be called, are allowed if the execute indicator of the procedure to be called is on and if the new CALL6 instruction (described below) is used. When the CALL6 instruction is directed to a procedure in an inner ring which has the appropriate execute access and call bracket, the processor will automatically switch to the ring specified as the R2 of the procedure being called. The call bracket and the CALL6 instruction are the only means (except for faults) by which control can be passed from an outer ring to an inner (more privileged) ring. If R3 is equal to R2, the call bracket is null and the procedure cannot be called from an outer ring.

#### 3.4 Summary

Assuming that the appropriate (read, execute or write) indicators are on, the following list summarizes the effects of the three ring brackets.

- 3.4.1 Writing is permitted from a ring within the read/write bracket only (i.e., if ring<R1).

- 3.4.2 Reading is permitted from a ring within the read/write bracket or the read/execute bracket (i.e., ring<R2).

- 3.4.3 Execution (or transfer of control) is permitted only from a ring within the read/execute bracket (i.e., Rl<ring<R2).

- 3.4.4 Calling (via CALL6 only) is permitted from a ring within the read/execute or call brackets (i.e., Rl<ring<R3).

- 3.4.5 The CALL6 instruction is the only instruction which may be used to access a segment in a ring within its call bracket (i.e., R2<ring<R3).

- 3.4.6 No access is permitted to a segment from a ring higher than the call bracket (i.e., ring>R3).

#### 4. Processor Address Registers

Like the 645, the H6180 processor has 10 address or pointer registers (PR's). Eight of these pointer registers can be directly accessed and modified by the software, one is used to locate the current instruction and one is used exclusively by the processor for effective address calculations. Unlike the 645, each of the eight program addressable pointer registers specifies a full segmented address including the segment number and the word number in a single pointer register.

#### 4.1 The Procedure Pointer Register

The procedure pointer register (PPR) is used by the processor to locate the current instruction and may be modified by the software to effect a transfer of control. The PPR is actually an extension of the PBR and IC of the 645. The contents of the 36-bit PPR are outlined below.

|   | PRR | PSR      | IC |

|---|-----|----------|----|

| 1 |     | <u> </u> |    |

PPR.PRR (3 bits)

Is the procedure ring register and specifies the ring (level of privilege) in which the processor is currently executing. PRR may be set to a higher value only by an RTCD or RCU instruction. It may be set to a lower value only by a CALL6 instruction (see below) or by a fault or interrupt.

PPR.PSR (15 bits)

Is the procedure segment register (same as the PBR in the 645) and specifies the segment number of the current procedure segment.

PPR.IC (18 bits)

Is the instruction counter (same as in the 645).

## 4.2 The Temporary Pointer Register

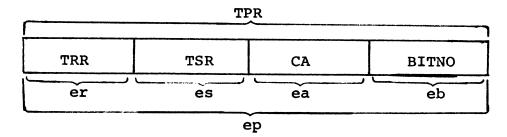

The temporary pointer register (TPR) is used exclusively by the processor for operand address calculations and serves the same general purpose as the TBR and computed address (CA) of the 645. It should be noted here that the addition of multiple-operand instructions (e.g., for string manipulation) requires additional TPR's (one for each additional operand). The contents of the 42-bit TPR are outlined below.

| TRR | TSR | CA | BITNO |

|-----|-----|----|-------|

TPR.TRR (3 bits)

Is the temporary ring register and is used to maintain the lowest level of privilege (i.e., highest ring number) encountered during operand address calculation. The TRR is initialized with the value of the PRR field of the PPR at the beginning of each instruction. During the operand address calculation, TRR is used to record the highest value of SDW.Rl (the top of the read/write bracket) of any segment used in the address calculation. For example, if an indirect address is fetched from segment X, TRR is set to the larger of TRR (its current value) and the Rl field in the SDW for segment Note that during the operand address calculation, the value of TRR may get larger but never smaller.

TPR.TSR (15 bits)

Is the temporary segment register (same as the TBR in the 645) and is initialized with the value of the PSR field of the PPR at the beginning of each instruction. During operand address calculation, TSR contains the segment number portion of the current address calculation.

TPR.CA (18 bits)

Is the computed address and serves the same function as the 645 register of the same name. The computed address is initialized at the beginning of each instruction with the contents of the instruction counter of the PPR. During operand address calculation, CA contains the word number portion of the current address calculation.

TPR.BITNO (6 bits) Is a bit offset relative to the first bit in the word specified by CA.

Once an operand address calculation is complete, the value of TRR is compared with the ring brackets of the segment containing the operand address to determine if the operation is to be allowed. For example, if the instruction intends to store into this operand, the value of TRR must be less than or equal to the Rl (in the SDW) of the segment to be modified.

# 4.3 The Eight Pointer Registers

The H6180 processor contains eight program-accessible pointer registers (PR's) which replace the 8 address base registers (ABR's) of the 645. The PR's of the 6180 processor differ from the 645 base registers in that each PR contains both a segment number and a word number portion. In effect, each PR of the 6180 processor behaves as a 645 base register pair. The contents of each 42-bit PR is outlined below.

| RN | SEGNO | WORDNO | BITNO |

|----|-------|--------|-------|

|    |       |        |       |

RN (3 bits)

Is used by the software to specify the level of privilege (i.e., ring number) at which the processor is to treat the address contained in the address register. When the processor uses the contents of a PR for address modification (e.g., bit 29 in the instruction word is on) the value of TRR is set to the larger of TRR (its current value) and the RN field of the specified PR. The use of the RN field of a PR allows the software to save the TRR of an operand address calculation (e.g., through the use of an EPP (effective pointer to pointer, formerly EAP) instruction.

SEGNO (15 bits)

Specifies the segment number portion of the segmented address.

WORDNO (18 bits)

Specifies the word number portion of the segmented address.

BITNO (6 bits)

Specifies a bit offset relative to WORDNO.

## 4.4 ITS Pointers

The software may store the contents of a PR into an ITS (indirect to segment) word pair with the use of an SPRI (store pointer in ITS format, formerly STP) instruction. The software may then address indirectly through the ITS indirect word rather than using the original PR. Alternatively, the software may reload another PR from the ITS word pair through the use of the EPP instruction. In either case, it is necessary to save the value of the RN of the PR in the ITS word pair so that the privilege level of the original operand address calculation is not lost. As a result, the ITS word pair is modified to include a ring number field as outlined below.

| $\boxtimes$ | SEGNO  | RN    | ITS . |  |

|-------------|--------|-------|-------|--|

|             | WORDNO | BITNO | MOD   |  |

- SEGNO (3-17) Is the segment number field (as in the 645). Note that bits 0-2 of the ITS word pair are set to zero for compatibility with 645 programs expecting an 18-bit segment number in the upper half of the first word.

- RN (18-20)

Is set to the value of the RN field of the PR during the SPRI instruction. If the processor attempts to indirect through an ITS word pair, TRR is set to the larger of TRR, RN (of the ITS), and Rl of the segment containing the ITS. Note that an improper value of RN in an ITS word pair has no ill effect since the processor always takes the maximum of TRR and RN. In other words, it is impossible for an ITS word pair to specify a higher privilege than the segment in which it resides.

- ITS (30-35) Specifies the modifier code (octal 43) for the ITS modifier (same as in the 645).

- WORDNO (0-17) Is the word number portion of the saved PR (same as in the 645).

- BITNO (21-26) Is the bit offset of the PR saved by the SPRI instruction.

- MOD (30-35) Is set to zero by the SPRI instruction but may be set by the software to specify further address modification (same as in the 645).

Since most Multics compilers (notably PL/I) calculate addresses via an EPP instruction, compiler-generated code can take full advantage of the hardware protection mechanism with little or no modification. If all addresses of all input parameters are calculated and saved (for use as outgoing argument pointers) via the use of the EPP and SPRI instructions it will be possible for a procedure operating in ring 1 to pass to ring 0 a parameter given to the procedure from ring 2 without checking the address of the parameter. The access checking is fully automatic as long as the TRR of the original address calculation continues to be maintained and passed along as the RN field of a PR or ITS word pair.

The STCD (store control double) instruction has been modified to store the PRR in the same manner as SPRI stores the RN field of a PR. The PRR is stored by the STCD to allow an RTCD (return control double) instruction to return to the proper ring.

#### 4.5 ITP Pointers

To accommodate the possibility of a bit offset, the indirect word for ITP modification (called ITB on the 645) has been modified as follows.

| PRNUM |        |   |       | ITP |

|-------|--------|---|-------|-----|

|       | WORDNO | X | BITNO | MOD |

- PRNUM (0-2) Is the number of the PR to be used in the indirection.

- ITP (30-35) Is the "Indirect Through Pointer" modifier (octal 41, the same as for ITB in the 645).

- WORDNO (0-17) Is added to the WORDNO field of the specified PR during indirection to form a new computed address.

- BITNO (21-26) Is the bit offset which overrides the BITNO field of the specified PR during indirection.

- MOD (30-35) May specify further address modification.

When an ITP modifier is found in the (even) word of an indirect reference, a new effective address is computed in the TPR as follows:

```

C(PRn.WORDNO) + C(ITP.WORDNO) + C(R) => TPR.CA

C(PRn.SEGNO) => C(TPR.TSR)

C(ITP.BITNO) => C(TPR.BITNO)

MAX(PRn.RN,SDW.R1,TPR.TRR) => C(TPR.TRR)

```

where PRn is ITP.PRNUM. Further indirection is possible if ITP.MOD so indicates. C(R) is specified by a previous IR tag.

#### 5. The CALL6 Instruction

The new CALL6 instruction is provided as the only means by which a procedure segment may call a procedure in an inner ring (i.e., set PRR to a lower value). The CALL6 instruction is to be used in all standard inter-procedure calls and is intended to replace the transfer instruction as the last instruction of the standard Multics calling sequence.

The "6" of the CALL6 instruction specifies that the pair of pointer registers (6-7) is to be involved in the execution of the CALL6. (This use of a pair of PR's involves two full PR's (RN, SEGNO, WORDNO, and BITNO) and should not be confused with a 645 base register pair.) When the CALL6 instruction is used to transfer control to another ring, the segment number of the stack for the target ring is formed by concatenating DSBR.STACK to the left of the ring number of the target ring. The CALL6 instruction behaves as a TRA (transfer) instruction with the following exceptions.

- 5.1 The access checking for a CALL6 instruction allows PRR to be set to a lower value provided that the call is made from a ring within the call bracket of the target segment.

- 5.2 If an attempt is made to call a procedure in an outer ring (a relatively rare case) an access violation occurs. Due to the necessity of copying all arguments the standard call, save and return sequences cannot handle calls to outer rings without excessive software overhead. Therefore, calls to outer rings' procedures will continue to cause a fault to allow the system software to interpret the call.

- 5.3 At the beginning of the CALL6, the contents of PR6 are assumed to point to a location (i.e., the current stack frame) within the stack segment of the calling ring. During execution of the CALL6, the processor sets the contents of PR7 to point to word 0 of the stack segment of the target ring in one of two ways. (TPR.TRR contains the target ring number.)

5.3.1 If the call is to a procedure in the same ring PR7 is set to point to word zero of the current stack segment as follows.

PR6.SEGNO => PR7.SEGNO

00...00 => PR7.WORDNO, PR7.BITNO

TPR.TRR => PR7.RN

5.3.2 If the call is to an inner ring (TPR.TRR<PPR.PRR)

PR7 is set to point to word 0 of the stack segment of the target ring as follows.

DSBR.STACK | TPR.TRR => PR7.SEGNO 00...00 => PR7.WORDNO, PR7.BITNO TPR.TRR => PR7.RN

5.3.3 If an attempt is made to use CALL6 to transfer to an outer ring (TPR.TRR>PPR.PRR) an access violation fault will be generated. The only way control can be transferred to an outer ring is via the RTCD (Return Control Double) instruction (i.e., the hardware only permits inward calls and outward returns). Calls to outer rings can of course be hand coded to look like outward returns to the hardware.

#### The H6180 INSTRUCTION SET

The instruction set of the H6180 processor is basically a merger of the 645 and H6080 instruction sets with several new instructions added for dealing with the extended pointer (address) registers of the H6180 processor. The definition of the H6180 instructions set is constrained to meet two distinctly different objectives. The first objective is to provide H6080 object code compatibility sufficient to allow the running of complete H6080 operating systems (e.g., GCOS) on a stand-alone basis and to allow the efficient operation of H6080 slave programs under Multics. The second objective is to maintain sufficient compatibility with H645 object code to allow Multics, with minimal software changes, to run effectively on both the current H645 and the H6180 processors.

## 1. Compatibility of Pointer Registers with 645 Address Base Registers

The H6180 processor contains eight pointer registers (PRs) in place of the eight address base registers (ABRs) of the H645. By Multics convention, the ABRs of the 645 are always used as four internal/external ABR pairs. The control fields are set so that ABRO/ABR1, ABR2/ABR3, ABR4/ABR5, and ABR6/ABR7 function as "pointer registers," each capable of holding a complete word number/segment number address. By convention, the even-numbered ABR's are used as the internal ABR of the pair. Each PR on the H6180 processor behaves like a 645 ABR pair, and can hold a complete segmented address. This doubling of the number of pointer registers makes code generation by the language translators more straightforward, and makes it possible to produce object programs that are more efficient. It means, however, that a careful mapping of 645 ABR-manipulating order codes to the H6180 processor was required to maintain upward compatibility of object programs.

Two aspects of the compatibility problem must be considered: the use of these registers in the formation of instruction operand addresses, and the effect of instructions which manipulate them.

ABR-relative addressing is specified on the H645 by setting bit 29 of an instruction word to "1" and placing an ABR number in the segment tag field of the instruction (bits 0-2). The operand address calculation depends on whether the segment tag names the internal or the external ABR in a pair. If it names the internal ABR in some pair (i.e., 0, 2, 4, or 6), then both the word number from that ABR and the segment number from the paired external ABR participate in the formation of the operand address for the instruction. The effect is addressing relative to the complete address in the "pointer register" formed by the pair. If the segment tag names the external ABR in some pair (i.e., 1, 3, 5, or 7), then only the segment number from that external ABR is used and a word number of zero is assumed. The effect is addressing relative to the beginning of the segment since the word number portion in the internal ABR is ignored.

These two uses of ABR-pair "pointer registers" in operand address formation are possible because two ABR numbers are associated with each of the four "pointer registers" formed by pairs. Because there is not enough room in an instruction word to increase the size of the segment tag from three to four bits, only one number can be associated with each PR of the H6180 processor. Thus, addressing relative to the beginning of a segment through a PR which points to an arbitrary word within that segment is no longer possible. To address relative to the beginning of a segment on the H6180 processor a PR must first be explicitly loaded with a pointer to it, i.e., with the complete address of word zero of the segment.

To maintain upward compatibility of object programs, it was necessary to be able to construct object code that will do addressing relative to the beginning of a segment through a "pointer register" which will execute properly on both the H645 and the H6180 processor. The mapping of 645 ABR-manipulating order codes to the H6180 processor defined below shows how this goal was met with code that executes efficiently on both machines.

The second aspect of the compatibility problem was the effect of instructions which manipulate ABR-pair "pointer registers" on the These instructions may also be applied to either the internal or the external ABR in a pair. Generally, the effect of the instruction on the "pointer register" formed by the pair is different in the two cases. For example, the "Add to Address Base Register n" (ADBn) instruction has the different effects of adding to the word number and adding to the segment number in the "pointer register" formed by the pair, depending on whether the internal or external ABR of the pair is specified as "n", respectively. The other 645 instructions with this property are EABn, EAPn, LBRn, SBRn, STPn, and TSBn. In cases where both functions performed by one of these instructions are used by Multics, instructions are provided on the H6180 processor to perform both on PRs. In several cases, however, both functions are not used, and only one or the other is provided on the H6180 processor. The same order code is used to represent the same function on both machines in all cases.

Before proceeding to a description of the proposed order code mapping, it is necessary to define some notation. The term "effective address" is used with respect to the H645 to mean the word number from the complete address of the ultimate operand of an instruction. Because Multics users think in terms of complete addresses, however, there is a tendency for them to use this term to mean the complete address of the operand, rather than just the word number from the complete address. The "Effective Address to Pair n" (EAPn) instruction suggests this usage is also acceptable. To eliminate user confusion on this matter, the following definitions are made: contents of the temporary pointer register (TPR) at the conclusion of an operand address formation is called the effective pointer The ring number (TRR), segment number (TSR), word number (CA), and bit number in the TRR are called the effective ring (er), effective segment (es), effective address (ea), and effective bit (eb), respectively. The following diagram summarizes this notation.

The mapping of order codes for manipulating pointer registers can now be considered. The PRs of the H6180 processor are numbered PRO through PR7, and the order code mapping will associate PRO, PR2, PR4, and PR6 with the ABRO/ABR1, ABR2/ABR3, ABR4/ABR5, and ABR6/ABR7 "pointer registers" of the 645, respectively. The 645 instruction set includes 59 order codes for manipulating paired and unpaired ABRs. These are grouped as 10 mnemonic instructions. They are mapped to 82 order codes grouped as 12 instructions on the H6180 processor. The ten 645 instructions are considered in alphabetic order.

ADBn - Add to Address Base Register n

Summary:

$$C(Y)_{0-17} + C(ABRn)_{0-17} => C(ABRn)_{0-17}$$

If n is even, then this instruction adds to the word number in the internal ABR of a pair. If n is odd, then it adds to the segment number in the external ABR of a pair. The first function is used by Multics and is duplicated on the H6180 processor. The second function is meaningless with respect to Multics and is not duplicated. The four order codes thus freed are reused to provide the add-to-word-number function for the four additional PRs on the H6180 processor. The result is the H6180 processor instruction:

ADWPn - Add to Word Number Field of PRn (old ADBn order codes)

$$C(Y)_{0-17} + C(PRn.WORDNO) => C(PRn.WORDNO)$$

$00...0 => C(PRn.BITNO)$

# <u>EABn</u> - <u>Effective</u> <u>Address</u> to <u>Base</u> n

Summary: EA =>  $C(ABRn)_{0-17}$

If n is even, then this instruction replaces the word number in the internal ABR of a pair with the effective address (word number from the complete address) of the operand of the instruction. If n is odd, then it replaces the segment number in the external ABR of a pair with the effective address. Both functions are used by Multics. They provide the best way of loading a pair with a complete address represented as a pair of integers. For example, if a segment number is contained in word "temp" as an integer and a word number is contained in word "temp+1" as an integer, then the sequence:

1daq temp place the integers in the A and Q

eab0 0,ql put second integer in internal ABR of pair 0/1

eab1 0,al put first integer in external ABR of pair 0/1

loads the ABRO/ABR1 "pointer register" with the complete address represented by the segment number and the word number. Both functions of the EABn instruction are provided on the 6180 The order codes for EABO, EAB2, EAB4, and EAB6 processor. become EAWPO, EAWP2, EAWP4 and EAWP6, respectively. tion, "Effective Address to Word Number Field of PRn", is described below. New order codes are provided for EAWP1, EAWP3, EAWP5, and EAWP7. The order codes for EAB1, EAB3, EAB5, and EAB7, become EASP0, EASP2, EASP4, and EASP6, respectively. instruction, "Effective Address to Segment Number Field of PRn", is described below. New order codes are provided for EASP1, EASP3, EASP5, and EASP7. The mapping of, say, EAB1 to EASPO is correct, for EABl updates the segment number portion of  $t\overline{h}e$  ABR0/ABR1 "pointer register" and EASP0 does the same to the corresponding PR (which is PRO) of the H6180 processor. With this mapping, the object form of the instruction sequence given in the example above performs the same function on both machines. A summary of these two H6180 processor instruction is:

EASPn - Effective Address to Segment Number Field of PRn (EABl, 3, 5, 7 and 4 new codes)

EA => C(PRn.SEGNO)

EAWPn - Effective Address to Word Number Field of PRn (EAB0, 2, 4, 6 and 4 new codes)

EA => C(PRn.WORDNO)

EB => C(PRn.BITNO)

#### <u>EAPn</u> - <u>Effective Address</u> to <u>Pair</u> n

to this section).

Summary: If  $C(ABRn)_{21} = "1"$  then ES =>  $C(ABRn)_{0-17}$

If  $C(ABRn)_{21} = "0"$  then  $EA \Rightarrow C(ABRn)_{0-17}$  and  $ES \Rightarrow C(ABRm)_{0-17}$

where "m" is the external ABR associated with the internal ABRn

If n is even, then C(ABRn) = "0" will be true and this instruction replaces the word number/segment number in the ABRn/ABRn+1 "pointer register" with the word number and segment number from the complete address of the operand of the instruction. If n is odd, then C(ABRn) = "1" will be true and only the segment number from the complete operand address replaces the segment number in the specified external ABR of a pair. The first function of the EAPn instruction is frequently used in Multics object programs, and is provided on the H6180 processor. The second function is infrequently used and is not duplicated on the follow-on processor. Instead, the order codes for EAP1, EAP3, EAP5, and EAP7 are used to solve the compatibility problem caused by lack of room in which to expand the segment tag field of an instruction from three bits to four bits to match the increased number of pointer registers (see above in the introduc-

Taking these ideas one at a time, the order codes for EAPO, EAP2, EAP4, and EAP6 become EPP0, EPP2, EPP4, and EPP6, respectively, on the H6180 processor. This instruction, "Effective Pointer to PRn", is described below. New order codes are provided for EPP1, EPP3, EPP5, and EPP7.

Next, before using the order codes of EAP1, EAP3, EAP5, and EAP7 to provide a different function on the H6180 processor, it must be shown that the function provided by them can be duplicated with other instructions. Consider an example of the occurrence of the instruction:

eap3 coperand > replace segment number in the 2/3 pointer

register with the segment number of

operand

This instruction can be replaced with three instruction sequence:

eaa ABR2 | 0 word number from 2/3 to au

eap2 <operand> complete address of operand to the 2/3

pointer register

eab2 0,au replace word number with number saved in

au

The same sort of thing could be done using one of the index registers rather than the accumulator. Because the EAPn instruction is very seldom used with n specified as odd, the inefficiency of replacing one instruction with three is of no concern. The order code for EAPn with n odd is used to provide a different function on the H6180 processor.

The different function is one that is not provided by a single instruction on the H645. The new instruction is EPBPn: Effective Pointer at Segment Base to PRn. The ring number and segment number from the effective pointer at the instruction's operand are placed in the RINGNO and SEGNO fields of PRn and the WORDNO and BITNO fields are set to zero. This generates in PRn a pointer at the beginning of the segment containing the operand of the instruction. The order codes for EAP1, EAP3, EAP5, and EAP7 are mapped to EPBP1, EPBP3, EPBP5, and EPBP7, respectively. New order codes are provided for EPBP0, EPBP2, EPBP4, and EPBP6. Note that the mapping here is different than for the case of EABn for n odd. EABl mapped to EASP0, but EAPl maps to EPBP1. The reason for this is so that the EPBPn instruction can solve the compatibility problem. As has been described, code sequences of the form (where n is even):

eapn <operand> pointer at operand to pair n/n+l

<opcode> ABRn+1 | m, <modifier>

reference relative to the beginning of the segment pointed into by ABRn/ABRn+1

will no longer work on the H6180 processor. (The object form of the second instruction in the sequence will generate a reference relative to PRn+1 and the first instruction in the sequence loaded PRn.) This sequence can be made to work on both machines by inserting a third instruction. The modified 645 instruction sequence is:

eapn <operand>

...

eapn+1 ABRn | 0 effectively does nothing on the 645

...

<operand>

ABRn+1 | m, <modifier>

On the H6180 processor the object form of the above sequence is the same as that generated by the following sequence of the H6180 processor instructions:

eppn <operand> pointer at operand to PRn

.

epbpn+l PRn | 0 pointer at beginning of operand segment to PRn+l

The effect of the sequence is the same on both machines and although the mnemonics are different, the order codes used are, in fact, the same. Thus, the strange mapping of the EAP1, EAP3, EAP5, and EAP7 instructions solves this problem of compatibility between the 645 and the H6180 processor.

The two instructions for the H6180 processor generated from EAPn are summarized as:

EPBPn - Effective Pointer at Segment Base to PRn (EAP1, 3, 5, 7, and 4 new codes)

er => C(PRn.RINGNO)

es => C(PRn.SEGNO)

00...0 => C(PRn.WORDNO), C(PRn.BITNO)

EPPn - Effective Pointer to PRn (EAP0, 2, 4, 6 and 4 new codes)

ep => C(PRn)

<u>LBRn</u> - <u>Load</u> <u>Base</u> <u>Register</u> n

Summary:  $C(Y)_{0-23} \Rightarrow C(ABRn)$

This instruction manipulates single ABRs, and ignores the pairing specified by the control fields. It is infrequently used and is <u>not</u> duplicated on the H6180 processor. The order codes thus freed are used for a new function on the H6180 processor: loading a pointer register from a segment number and word number stored in a single word as a "packed pair". This new instruction is summarized below:

<u>LPRPn</u> - Load Pointer Register from Packed Pointer into PRn (old codes for LBRn)

er => C(PRn.RINGNO)

$C(Y)_{6-17} => C(PRn.SEGNO)$

$C(Y)_{18-35} => C(PRn.WORDNO)$

$C(Y)_{0-5} => C(PRn.BITNO)$

#### LDB - Load Bases

Summary:

$$C(Y,Y+1,...,Y+7)_{0-23} \Rightarrow C(ABR0,ABR1,...,ABR7)$$

The analog of this instruction on the H6180 processor loads the eight PRs from eight consecutive ITS pairs. The decision to load from ITS pairs is made because each pointer register is longer than 36 bits and thus requires two words of storage in any case, and storing and loading the PRs from ITS pairs allows the stored images to be used as indirect addresses. The new instruction has the following summary:

<u>LPRI</u> - Load Pointers from ITS Pointers into Pointer Registers (old LDB)

"lpri loc" is equivalent to the following sequence assuming "loc" is the address (zero mod 16) of a vector of eight ITS pairs:

#### LDCF - Load Control Field

This instruction has no use with respect to PRs, and is dropped. The order code is freed for other use.

# <u>SBRn - Store Address Base Register n</u>

This instruction is the inverse of the 645 LBRn instruction, and is mapped to the inverse of the H6180 processor LPRPn instruction.

SPRPn - Store PRn in Packed Pointer format (old codes for SBRn)

$$C(PRn.BITNO) => C(Y)_{0-5}$$

$$C(PRn.SEGNO) => C(Y)_{6-17}$$

$$C(PRn.WORDNO) => C(Y)_{18-35}$$

#### STB - Store Bases

This instruction is the inverse of the 645 LDB instruction and is mapped to the inverse of the H6180 processor LPRI instruction.

SPRI - Store Pointers Register in ITS format (old STB)

"spri loc" is equivalent to the following sequence assuming "loc" is a zero mod 16 address:

spri0 loc spri1 loc+2 . . spri7 loc+14

# <u>STPn - Store Pair n</u>

Summary: If

$$C(ABRn)_{21} = "0"$$

then

$$C(ABRm)_{0-17} \Rightarrow C(Y)_{0-17}, 00...0 \Rightarrow C(Y)_{18-29},$$

$$ITS \text{ tag } (100011) \Rightarrow C(Y)_{30-35}$$

$$C(ABRn)_{0-17} \Rightarrow C(Y+1)_{0-17}, 00...0 \Rightarrow C(Y+1)_{18-35}$$

If  $C(ABRn)_{21} = "1"$  then

$$C(ABRn)_{0-17} \Rightarrow C(Y)_{0-17}, 00...0 \Rightarrow C(Y)_{18-29},$$

$$ITS \text{ tag } (100011) \Rightarrow C(Y)_{30-35}$$

$$00...0 \Rightarrow C(Y+1)$$

where ABRm is the external base paired with ABRn and Y is a zero mod 2 address.

This instruction is another of those with two functions, depending whether the internal or external ABR of pair is specified by "n". If n is even, then  $C(ABRn)_{21} = "0"$  will be true and the instruction causes the contents of the ABR pair "pointer register" including this ABR to be stored as an ITS pair. The ITS pair will contain the complete address from the pair. On the other hand, if n is odd then  $C(ABRn)_{21} = "1"$  will be true and an ITS pair is produced that contains only the segment number from the

pair is produced that contains only the segment number from the specified external ABR in a pair and a word number of zero. Both functions are provided on the H6180 processor. The order codes for STPO, STP2, STP4, and STP6 become SPRIO, SPRI2, SPRI4, and SPRI6 on the H6180 processor, respectively. This instruction, "Store Pointer from PRn" in ITS format, is described below. New order codes are provided for SPRI1, SPRI3, SPRI5, and SPRI7. The order codes for STP1, STP3, STP5, and STP7 become SPBP0, SPBP2, SPBP4, and SPBP6 on the H6180 processor. This instruction, "Store Pointer at Segment Base from PRn", is described below. New order codes are provided for SPBP1, SPBP3, SPBP5, and SPBP7. The mapping here is similar to the mapping described earlier for the 645 EABn instruction.

SPRIn - Store Pointer from PRn in ITS format (STP0, 2,

4, 6 and 4 new codes)

$000 => C(Y)_{0-2}$

PRn.SEGNO =>  $C(Y)_{3-17}$

$PRn.RN => C(Y)_{18-20}$

$00...0 => C(Y)_{21-29}$

ITS flag (100011) =>  $C(Y)_{30-35}$

PRn.WORDNO =>  $C(Y+1)_{0-17}$

$00...0 \Rightarrow C(Y+1)_{18-20}$

PRn.BITNO =>  $C(Y+1)_{21-26}$

$00...0 = C(Y+1)_{27-35}$

SPBPn - Store Pointer at Segment Base from PRn (STP1, 3, 5, 7, and 4 new codes). Same as SPRIn except:

00...0 => C(Y+1)

TSBn - Transfer and Set Base n

Summary: If  $C(ABRn)_{21} = "0"$  then  $C(IC) + 00...01 => C(ABRn)_{0-17}$  $C(PBR) => C(ABRm)_{0-17}$ , EA => C(IC), ES => C(PBR)

where n and m are the designated internal and linked external ABR's, respectively

IF  $C(ABRn)_{21} = "1"$  then  $C(PBR) => C(ABRn)_{0-17}$ , EA => C(IC), ES => C(PBR)

Of the two functions performed by this instruction, only that associated with n even is useful under Multics. The function performed when n is odd is not duplicated on the H6180 processor. The order codes thus freed are used to provide the first function for the additional four PRs. Thus, the following instruction is defined:

TSPn - Transfer and Set PRn (old TSBn order codes)

C(PRR) => C(PRn.RINGNO)

C(PSR) => C(PRn.SEGNO)

C(IC) + 1 => C(PRn.WORDNO)

$000000 \Rightarrow C(PRn.BITNO)$

es => C(PSR)

ea => C(IC)

## 2. Other Modifications to the H645 Instruction Set

With the exception of the instructions discussed earlier and those listed below, all H645 and H6080 instructions are interpreted by the H6180 as specified in their respective processor manuals. The instructions listed below have been modified from their H645 versions. Detailed instruction writeups of all modified unprivileged instructions are provided in section 4.

#### LBAR - Load Base Address Register

This instruction causes a "635 Compatibility" fault on the H645. On the H6180 the BAR is loaded with the specified values. LBAR is an unprivileged instruction when the H6180 is in Multics mode but is privileged when the H6180 is in GCOS (H6080) mode.

#### RCCL - Read Calendar Clock

The manner in which the processor port number is specified by the RCCL is greatly simplified.

#### RET, STC1, STI, and LDI Instructions

These instructions have all been modified to deal with the expanded number of indicators which are maintained in the H6180.

#### RTCD and STCD Instructions

These instructions no longer save and reload the indicators on the H6180. (Indicators are no longer saved accross a call by the standard CALL, SAVE, and RETURN macros.) In addition RTCD is modified to handle a return to an outer ring.

#### STAC - Store A Conditionally

This instruction is implemented using the limited read-alterrewrite (RAR) facility of the H6180. On the H645 an RAR instruction would delay any instruction until it completed its RAR cycle. On the H6180 an RAR instruction will only delay other RAR instructions but have no control over non-RAR instructions.

# TSS - Transfer and Set Slave

The TSS instruction allows an unprivileged user program to enter Multics BAR mode and transfer to H600/6000 slave programs to be run in BAR mode within the Multics environment.

#### 3. New Instructions

In addition to the EIS instructions the following new unprivileged instructions have been added to the H6180.

## EPAQ - Effective Pointer to AQ

The EPAQ instruction loads the full effective pointer (TRR, TSR, WORDNO, and bit number) into the AQ in a form such that each value is available for subsequent AU, AL, QU, or QL indexing operations.

## STACQ - Store A Conditional on Q

The STACQ instruction is designed as an eventual replacement for STAC as a locking instruction. If the contents of the operand word are equal to the contents of the Q register, the A register is stored in the operand word and the zero indicator is set on. Otherwise the operand is not modified and the zero indicator is set off.

# 4. Writeups of New and Modified Instructions

This section gives detailed instruction write-ups of all new or modified instructions with the exception of the EIS instructions which are documented in standard Honeywell 6000 line publications. Note that the H6000 line operation code field now includes bit 27 giving a 10-bit opcode field (600 line opcodes were restricted to 9 bits, 18-26). In the instruction writeups the opcode is given as XXX (Y) where XXX is the octal value of the first 9 bits of the field and Y is 0 or 1 depending on the value of bit 27 in the opcode. Thus the opcode for the H635 instruction LDA (H635 opcode 235) is written as 235 (0).

# 4.1 ADWPn - Add to Word Register of PRn

| Mnemonic | Name of Instruction         | Op Code (octal)                                     |

|----------|-----------------------------|-----------------------------------------------------|

| ADWPn    | Add to Word Register of PRn | 050 (0)<br>051 (0)<br>052 (0)<br>053 (0)<br>150 (0) |

|          |                             | 151 (0)<br>152 (0)<br>153 (0)                       |

Summary:  $C(Y)_{0-17} + C(PRn.WORDNO) => C(PRn.WORDNO)$  $00 \dots 00 => C(PRn.BITNO)$

The contents of memory location Y is added to the contents of the WORDNO field of Pointer Register n and the result replaces the contents of the WORDNO field. Zeros replace the contents of the BIT field of Pointer Register n. The rest of Pointer Register n remains unchanged.

Modifications: All except CI, SC, SCR

Indicators Affected: None

Illegal Procedure Fault:

Modifications: CI, SC, SCR

# 4.2 CALL6 - Call Instruction

| Mnemonic | Name of Instruction | Op Code (octal) |

|----------|---------------------|-----------------|

| CALL6    | Call (using PR6-7)  | 713 (0)         |

Summary:  $C(TPR) \Rightarrow C(PPR)$

> C(TPR.CA) => C(PPR.IC) C(TPR.TRR) => C(PR7.RN)

The SEGNO field of PR7 is replaced according to the TRR and PRR fields (see above) and the effective ring number, segment number and segment address replace the corresponding fields of the procedure pointer register.

Modifications: All except DU, DL, CI, SC, SCR

Indicators Affected: None

Illegal Procedure Fault:

Modifications: DU, DL, CI, SC, SCR

Note: If C(TRR) > C(PRR) an access violation fault is initiated and the instruction is not executed.

# 4.3 EASPn - Effective Address to Segment Number Field of PRn

Mnemonic Name of Instruction Op Code (octal)

EASPN Effective Address to Segment Number Field of PRn

311 (0)

310 (1)

313 (0)

312 (1)

331 (0)

330 (1)

333 (0)

332 (1)

Summary:  $EA_{3-17} \Rightarrow C(PRn.SEGNO)$

The least significant 15 bits of the effective address register replaces the contents of the SEGNO field of Pointer Register n. The rest of Pointer Register n remains unchanged.

Modifications: All except DU, DL, CI, SC, SCR

Indicators Affected: None

Illegal Procedure Fault:

Modifications: DU, DL, CI, SC, SCR

Note: This and EAWPn replace the 645 Effective Address to

Base n instruction.

# 4.4 EAWPn - Effective Address to Word/Bit Number Field of PRn

| Mnemonic | Name of Instruction                                  | Op Code (octal)                          |

|----------|------------------------------------------------------|------------------------------------------|

| EAWPn    | Effective Address to Word/Bit<br>Number Field of PRn | 310 (0)<br>311 (1)<br>312 (0)<br>313 (1) |

|          |                                                      | 330 (0)<br>331 (1)<br>332 (0)<br>333 (1) |

Summary: C(TPR.CA) => C(PRn.WORDNO) C(TPR.BITNO) => C(PRn.BITNO)

The calculated address and bit number replaces the contents of the word and bit number fields of Pointer Register n. The remaining fields of Pointer Register n remain unchanged.

Modifications: All except DU, DL, CI, SC, SCR

Indicators Affected: None

Illegal Procedure Fault:

Modifications: DU, DL, CI, SC, SCR

Note: This and EASPn replace the 645 Effective Address to Base n instruction.

# 4.5 <u>EPAQ</u> - <u>Effective</u> <u>Pointer</u> to <u>AQ</u> <u>Register</u>

Mnemonic Name of Instruction Op Code (octal)

EPAQ Effective Pointer to AQ Register 212 (0)

Summary:  $C(TPR) \Rightarrow C(AQ)_{00} - 17$

#### where:

00 ... 00 => C(AQ)<sub>0-2</sub>

C(TPR.TSR) => C(AQ)<sub>3-17</sub>

00 ... 00 => C(AQ)<sub>18-32</sub>

C(TPR.TRR) => C(AQ)<sub>33-35</sub>

C(TPR.CA) => C(AQ)<sub>36-53</sub>

00 ... 00 => C(AQ)<sub>54-65</sub>

C(TPR.BITNO) => C(AQ)<sub>66-71</sub>

Modifications: All except DU, DL, CI, SC, SCR

## Indicators Affected:

Zero If C(AQ) = 0, then ON; otherwise OFF

Illegal Procedure Fault:

Modifications: DU, DL, CI, SC, SCR

# 4.6 EPBPn - Effective Pointer at Base to PRn

| Mnemonic | Name of Instruction                 | Op Code (octal)                                                                      |

|----------|-------------------------------------|--------------------------------------------------------------------------------------|

| EPBPn    | Effective Pointer at Base<br>to PRn | 350 (1)<br>351 (0)<br>352 (1)<br>353 (0)<br>370 (1)<br>371 (0)<br>372 (1)<br>373 (0) |

Summary: C(TPR.TRR) => C(PRn.RN) C(TPR.TSR) => C(PRn.SEGNO) 00 ... 00 => C(PRn.WORDNO) 00 ... 00 => C(PRn.BITNO)

The ring number and segment number portion of the Effective Pointer (TPR) replace the contents of the RN and SEGNO fields of Pointer Register n. The contents of the WORDNO and BITNO fields of Pointer Register n are forced to zero.

Modifications: All except DU, DL, CI, SC, SCR

Indicators Affected: None

Illegal Procedure Fault:

Modifications: DU, DL, CI, SC, SCR

Note: This and EPPn replace the 645 Effective Address to Pair n instruction.

# 4.7 EPPn - Effective Pointer to PRn

| Mnemonic | Name of Instruction      | Op Code (octal)                                     |

|----------|--------------------------|-----------------------------------------------------|

| EPPn     | Effective Pointer to PRn | 350 (0)<br>351 (1)<br>352 (0)                       |

|          |                          | 353 (1)<br>370 (0)<br>371 (1)<br>372 (0)<br>373 (1) |

Summary:  $C(TPR) \Rightarrow C(PRn)$

C(TPR.TRR) => C(PRn.RN) C(TPR.TSR) => C(PRn.SEGNO) C(TPR.CA) => C(PRn.WORDNO) C(TPR.BITNO) => C(PRn.BITNO)

The ring number, segment number, bit number, and computed address of the Effective Pointer (TPR) replace the contents of the RN, SEGNO, WORDNO and BITNO fields of Pointer Register n.

Modifications: All except DU, DL, CI, SC, SCR

Indicators Affected: None

Illegal Procedure Fault:

Modifications: DU, DL, CI, SC, SCR

Note: This and EPBPn replace the 645 Effective Address to Pair n instruction.

# 4.8 LBAR - Load Base Address Register

| Mnemonic | Name of Instruction        | Ор | Code   | (octal) |

|----------|----------------------------|----|--------|---------|

| LBAR     | Load Base Address Register | :  | 230 (0 | )       |

Summary:  $C(Y)_{0-8} \Rightarrow BAR.BASE$   $C(Y)_{9-17} \Rightarrow BAR.BOUND$

BAR.BASE is the high order 9 bits of an 18-bit relocation constant (with 9 low order zeros) used to relocate effective address calculations when the processor is placed in BAR mode. BAR.BOUND specifies the number of 512-word logical blocks within the simulated "core image." A reference to a logical block above this bound will cause a store fault. The LBAR instruction is unprivileged when executed while the processor is in Multics mode.

Modifications: all except DU, DL, CI, SC, SCR

Indicators Affected: None

Illegal Procedure Fault:

# 4.9 LDI - Load Indicator Register

| Mnemonic | Name of Instruction     | Op Code (octal) |

|----------|-------------------------|-----------------|

| LDI      | Load Indicator Register | 634 (0)         |

Summary:  $C(Y)_{18-30} = C(IR)$

The relationship between  $C(Y)_{18-30}$  and the indicators is as follows:

| Bit Position C(Y) | Indicator             |

|-------------------|-----------------------|

| 18                | Zero                  |

| 19                | Negative              |

| 20                | Carry                 |

| 21                | Overflow              |

| 22                | Exponent Overflow     |

| 23                | Exponent Underflow    |

| 24                | Overflow Mask         |

| 25                | Tally Runout          |

| 26                | Parity Error          |

| 27                | Parity Mask           |

| 29                | Truncation            |

| 30                | Multi-Word Inst. Int. |

Modifications: All except CI, SC, SCR

The tally runout indicator will reflect C(Y) 25 regardless of what address modification is performed on the LDI instruction for tally opera-

tions.

### Indicators Affected:

| Parity Mask               | If corresponding bit in C(Y) is 1, and processor is in Privileged Mode, then ON; otherwise OFF. Indicator is NOT AFFECTED in the Non-Privileged Mode. |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bar Mode                  | Not affected                                                                                                                                          |  |

| Absolute Mode             | Not affected                                                                                                                                          |  |

| All other Indica-<br>tors | If corresponding bit in C(Y) is ONE, then ON; otherwise OFF.                                                                                          |  |

Illegal Procedure Fault:

Modifications: SC, SCR, CI

### 4.10 LPRI - Load Pointer Registers from ITS Pairs

| Mnemonic | Name of Instruction                      | Op Code (octal) |

|----------|------------------------------------------|-----------------|

| LPRI     | Load Pointer Registers<br>from ITS Pairs | 173 (0)         |

Summary:

$$C(Y, Y + 2, ..., Y + 14)_{00-71} => C(PR0, PR1, ..., PR7)$$

where:

MAX(Y+2n pair 18-20, SDW.Rl, TPR.TRR) => C(PRn.RN)

$C(Y + 2n pair)_{3-17} \Rightarrow C(PRn.SEGNO)$

$C(Y + 2n pair)_{36-53} => C(PRn.WORDNO)$

$C(Y + 2n pair)_{57-62} => C(PRn.BITNO)$

Starting at location Y, the contents of eight word pairs (in ITS pair format) replace the contents of Pointer Registers 0 thru 7 as shown. The hardware assumes  $Y_{14-17}^{=0000}$  (zero modulo 16) and addressing will be incremented accordingly. No check is made. The contents of the ITS word pairs loaded is unchanged.

Modifications: All except DU, DL, CI, SC, SCR

Indicators Affected: None

Illegal Procedure Fault:

Modifications: DU, DL, CI, SC, SCR

Note: This replaces the 645 Load Base Register instruction.

# 4.11 LPRPn - Load Pointer Register n Packed

Mnemonic Name of Instruction Op Code (octal)

| LPRPn | Load Pointer Register n Packed | 76n (0) |

|-------|--------------------------------|---------|

|       |                                |         |

Summary:  $C(Y)_{0-35} \Rightarrow C(PRn)$

where:

$C(TPR.TRR) \Rightarrow C(PRn.RNR)$   $C(Y)_{0-5} \Rightarrow C(PRn.BITNO)$   $X \mid C(Y)_{6-17} \Rightarrow C(PRn.SEGNO)$   $C(Y)_{18-35} \Rightarrow C(PRn.WORDNO)$

If the  $C(Y)_{6-17}$  is all ones, X will be llllll; if  $C(Y)_{6-17}$  is not all ones, X will be 000000.

Modifications: All except DU, DL, CI, SC, SCR

Indicators Affected: None

Illegal Procedure Fault:

# 4.12 RCCL - Read Calendar Clock

| Mnemonic | Name of Instruction | Op Code (octal) |

|----------|---------------------|-----------------|

| RCCL     | Read Calendar Clock | 633 (0)         |

Summary: 00 ... 00 =>  $C(AQ)_{0-19}$   $C(Calendar\ Clock)$  =>  $C(AQ)_{20-71}$  $C(Y)_{0-2}$  specify which Processor Port is to be used.

The contents of the clock in one of the System Controllers replaces the contents of the AQ register as shown. The contents of the clock is unchanged. The contents of the three most significant bits of the C(Y) specify which Processor Port (i.e., which System Controller) is to be used.

Modifications: All except DU, DL, CI, SC, SCR

Indicators Affected: None

Illegal Procedure Fault:

### 4.13 RET - Return

| Mnemonic | Name of Instruction | Op Code (octal) |

|----------|---------------------|-----------------|

| RET      | Return              | 630 (0)         |

Summary:  $C(Y)_{0-17} = C(IC)$ ;  $C(Y)_{18-31} = C(IR)$

The contents of the location specified by Y replace the contents of the Instruction Counter and Indicator Register. The Tally Runout indicator reflects the state of C(Y) 25

<u>prior</u> to address modification and is unaffected by any subsequent modification performed on the RET instruction. The relationship between  $C(Y)_{18-31}$  and the indicators are as follows:

| Bit Position C(Y) | Indicator             |

|-------------------|-----------------------|

| 18                | Zero                  |

| 19                | Negative              |

| 20                | Carry                 |

| 21                | Overflow              |

| 22                | Exponent Overflow     |

| 23                | Exponent Underflow    |

| 24                | Overflow Mask         |

| 25                | Tally Runout          |

| 26                | Parity Error          |

| 27                | Parity Mask           |

| 28                | Not (BAR Mode)        |

| 29                | Truncation            |

| 30                | Multi-word Inst. Int. |

| 31                | Absolute Mode         |

Modifications: All except DU, DL, CI, SC, SCR

#### Indicators Affected:

| Parity Mask               | Not affected                                               |

|---------------------------|------------------------------------------------------------|

| Bar Mode                  | Not affected                                               |

| Absolute Mode             | Not affected                                               |

| All other Indica-<br>tors | If corresponding bit in C(Y) is 1, then ON; otherwise OFF. |

Illegal Procedure Fault:

# 4.14 RTCD - Return Control Double

Mnemonic Name of Instruction Op Code (octal)

RTCD Return Control Double 610 (0)

Summary: C(Y pair) => C(PPR)

$C(Y pair)_{3-17} \Rightarrow C(PPR.PSR)$

$Max(C(Y)_{18-20}, C(TPR.TRR), C(SDW.Rl_v)) \Rightarrow C(PRR)$

$C(Y pair)_{36-53} \Rightarrow C(PPR.IC)$

If TPR.TRR>PPR.PRR, then TPR.TRR+PR0-7.RN, otherwise no change to RN

The contents of the word pair starting at location Y replaces the contents of the procedure segment and ring number. The hardware assumes  $Y_{17} = 0$ . No check is made. The contents of the word pair starting at location Y is unchanged.

Modifications: All except DU, DL, CI, SC, SCR

Indicators Affected: None

Illegal Procedure Fault:

### 4.14 SPBPn - Store Segment Base Pointer of PRn

Mnemonic Name of Instruction Op Code (octal)

SPBPn Store Segment Base Point of PRn 250 (1)

251 (0)

252 (1)

253 (0)

650 (1)

651 (0)

652 (1)

653 (0)

Summary: 000 => C(Y pair)<sub>0</sub> - 2 C(PRn.SEGNO) => C(Y pair)<sub>3</sub> - 17 C(PRn.RN) => C(Y pair)<sub>18</sub> - 20 00 ... 00 => C(Y pair)<sub>21</sub> - 29 43<sub>8</sub> => C(Y pair)<sub>30</sub> - 35 00 ... 00 => C(Y pair)<sub>36-71</sub>

The ring number and segment descriptor number currently in the Pointer Register n replace the contents of word pair starting at location Y as shown. The hardware assumes  $Y_{17} = 0$ . No check is made. The contents of Pointer Register n is unchanged.

Modifications: All except DU, DL, CI, SC, SCR

Indicators Affected: None

Illegal Procedure Fault:

Modifications: DU, DL, CI, SC, SCR

Note: This and SPRIn replace the 645 Store Pair n instruction.

# 4.15 <u>SPRI - Store Pointer Registers as ITS Pairs</u>

Mnemonic Name of Instruction Op Code (octal)

SPRI Store Pointer Registers as 254 (0)

ITS Pairs

Summary:  $C(PR0, PR1,...,PR7) => C(Y, Y+2,...,Y+14)_0 - 71$

where:

000 => C(Y+2n pair)<sub>0</sub> - 2 C(PRn.SEGNO) => C(Y+2n pair)<sub>3</sub> - 17 C(PRn.RN) => C(Y+2n pair)<sub>18</sub> - 20 00 ... 00 => C(Y+2n pair)<sub>21</sub> - 29 43<sub>8</sub> => C(Y+2n pair)<sub>30</sub> - 35 C(PRn.WORDNO) => C(Y+2n pair)<sub>36</sub> - 53 000 => C(Y+2n pair)<sub>54</sub> - 56 C(PRn.BITNO) => C(Y+2n pair)<sub>57</sub> - 62 00 ... 00 => C(Y+2n pair)<sub>63</sub> - 71

Starting at location Y, the contents of Pointer Registers 0 - 7 replace the contents of eight word pairs (in ITS pair format). The hardware assumes  $Y_{14} - 17 = 0000$  and addressing is incremented accordingly. No check is made. The contents of the Pointer Registers are unchanged.

Modifications: All except DU, DL, CI, SC, SCR

Indicators Affected: None

Illegal Procedure Fault:

Modifications: DU, DL, CI, SC, SCR

Note: This replaces the 645 Store Bases instruction.

### 4.16 SPRIn - Store Pointer Register n as ITS Pair

| Mnemonic | Name of Instruction                     | Op Code (octal)    |

|----------|-----------------------------------------|--------------------|

| SPRIn    | Store Pointer Register n<br>as ITS Pair | 250 (0)<br>251 (1) |

| <u> </u> |                                         | 252 (0)<br>253 (1) |

|          |                                         | 650 (0)<br>651 (1) |

|          |                                         | 652 (0)<br>653 (1) |

Summary:  $C(PRn) \Rightarrow C(Y)_{0} - 71$

where:

The contents of Pointer Register n replaces the contents of the word pair (in ITS format) starting at location Y. The hardware assumes  $Y_{17} = 0$ . No check is made. The contents of the Pointer Register n are unchanged.

Modifications: All except DU, DL, CI, SC, SCR

Indicators Affected: None

Illegal Procedure Fault:

Modifications: DU, DL, CI, SC, SCR

Note: This and SPBPn replace the 645 Store Pair n instruction.

# 4.17 SPRPn - Store Pointer Register n Packed

| Mnemonic | Name of Instruction             | Op Code (octal) |

|----------|---------------------------------|-----------------|

| SPRPn    | Store Pointer Register n Packed | 54n (0)         |

Summary:  $C(PRn) => C(Y)_{0-35}$

where:

$C(PRn.BITNO) => C(Y)_0 - 5$   $C(PRn.SEGNO)_{3-14} => C(Y)_6 - 17$  $C(PRn.WORDNO) => C(Y)_{18} - 35$

The contents of Pointer Register n replace the contents of location Y as shown. The contents of Pointer Register n are unchanged.

Modifications: All except DU, DL, CI, SC, SCR

Indicators Affected: None

Illegal Procedure Fault:

Modifications: DU, DL, CI, SC, SCR

If the 3 most significant bits of  $C(PRn.SEGNO) \neq 000$  and  $C(PRn.SEGNO) \neq to$  all one's (Null Pointer).

Note: This replaces the 645 Store Address Base Register n instruction.

### 4.18 SREG - Store Registers

| Mnemonic | Name of Instruction | Op Code (octal) |

|----------|---------------------|-----------------|

| SREG     | Store Registers     | 753 (0)         |

Summary: C(X0,X1,...,X7,A,Q,E,TR) = C(Y,Y+1,...,Y+7)where Y must be a 0 modulo 8 address.\*

The contents of the Index (X0-X7), A, Q, E, and TR registers are stored in successive locations beginning at Y and ending at Y+7 in the following format:

$$C(X0) \Rightarrow C(Y)_{0-17}$$

$C(A) \Rightarrow C(Y+4)_{0-35}$

$C(X1) \Rightarrow C(Y)_{18-35}$   $C(Q) \Rightarrow C(Y+5)_{0-35}$

$C(X2) \Rightarrow C(Y+1)_{0-17}$   $C(E) \Rightarrow C(Y+6)_{0-7}$

$C(X3) \Rightarrow C(Y+1)_{18-35}$   $C(X4) \Rightarrow C(Y+2)_{0-17}$   $C(X5) \Rightarrow C(Y+2)_{18-35}$   $C(X5) \Rightarrow C(Y+2)_{18-35}$   $C(X6) \Rightarrow C(Y+3)_{0-17}$   $C(X7) \Rightarrow C(Y+3)_{18-35}$

Modifications: All except DU, DL, CI, SC, SCR

Indicators Affected: None

Illegal Procedure Fault:

<sup>\*</sup>The hardware assumes  $Y_{15-17} = 000$  and addressing is incremented accordingly. No check is made.

# 4.19 STAC - Store A Conditional

| Mnemonic | Name of Instruction | Op Code (octal) |

|----------|---------------------|-----------------|

| STAC     | Store A Conditional | 354 (0)         |

Summary: Test C(Y) Then:

1) if C(Y) = 0, C(A) = C(Y), Zero indicator set ON 2) if  $C(Y) \neq 0$ , Zero indicator set OFF

If the initial C(Y) is non-zero then C(Y) are not changed by this instruction.

Modifications: All types except DU, DL, CI, SC, SCR

Indicators Affected:

Zero If initial C(Y) = 0, then ON; otherwise OFF

Illegal Procedure Fault:

Modifications: DU, DL, CI, SC, SCR

# 4.20 STACQ - Store A Conditional on Q

| Mnemonic | Name of Instruction           | Op Code | (octal) |

|----------|-------------------------------|---------|---------|

| STACQ    | Store A Conditional-C(Y)=C(Q) | 654     | (0)     |

Summary: Test C(Y) Then:

- 1) if C(Y) = C(Q),  $C(A) \Rightarrow C(Y)$ , Zero indicator set ON

- 2) if  $C(Y) \neq C(Q)$ , Zero indicator set OFF

If the initial C(Y) is  $\neq C(Q)$  then C(Y) are not changed by this instruction.

Modifications: All types except DU, DL, CI, SC, SCR

Indicators Affected:

Zero If initial C(Y) = C(Q), then ON; otherwise OFF

Illegal Procedure Fault:

### 4.21 STC1 - Store Instruction Counter Plus 1

Mnemonic Name of Instruction Op Code (octal)

STC1 Store Instruction Counter plus 1 554 (0)

Summarus C(IC) + 0 01 = C(Y)

Summary:  $C(IC) + 0 ... 01 = C(Y)_{0-17}$   $C(IR) \Rightarrow C(Y)_{18-31}$  $00 ... 0 = C(Y)_{32-35}$