#### DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

# VHDL - Esempi

Martedì 13 Gennaio 2009

- Un process è un'istruzione concorrente che contiene un'area sequenziale.

- Un processo viene eseguito parallelamente alle altre istruzioni concorrenti.

- L'esecuzione del suo body può essere condizionata da una sensitivity list, una lista di segnali.

- La sensitivity list non si usa quando il body contiene un'istruzione wait.

- In questo caso l'esecuzione viene avviata e si sospende nel modo indicato da wait.

#### Note:

- I segnali assegnati all'interno di un processo ricevono il valore solo dopo la sospensione del processo.

- In un processo le variabili locali conservano in proprio valore nel tempo tra un'esecuzione e l'altra.

```

p1: process (B, C)

begin

A <= B and C;

C <= '0';

end;

```

```

p1_2: process

begin

A <= B and C;

C <= '0';

wait on B, C;

end;

```

#### Struttura generale di un programma

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

```

use libreria

entity circuito is

end circutio;

architecture archi of circuito is

-- istruzione concorrente 1

-- istruzione concorrente 2

begin

pa: process

begin

Area sequenziale

-- istruzione sequenziale pa_1

-- istruzione sequenziale pa_2

Area concorrente

end:

pb: process

begin

Area sequenziale

-- istruzione sequenziale pa_2

end;

end;

```

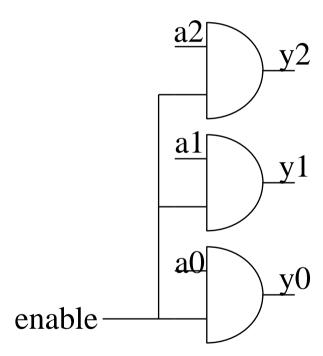

#### Controllo dei processi: IF-THEN-ELSE

```

SIGNAL a : STD_LOGIC_VECTOR(2 downto 0);

```

SIGNAL y: STD\_LOGIC\_VECTOR(2 downto 0);

SIGNAL enable: STD\_LOGIC;

```

PROCESS( enable)

BEGIN

IF (enable = '1') THEN

y <= a;

ELSE

y <= "000";

END IF;

END PROCESS;

```

#### Controllo dei processi: CASE

```

SIGNAL a : STD_LOGIC;

SIGNAL y: STD_LOGIC;

SIGNAL enable: STD_LOGIC_VECTOR(1 downto 0);

PROCESS (enable)

BEGIN

CASE enable IS

WHEN "00" =>

V \leq a;

WHEN "01" =>

y \le 0';

WHEN "10" =>

y \le 0';

WHEN OTHERS =>

V <= '1';

END CASE;

END PROCESS;

```

#### Controllo dei processi: CASE - DECODER

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

```

SIGNAL y: STD_LOGIC_VECTOR(3 downto 0);

SIGNAL a: STD_LOGIC_VECTOR(1 downto 0);

PROCESS (a)

BEGIN

CASE a IS

WHEN "00" =>

y <= "0001";

a1

WHEN "01" =>

DECODE

v <= "0010";

a0

y1

R

WHEN "10" =>

y0

y \le "0100";

WHEN "11" =>

y \le "1000";

WHEN OTHERS => ;

END CASE;

END PROCESS;

```

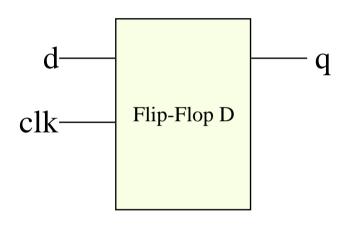

### Circuiti Sequenziali: FF-D

```

POLITECNICO

DI MILANO

```

```

entity ffd is

port(

in std_logic;

d:

in std_logic;

clk:

out std_logic

q:

end ffd;

ARCHITECTURE arch OF ffd IS

BEGIN

PROCESS(clk)

BEGIN

IF (clk'EVENT AND clk = '1') THEN

q \ll d;

END IF;

END PROCESS;

END arch;

```

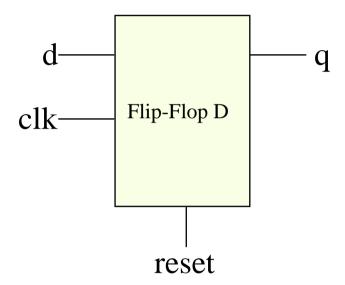

#### Circuiti Sequenziali: FF-D con RESET

```

POLITECNICO

DI MILANO

```

```

entity ffd is

port(

d:

in std_logic;

clk:

in std_logic;

in std_logic;

reset:

out std_logic

q:

end ffd;

ARCHITECTURE arch OF ffd IS

BEGIN

PROCESS(clk, reset)

BEGIN

IF (reset = '1') THEN

q \le 0;

ELSIF (clk'EVENT AND clk = '1') THEN

q \ll d;

END IF;

END PROCESS;

END arch;

```

```

ARCHITECTURE arch OF counter IS

BEGIN

PROCESS(clk, reset)

BEGIN

IF (reset = '1') THEN

q \le '000';

ELSIF (clk'EVENT AND clk = '1') THEN

IF q \ge 9 THEN

q \le '000';

ELSE

q \le q + 1;

END IF;

END IF;

END PROCESS;

END arch;

```

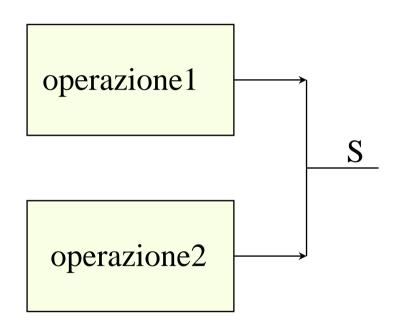

```

ARCHITECTURE arch OF circ IS

SIGNAL s : BIT;

BEGIN

PROCESS

BEGIN

s <= operazione1;

END PROCESS;

PROCESS

BEGIN

s <= operazione2;

END PROCESS;

END arch;

```

#### DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

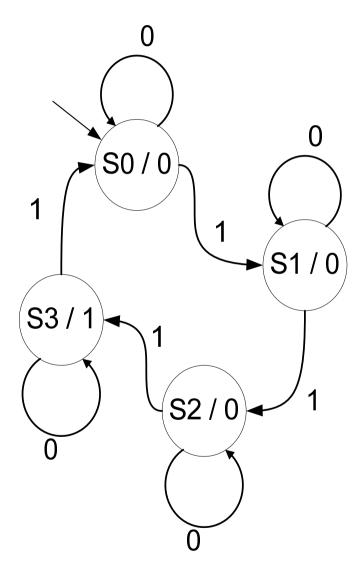

# Macchina a stati finiti: FSM

```

library ieee;

use ieee.std_logic_1164.all;

entity seq_design is

port(

in std_logic;

a:

clock:

in std_logic;

in std_logic;

reset:

out std_logic

X:

end seq_design;

```

```

\

```

## FSM 2/4 – Architecture: process#1

```

architecture FSM of seg design is

-- define the states of FSM model

type state_type is (S0, S1, S2, S3);

signal next state, current state: state type;

begin

-- cocurrent process#1: state registers

state_reg: process(clock, reset)

begin

if (reset='1') then

current state <= $0;

elsif (clock'event and clock='1') then

current_state <= next_state;</pre>

end if;

end process;

```

### FSM 3/4 – Architecture: process#2

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

```

-- cocurrent process#2: combinational logic

comb_logic: process(current_state, a)

begin

-- use case statement to show the

-- state transistion

case current state is

when S0 =>

x \le '0';

if a='0' then

next_state <= S0;

elsif a ='1' then

next_state <= S1;</pre>

end if:

when S1 =>

x <= '0':

if a='0' then

next state <= S1;

elsif a='1' then

next_state <= S2;</pre>

```

end if;

## FSM 4/4 – Architecture: process#2

DIPARTIMENTO DI ELETTRONICA E INFORMAZIONE

```

when S2 =>

x <= '0';

if a='0' then

next state <= S2;

elsif a='1' then

next state <= S3;

end if:

when S3 =>

x <= '1';

if a='0' then

next state <= S3;

elsif a='1' then

next_state <= S0;

end if;

when others =>

x \le '0';

next state <= S0;

end case;

end process;

end FSM;

```

- ISE WebPACK è un tool gratuito e scaricabile dal web che supporta la scrittura, la sintesi e la verifica di specifiche in HDL sia per CPLD che FPGA.

- E' possibile scaricarlo gratuitamente da:

- www.xilinx.com