# **Exo-GPU: Safe, Imperative, User-schedulable Programming** for Tensor Cores

# ANONYMOUS AUTHOR(S)

Modern GPUs require not only SIMT-style parallelism but also software-managed concurrency between compute and data movement to reach maximum performance. Performance engineers must reason about subdividing work into the hierarchy of computation resources (threads, warps, warpgroups, blocks, clusters), and, in many cases, also must use asynchronous tensor core and memcpy instructions on different levels of the memory hierarchy (registers, tensor core accumulators, shared memory, global memory). Unlike CPUs, where out-of-order execution is managed by hardware and hidden from programmers, GPUs expose explicit instruction reordering to software through these asynchronous instructions. Well-established GPU programming languages generally offer either direct low-level control without safety guarantees (e.g., CUDA C++ inline assembly or intrinsics) or easier-to-analyze, high-level abstractions (e.g., Triton's tile-based model) that hide asynchronous instructions in the compiler backend, which may prevent performance engineers from maximizing performance by tuning critical details.

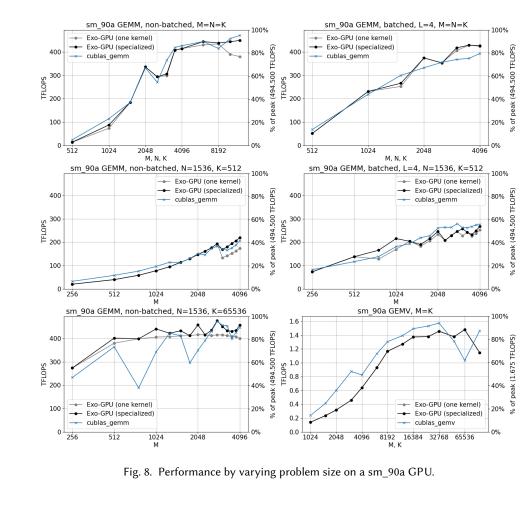

We propose Exo-GPU, an imperative, low-level language that creates minimal abstraction over CUDA. Our key idea is to treat parallelism and synchronization as mere annotations on sequential code rather than as fundamental control flow primitives, enabling verification that these constructs do not alter the program semantics. The benefit is two-fold: programmers can reason about code without hidden control flow or mutation, while allowing the Exo-GPU compiler to verify *sequential-parallel equivalence*—guaranteeing that parallel execution is functionally equivalent to its sequential interpretation. We used Exo-GPU to author GEMM kernels for the H100 GPU, using wgmma, TMA, and split-k. Our kernels achieved over 80% of theoretical peak on large problem sizes, in some cases outperforming the vendor-provided CUBLAS library.

## 1 INTRODUCTION

Starting with Tensor Cores introduced in NVIDIA's Volta generation of GPUs [13], the menu of tensor-specialized features in NVIDIA GPUs has expanded to encompass automated bulk movement of multidimensional data, distributed shared memory, and new asynchronous tensor cores supporting large-scale (up to  $64 \times 256$ ) matrix accumulation in a single instruction [18]. This poses ever-increasing challenges for authoring correct, top-performing CUDA code. Not only must algorithms be rewritten to migrate work from traditional SIMT-style code to target these specialized instructions, but also, these instructions expose explicit out-of-order instruction execution to the programmer, moving synchronization that was traditionally the responsibility of the hardware (e.g., through scoreboarding) to the programmer.

High-level kernel programming languages, such as Triton [24], provide a popular approach for taming this complexity. Triton's tile-based, automatically-parallelized programming model reduces the risk of programmer error by moving responsibility for correct usage of bulk data movement and synchronization instructions into the compiler. However, in practice, groundbreaking algorithms, such as the original FlashAttention 3 [21], are often written directly in CUDA C++ for greater control. On the one hand, CUDA C++ provides direct control over features such as asynchronous data movement and warp specialization required for optimal GPU usage. On the other hand, CUDA C++ exposes programmers to a variety of potential bugs, which we broadly categorize as:

- (1) Dataflow Logic Bugs: Program optimization usually requires changing the storage or computation order of intermediate values, e.g. caching data in a faster memory, or reordering instructions to hide latency. A flawed optimization, such as an indexing bug in copying a tile, or exchanging two statements that don't commute safely, can change the functional behavior of the program.

- (2) *Instruction Logic Bugs*: Accelerator instructions won't work as intended if not used as specified by the hardware vendor. For example, wgmma tensor core instructions require data in a certain input format and uniform execution by a full warpgroup (128 aligned threads).

(3) Inter-Thread Synchronization Bugs: Garden-variety synchronization bugs involve two threads accessing the same memory location (with one access being a write) without ordering enforced by synchronization.

(4) *Intra-Thread Synchronization Bugs*: If one thread issues an asynchronous (async) instruction, and that *same thread* later issues another instruction (async or not) that operates on the same memory location, overlapped or reordered instruction execution can undermine correctness.

Our goal is to provide a programming model that gives CUDA-like control *without* accepting the risk of these bugs as a fact of life. Existing CUDA C++ libraries such as CuTe [14] and ThunderKittens [22] provide close-to-the-metal abstractions that minimize the risk of logic bugs, particularly data movement and instruction input format bugs; however, none of them support large-scale program analysis and synchronization checking of arbitrary input programs.

As a starting point for the Exo-GPU language design, we postulate that programs with *sequential semantics* are far easier to analyze, both by humans and by compilers. We define program behavior using standard sequential semantics, treating language features for parallelism and synchronization—including parallel for-loops across CUDA thread hierarchies and barrier statements—simply as *annotations* on sequential code. This design provides two key benefits: programmers can intuitively reason about their code without hidden control flow or side effects, and more importantly, compilers can verify whether synchronizations are legal; that is, they can verify these annotations do not alter the program behavior relative to its baseline sequential interpretation.

The Exo-GPU program, interpreted sequentially, serves as as the semantic baseline—defining what the user intends to compute. Parallelism annotations specify which threads execute which statement instances, while synchronization constructs specify how the user intends to uphold baseline behavior. This raises a question: what degree of safety and control does Exo-GPU provide? We define safety as sequential-parallel equivalence—ensuring that the parallel interpretation of a program matches the sequential one. Parallelism is explicitly controlled by the programmer's annotations, rather than being hidden and automated by the compiler. The Exo-GPU compiler's role is limited to verifying that the user-provided synchronization ensures equivalence.

Through collective analysis (Section 4), we annotate each statement with a *collective tiling*, specifying which thread(s) execute each statement instance. This enables static analysis of the thread assignment counts, ensuring instructions with thread convergence requirements (e.g. warp MMA) are used correctly. To ensure sequential-parallel equivalence, we simulate execution on an *abstract machine* (Section 5). The Exo-GPU program converts to an Abstract Machine program where data variables store access histories (reads and mutations) with their thread and async instruction *visibility*, rather than numeric values. Synchronization statements become meaningful only in the abstract machine, conditionally expanding the visibility of all prior recorded accesses.

We built Exo-GPU as an extension to Exo [7, 8], a user-schedulable language providing composable, checked rewrite rules for transforming sequential programs. Exo lacks GPU support, and we significantly extended its frontend language design, static analysis, semantics, and codegen to enable safe parallel program transformation. Treating parallel constructs as annotations over a sequential semantic baseline enabled us to reuse Exo's over 60 verified rewrites as-is, which allowed us to transform a simple sequential GEMM program into a complex GEMM kernel for the NVIDIA Hopper architecture, with every step of transformation verified via a *chain of equivalence*: Exo verified equivalence between the original  $p_1$  and the final  $p_n$  while ignoring all the synchronization constructs, and Exo-GPU verified functional equivalence between the parallel and sequential interpretations of  $p_n$ , checking the legality of the parallel and synchronous annotations (Section 2.3). Combining Exo's pre-existing checked rewrite rules with Exo-GPU's new language features and synchronization checking, we created a GEMM kernel achieving over 80% of theoretical peak for large problem sizes, in some cases outperforming the vendor-supplied CUBLAS library (Section 6).

#### 2 EXAMPLES AND SYSTEM OVERVIEW

# 2.1 Exo-GPU Language Overview

Exo-GPU is built on fundamental design goals of safe, performance transparent, and imperative GPU programming. Unlike other GPU abstractions that hide complexity, we make threads and most CUDA instructions explicit in the IR. We introduce three first-class frontend language features derived from our design principles: (i) parallel loops that explicitly map work to blocks/warps/threads, (ii) a distributed memory model with sharding and explicit memory space annotations, and (iii) explicit synchronization, including fences, split-barriers, and asynchronous operations.

**Parallel loops.** Exo-GPU exposes three kinds of loops. (1)  $seq(c_{lo}, c_{hi})$  is a sequential loop that iterates i from  $c_{lo}$  to  $c_{hi}-1$ . (2)  $cuda\_tasks(lo, hi)$  distributes iterations across CUDA clusters; on presm\_90 (H100) GPUs a cluster coincides with a single CTA (thread block). (3)  $cuda\_threads(lo, hi)$ , unit =  $\tau_u$ ) assigns iterations to subsets of threads inside the current cluster. The unit takes a parameter  $\tau_u$  that specifies the shape of the participating thread set but not concrete indices—for example,  $\tau_u$  =  $cuda\_warp$  denotes contiguous 32-thread groups with thread IDs 0–31, 32–63, 64–95, etc. (inclusive), while  $\tau_u$  =  $cuda\_thread$  denotes a single thread (see Figure 11).

Each loop body, conditional branch, with-block, or procedure defines a program scope. As part of collective analysis (Section 4), we annotate each scope with a collective tiling  $\omega \in \Omega$ . This describes a mapping between the control variable values and the thread collective (set of threads) assigned to execute statement instances in the scope (i.e. which threads execute which loop iterations). We say that a scope is a  $\tau_u$ -scope when

$\tau_u$  accurately describes the thread sets produced by the mapping. In the inset figure, the outermost parallel loop cuda\_tasks(0,37) creates scope-1 (which is a cluster scope, and, assuming clusterDim=1, also a CTA scope); nesting cuda\_threads(..., unit=cuda\_warp) creates scope-2 (warp scope); and nesting cuda\_threads(..., unit=cuda\_thread) creates scope-3 (single-thread scope). Statement instances in scope-3 are executed by one thread.

**Distributed Memory:** Exo-GPU exposes explicit allocation statements for data and barrier variables, annotated by memory type, e.g. x : f32[8] @ CudaRmem allocates a data array x of type f32 and size 8 in GPU register memory. Allocations can be *distributed*: a single logical object may be sharded across threads at multiple CUDA levels (e.g., per-thread register shards or per-CTA-in-cluster shared-memory shards). Threads must access only their owned shards except via explicit communication instructions (e.g., warp shuffles) or TMA multicast. This sharding is not annotated explicitly at the allocation, but deduced from the usage pattern of the variable; all deductions must be consistent, as enforced by distributed memory analysis (Section 4.1).

Inset right illustrates the motivation for this design. If the first loop was executed sequentially, tmp would hold A[31] after the first loop, so the second loop broadcasts that value to every B[i]. Languages like CUDA that implicitly duplicate local variables per thread would interpret the same code as a vector copy (B[i] = A[i]). While not necessarily error-prone, this design would be inappropriate for our goal of defining x

this design would be inappropriate for our goal of defining program behavior with sequential semantics. Hence, in Exo-GPU, storing a temporary value per-thread requires a sharded allocation of tmp; as written, the program is rejected by the analysis because a register-resident tmp cannot be read by different threads without (for example) a warp shuffle. If a user intends to express a vector copy (B[i] = A[i]) through register tmp, tmp requires explicit *distrubuted* allocation per thread (tmp:f32[32]) and the accesses must be per-thread (tmp[i]).

**Explicit Synchronization:** Many GPU instructions require additional explicit synchronization, but overly conservative barriers can cancel the performance benefits of concurrency. Exo-GPU provides two forms of synchronization: a blocking barrier via Fence, and split barriers via paired Arrive/Await. As with other statements, all synchronization statements execute in program order.

A Fence causes all threads in the current thread collective (warp, CTA, or cluster) to rendezvous. At warp scope it maps to \_\_syncwarp; at CTA scope it maps to \_\_syncthreads (as shown in the right-hand code inset). A Fence takes two synchronization–timeline parameters,  $\tau_s^{\rm pre}$  and  $\tau_s^{\rm post}$  (Figure 16). These timelines specify which memory operations (sync and/or async) before and after the fence must be ordered, and the compiler emits the minimal

```

# Code at CTA-scope, with blockDim=128

buf: f32[128] @ CudaSmemLinear

for tid in cuda_threads(0, 128, unit=cuda_thread):

buf[tid] = gmem[tid]

# __syncthreads

Fence(cuda_in_order,cuda_in_order)

for tid in cuda_threads(0, 128, unit=cuda_thread):

accum: f32 # Each thread sums up buf[...]

accum = 0

for i in seq(0, 128):

accum += buffil

```

combination of synchronization and memory-fence instructions required to satisfy them. The cuda\_in\_order timeline specifies that the effects of async instructions are *not* synchronized, but only regular synchronous instructions. If we were to, for example, replace the loads into shared memory with cp.async operations, the first parameter must be set to Sm80\_cp\_async so that the copy operations preceding the fence are completed before execution proceeds.

Split barriers use a shared barrier-typed variable z, declared as z: barrier @  $\pi_b$ , where  $\pi_b$  selects the completion mechanism (commit group, mbarrier, or cluster sync). Programmers express a split barrier statement pair with Arrive( $\tau_s^{\rm pre}$ ) >> z and Await(z,  $\tau_s^{\rm post}$ ). The statement pairing is determined by the shared barrier variable z. A matching pair orders memory operations prior to Arrive (filtered by  $\tau_s^{\rm pre}$ ) with those after Await (filtered by  $\tau_s^{\rm post}$ ). The right-hand inset illustrates replacing the earlier Fence example with an mbarrier-based split barrier.

## 2.2 Exo-GPU Examples with Erroneous Synchronization

To motivate our language design, we build up a series of increasingly subtle, hard-to-identify interand intra-thread synchronization bugs; all would be rejected by synchronization checking (Section 5). Variables prefixed with some\_\* are allocated outside the code snippet, some\_in\_order\_op represents non-async work, and example\_tma\_multicast and example\_wgmma are simplified placeholders for actual TMA (tile copy) and wgmma (tensor core) instructions.

The first example illustrates an inter-thread synchronization bug involving a cluster with 2 CTAs:

```

B: f32[2, 256, 32] @ CudaSmemLinear # Distributed mem: B[0,:,:] on CTA 0; B[1,:,:] on CTA 1

for cta in cuda_threads(0, 2, unit=cuda_cta_in_cluster):

some_in_order_op(B[cta, :, :])

Fence(cuda_in_order, cuda_in_order) # __syncthreads

example_tma_multicast(B[:,:,:], some_gmem[:,:]) # Copy some_gmem[:,:] to B[0,:,:] and B[1,:,:]

```

The example\_tma\_multicast instruction is implemented by threads in the 2 CTAs cooperating to fill each others' shared memory; however, this cooperation does not entail implicit synchronization between the two CTAs. Since the Fence statement, as placed in CTA-scope, only synchronizes threads within a CTA, it is possible that threads in CTA 0 proceed to the multicast instruction, filling the SMEM of CTA 1 (B[1,:,:]), while threads in CTA 1 are still reading from it while executing some\_in\_order\_op. Although the TMA instruction is async, this is not relevant to the bug illustrated here, as the TMA appears after the in-order operations upon which it races with.

The next example illustrates an intra-thread synchronization bug:

```

D: f32[2, 2, 64, 256] @ Sm90_RmemMatrixD(64, 256) # Distributed: D[x,y,:,:] on CTA x, warpgroup y

for cta in cuda_threads(0, 2, unit=cuda_cta_in_cluster):

for wg in cuda_threads(0, 2, unit=cuda_warpgroup):

example_wgmma(D[cta, wg, :, :], some_A[:, :], some_B[:, :]) # D += matmul(A, B)

some_in_order_op(D[cta, wg, :, :])

```

This code parallelizes across CTAs and warpgroups, with each warpgroup accessing only its own shard D[cta, wg, :, :]. Nevertheless, the code is flawed, as the async example\_wgmma instruction isn't waited-for before some\_in\_order\_op attempts to access its output.

A more subtle bug arises when async instructions interact with inter-thread synchronization:

```

B: f32[2, 256, 32] @ Sm90_SmemSwizzled(128)

# Distributed: B[x,:,:] on CTA x

D: f32[2, 2, 64, 256] @ Sm90_RmemMatrixD(64, 256) # Distributed: D[x,y,:,:] on CTA x, warpgroup y

cg: barrier[2, 2] @ CudaCommitGroup

# Distributed: cg[x,y] for CTA x, warpgroup y

for cta in cuda_threads(0, 2, unit=cuda_cta_in_cluster):

for wg in cuda_threads(0, 2, unit=cuda_warpgroup):

-some_in_order_op_1(B[cta, :, :])

example_wgmma(D[cta, wg, :, :], some_A[:,:], B[cta, :, :]) # D += matmul(A, B)

Arrive(wgmma_async) >> cg[cta, wg] -

cs: barrier @ CudaClusterSync

for cta in cuda_threads(0, 2, unit=cuda_cta_in_dluster):

for wg in cuda_threads(0, 2, unit=cuda_warpgroup):

Await(cg[cta, wg], cuda_in_order, 0)

some_in_order_op_2(D[cta, wg, :, :])

Await(cs, cuda_in_order, 0)

example_tma_multicast(B[:,:,:], some_gmem[:,:]) # Copy some_gmem[:,:] to B[0,:,:] and B[1,:,:]

```

The statements connected in blue on the left illustrate safe synchronization in a situation similar to our first example: the Arrive/Await pair using cs (cluster sync) ensures all accesses to B by some\_in\_order\_op\_1 finish before any thread in the cluster overwrites B using TMA. The statements connected in blue on the right illustrate safe synchronization in a situation similar to our second example: the Arrive/Await pair using cg (commit group) ensures each warpgroup waits for its example\_wgmma to finish before accessing D[cta, wg...] in some\_in\_order\_op\_2.

However, the bolded access to **B** by example\_wgmma is unsafe. Dotted red arrows illustrate synchronization that does *not* happen. Because the Arrive on cs uses the timeline cuda\_in\_order, the completion of the Arrive does not depend on the prior async wgmma instructions to retire. Meanwhile, the Await on cg (commit group) occurs too late for it to interact transitively with the prior cs (cluster sync) Arrive. Therefore, while all *non-async* accesses to B will retire before any thread proceeds to the TMA multicast, this isn't the case for the async wgmma instructions, whose B operand could be overwritten unexpectedly by another CTA multicasting to its input memory. Subtle bugs like this can be difficult to spot in optimized CUDA code.

## 2.3 Optimization Process and Equivalence Checking

Exo-GPU programmers can either directly write optimized object code or apply a sequence of scheduling transformations to simple initial code. Both approaches grant full control over performance-critical details. However, the scheduling approach offers significant practical advantages for performance engineering: optimization strategies become reusable functions across similar kernels, complex transformations decompose into sequences of verified primitives that enable rapid iteration with correctness guarantees, and the compiler automatically handles complex index calculations for tiling strategies—especially valuable for GPU optimization. Below, we describe Exo-GPU's scheduling-based optimization process.

| v : Var                                                                               |              | $y \in \mathbb{Y}$                                                                                                       | data variable<br>control variable                            |           |              |                                                                                   |                                                                                          |

|---------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------|--------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

|                                                                                       |              | $z \in \mathbb{B}$ $r \in \mathbb{W}$                                                                                    | barrier variable<br>warp variable                            | c : CExpr |              | y                                                                                 | integer<br>reads                                                                         |

| $e: \mathrm{DExpr}$ $e_{\mathrm{z}}: \mathrm{ZExpr}$ $e_{\mathrm{w}}: \mathrm{WExpr}$ | <br> <br>::= | $x \mid x \lceil w^* \rceil$<br>$e_1 + e_2 \mid e_1 - e_2 \mid e_1 * e_2 \mid e_1 / e_2$<br>$z \mid z \lceil w^* \rceil$ | data value<br>reads<br>compound expr<br>reads<br>warp config | b : BExpr | ::=<br> <br> | $b_1$ and $b_2 \mid b_1$ or $b_2$<br>$c_1 == c_2 \mid c_1 < c_2 \mid c_1 \le c_2$ | affine arith<br>quasi affine<br>boolean<br>logical ops<br>relational ops<br>point access |

| n<br>t<br>d                                                                           | _            | Bool                                                                                                                     | integer<br>boolean<br>data values                            |           |              | $c_1c_2$                                                                          | interval access                                                                          |

Fig. 1. The syntax of variables and expressions of GPU IR. We use  $\cdot^{*}$  to mean 0 or more.

The scheduling flow in Exo-GPU begins with a simple initial procedure  $p_1$ . The programmer issues a series of *rewrite operations*  $R_1 \dots R_{N-1}$  to create transformed procedures  $p_2 \dots p_N$ .

Rewrites:

$$p_1 \xrightarrow{R_1} p_2$$

...  $\xrightarrow{R_{N-1}} p_N$  (Exo-GPU checks)  $p_N$

Behavior:  $\operatorname{seq} \llbracket p_1 \rrbracket \equiv \operatorname{seq} \llbracket p_2 \rrbracket$  ...  $\equiv \operatorname{seq} \llbracket p_N \rrbracket \equiv \operatorname{par} \llbracket p_N \rrbracket$

Exo's scheduling rewrite verifies functional equivalence of  $\operatorname{seq} \llbracket p_1 \rrbracket$  ... $\operatorname{seq} \llbracket p_N \rrbracket$  under sequential semantics (denoted  $\operatorname{seq} \llbracket ... \rrbracket$ ). Exo-GPU adds new scheduling operations for parallel and synchronization constructs, but these non-semantics-altering annotations are ignored under  $\operatorname{seq} \llbracket ... \rrbracket$  checks. Then Exo-GPU performs additional verification on the final program  $p_N$ . Specifically, synchronization checking ensures  $\operatorname{seq} \llbracket p_N \rrbracket \equiv \operatorname{par} \llbracket p_N \rrbracket$ , where  $\operatorname{par} \llbracket ... \rrbracket$  denotes parallel semantics. Transitively, this completes the *chain of equivalence* from  $\operatorname{seq} \llbracket p_1 \rrbracket \equiv ... \equiv \operatorname{seq} \llbracket p_N \rrbracket \equiv \operatorname{par} \llbracket p_N \rrbracket$ , guaranteeing that  $p_1$ 's behavior is preserved throughout all transformations.

Equivalence checking relies on three categories of reasoning:

**Exo Rewrites:** Exo's existing rewrites implement dependency analysis-based equivalence checking, which guards against *dataflow logic bugs*. For example, reorder\_stmts, which reorders two statements  $s_1$ ;  $s_2$ , is only permitted when the effects of the statements commute.

**Instruction Substitution:** Explicit instruction selection rewrite (replace) lets programmers substitute a code block with an accelerator instruction call. Exo-GPU models instructions via their *behavior* (sequential semantics), per-parameter *memory type* (physical memory and layout), expected collective unit  $\tau_u$ , and async annotations. Exo's unification verifies that the replaced code block's behavior matches the instruction, while Exo-GPU's static analysis ensures appropriate threads execute it (Section 4.1); together preventing *instruction logic errors*.

**Exo-GPU Synchronization Check:** Since parallel loops and synchronization statements (Fence, Arrive, and Await) are ignored during sequential checks, synchronization checking must ensure that their usage is valid and does not alter program behavior or introduce race conditions. We verify this via interpretation on the Abstract Machine (Section 5), which protects the program against both *inter- and intra-thread synchronization bugs* for selected concrete problem sizes.

#### 3 GPU IR

GPU IR is the frontend language of Exo-GPU, and examples in Section 2 are written in GPU IR.

# 3.1 Variables and Expressions

Figure 1 defines the expression syntax of GPU IR. GPU IR explicitly distinguishes between control, data, barrier, and warp expressions and is a static control program. We denote the sets of data, control, barrier, and warp variables by  $\mathbb{X}$ ,  $\mathbb{Y}$ ,  $\mathbb{B}$ ,  $\mathbb{W}$ , respectively.  $x \in \mathbb{X}$  is a data variable,  $y \in \mathbb{Y}$

is a control variable,  $z \in \mathbb{B}$  is a barrier variable, and  $r \in \mathbb{W}$  is a warp variable. The truth values Bool  $\triangleq \{\text{true}, \text{false}\}$ . are ranged over by a metavariable t, and n is the metavariable for  $\mathbb{Z} \triangleq \{\cdots, -1, 0, 1, 2, \cdots\}$ . The metavariable  $d \in \mathbb{D}$  ranges over data values, including 8-, 32-, and 64-bit integers as well as single- and double-precision floating-points.

Control expressions CExpr encompass integer, scalar read, and (quasi-) affine arithmetic operations. Boolean expressions BExpr define basic logical and relational operations on control expressions. Data expressions DExpr are similarly defined, but operations need not be affine. Barrier Expressions ZExpr are only allowed to read, but not composed. Window coordinates  $w^*$  (we use .\* to denote a tuple) used in data and barrier read accesses are specified as a tuple of point-wise or interval control expressions, expressing a windowed access to multi-dimensional arrays. Scalar read is syntactic sugar for an array access of  $w^* = \langle \rangle$  (empty tuple).

# 3.2 Types

All types are fully defined in Appendix A. This section provides a general introduction to the different types in GPU IR. Figure 10 defines data and barrier types. Data types  $\tau_x$  specify precisions for data variables  $\mathbb{X}$ , such as f32 and i32. Barrier types  $\tau_z$  distinguish a non-explicitly guarded barrier from an explicitly guarded barrier (barrier(z)); the explicitly guarded barrier case is required only for mbarriers. A *collective type* ( $\delta \in \Delta$ ) defines a tuple consisting of a domain and a box, each representing d- dimensional natural numbers (( $\mathbb{N}^d, \mathbb{N}^d$ )). Together, these define a d-level thread hieararchy within a thread cluster, and a selection of a number of elements on each level. An argument to cuda\_threads loop  $\tau_u$  is parameterized by a collective type  $\delta$ , which is defined in Figure 11. Figures 12–14 classify three categories of memory spaces:  $\pi_d$  for data memories (such as CudaRmem for CUDA registers),  $\pi_z$  for barrier completion mechanisms (such as mbarrier or commit\_group), and  $\pi_w$  for special window aliasing (such as CUtensorMap). Similar to  $\tau_u$ ,  $\pi_d$  is parameterized by  $\delta$ .

A qualitative timeline  $\tau_q$  annotates each  $\mathit{runtime}$  buffer access. We define distinct  $\tau_q$  to distinguish between buffer accesses that require different synchronization mechanisms or memory fences to resolve hazards. For example, we distinguish non-async copies from cp. async copies (which require cp. async.wait\_all or similar to wait for), and we distinguish register and SMEM operands of wgmma instructions (which require wgmma.fence and fence.proxy.async, respectively). Section 5 will formally define how a runtime buffer access instance  $x[i_1,\ldots,i_n]$  tagged with  $q_1$  states that, at the program point and thread, the access to x occurs under  $q_1$ . Moreover, the sync timelines SyncTL mentioned in Section 2.1, which parameterize synchronization statements, are actually defined as compositions of qualitative timelines (QualTL), as shown in Figure 16.

## 3.3 Programs

Exo-GPU supports two types of procedures, p: Proc, which models CPU functions (possibly containing CUDA kernel launches), and g: Instr, which models hardware instructions for either CPU or CUDA. Both procedure types share three common components: a statement body that defines sequential behavior, a tuple of control parameters  $y^*$ , and a tuple of data parameters  $x^*$ . Each data parameter in Proc carries two annotations:  $\tau_x$ , specifying the required data precision, and  $\pi_d$ , specifying the required memory type for the passed argument.

Instruction parameters  $(\tau_a)$  also carry both  $\tau_x$  and  $\pi_d$  annotations, as well as hardware-specific information, namely: out-of-order, convergence, and qualitative timeline information, which all affect only abstract machine semantics for checking (Section 5). The  $\tau_a$  also contains a distributed collective units tuple  $(\tau_u^*)$  specifying the CUDA thread hierarchy at which each array dimension is sharded (checked by distributed memory analysis, Section 4.1). The instruction (g) contains annotations for t (a CPU/CUDA flag), a collective unit  $\tau_u$  specifying the convergent threads required, and  $\pi_z$  and  $\tau_u^*$ .

```

s: Stmt := s_1; s_2

sequencing

\mid for y in \operatorname{seq}(c_{\operatorname{lo}},c_{\operatorname{hi}}) do s

sequential loop

cuda tasks

\mid for y in cuda_tasks(c_{

m lo},c_{

m hi}) do s

| for y in cuda_threads(c_{lo}, c_{hi}, unit=\tau_u) do s cuda threads

| with CudaDeviceFunction(n, \, e_{\mathrm{w}}^*) do s

CUDA device function block

with CudaWarps(n, n, r) do s

Warp Specialization Block

if b then s

p(c^*, e^*)

non-instruction subprocedure call

q(c^*, e^*) >>

instruction subprocedure call

x[c^*] = e

x[c^*] += e

reduce

window statement

x = x[w^*] @ \pi_w

x: \tau_{\mathbf{x}}[c^*] @ \pi_{\mathbf{d}}

Data alloc

Barrier alloc

z: \tau_z[c^*] @ \pi_z

free x

Data free

free z

Barrier free

Fence(\tau_s, \tau_s)

Non-split barriers

Arrive(\tau_s, n) >> e_{\tau}^*

Arrive

Await(e_z, \tau_s, n)

Await

\tau_a : \operatorname{Arg} := \tau_x

data type (precision)

data memory type

out_of_order ∈ Bool

out-of-order execution flag

convergent ∈ Bool

implicit thread sync flag

distributed collective units

| initial_qual_tl \in QualTL

initial qualitative timeline

| \ \mathsf{ext\_qual\_tl} \in \mathcal{P}(\mathsf{QualTL})

extended qualitative timeline set

| atomic_qual_tl \in \mathcal{P}(QualTL)

atomic qualitative timeline set

p: \mathsf{Proc} \coloneqq \frac{\mathsf{proc}\ y^*, (x: \tau_x \ \exists\ \pi_d)^*}{\mathsf{proc}\ }

proc y^*, (x : \tau_a)^*, t, \tau_u, \pi_z, \tau_u^*

q : Instr ::=

do s

do s

```

Fig. 2. The syntax of GPU IR statements.

#### 3.4 Statements

345

346

347

353

357

359

361

363

365

366

367

368

369 370

371

372

373

374

375

376

377

378

379

380

381

382

383

384

385

386

387

388

389

390

391 392 Figure 2 defines statements  $s \in Stmt$ . A statement can sequence  $(s_1; s_2)$ , iterate over loops (seq, cuda\_tasks, or cuda\_threads), and guard (if b then s). Data effects include indexed writes  $x[c^*] = e$ , reductions  $x[c^*] += e$ , and window creation  $x = x[c_{lo} : c_{hi}] \otimes \pi_w$ . CudaDeviceFunction and CudaWarps control generation and selection of CUDA threads. Synchronization statements Fence, Arrive, and Await get lowered to CUDA synchronization and proxy fence instructions.

```

CUDA Kernel Structure: All Exo-GPU with CudaDeviceFunction(...):

code is compiled as CPU code by default. A CudaDeviceFunction block specifies a CPU-side launch of a CUDA kernel. Its body must contain only a single statement: a nest of one or more cuda_tasks loops; cuda_tasks loops must not appear elsewhere. Each iteration of the innermost cuda_tasks loop comprises a device task and is assigned to one CUDA cluster for execution.

```

The device scope of a statement is CPU if outside of a CudaDeviceFunction block, and GPU if inside. At CPU scope, all loops must have loop mode seq. The arguments of CudaDeviceFunction  $(n, e_w^*)$  respectively define the clusterDim and, indirectly, the blockDim of the CUDA clusters launched. Each warp expression  $e_w: r = (n, n, n)$  defines a group of warps named r, with the first n parameter being the number of warps. If nonzero, the latter two n parameters specify that the warps will adjust the register count down or up, respectively, using a setmaxnreg. dec or setmaxnreg. inc instruction [18]. We infer that blockDim is 32 times the total number of warps named.

Thread Control: Having described the cuda\_tasks loops (inter-cluster parallelism), we now describe cuda\_threads loops and with CudaWarps (intra-cluster parallelism). A cuda\_threads loop takes its the executing threads in flight and sub-divides it, assigning one subdivision to execute each loop iteration (possibly with left-over, inactivated threads). The unit parameter adjusts the number of

393

394

395

396

397

398

402

406

408

409 410

412

413

414 415

416

417

418 419

420

421

422

423

424

425

426

427

428

429

430

431

432

433

434

435

436

437

438

439

440 441

```

my_warp_config = [

CudaWarpConfig("producer", 1, 40, 0),

CudaWarpConfig("unused",

3, 40, 0),

CudaWarpConfig("consumer", 8, 0, 232)]

with CudaDeviceFunction(clusterDim=2,

warp_config=my_warp_config):

```

Fig. 3. Launching clusters of 2 CTAs each, with 1 "producer", 3 "unused", and 8 "consumer" warps per CTA (total blockDim=384). The consumer warps have 232 registers per thread, and the others only 40.

threads per iteration. The CudaWarps (n, n, r) block restricts its body statement to execute only with threads residing in the warp variable named by r (which is defined in the CudaDeviceFunction); the numeric arguments further restrict the warps selected.

**Proc & Instruction Calls:** Calls to p: Proc and q: Instruction are syntactically similar, distinguished only by the callable's type. Exo-GPU's static analysis enforces that calls to p: Proc only appear at CPU scope, while calls to g: Instrappear at CPU or CUDA scope as appropriate for g. For CUDA instructions, calls to g must only appear at  $\tau_u$ -scope, where  $\tau_u$  is the collective unit specified for g. Additionally, each data parameter must have the correct precision  $\tau_x$  and memory type  $\pi_d$ , and the trailing barrier (if required) must have the correct  $\pi_z$ .

Synchronization Statements: The user specifies synchronization between threads and/or between async accelerator instructions by inserting synchronization statements. They take synchronization timeline (SyncTL) parameters, defined as compositions of qualitative timelines and a transitivity (trnstv?) flag (Figure 16). The transitivity flag controls interaction between synchronization statements, detailed in Section 5.

Each  $\tau_s$ : SyncTL contains two QualTL sets: the full timeline set (indicated by "full" in (Figure 16), and a temporal timeline set (indicated by "full" or "temp."). A Fence  $(\tau_s^{\text{pre}}, \tau_s^{\text{post}})$ , or paired Arrive( $\tau_s^{\text{pre}}$ ,\_) and Await(\_,  $\tau_s^{\text{post}}$ ,\_) statements, resolves hazards between two accesses to the same array element when: (1) the first access precedes synchronization and uses a QualTL from  $\tau_s^{\rm pre}$ 's full timeline set, and (2) the second access follows synchronization and uses a QualTL from  $\tau_{\rm s}^{\rm post}$ ,'s full timeline set (for reads) or temporal timeline set (for writes). In hardware terms, the distinction between the full and temporal timeline sets is due to memory fences. If the prior value of a buffer element is *overwritten*, without being read, we require only that the overwrite is temporally ordered after prior accesses to that buffer element, and memory fences may be elided.

Alloc & Free: An allocation statement begins the lifetime of a new data or barrier variable. For data allocations, the data memory  $\pi_d$  determines the physical backing memory (registers (RMEM), shared memory (SMEM), or global memory (GMEM)) and the mapping between multidimensional tensor coordinates and 1D memory offsets (Figure 12). It also carries an implicit collective type  $\delta$ , specifying which level of the thread hierarchy at which the physical memory type is allocated (e.g. CTA for shared memory allocations); this is consumed by distributed memory analysis (Section 4.1). For barrier allocations, the BarrierComp parameter  $\pi_z$  controls the completion mechanism used for CUDA code translated from Arrive and Await statements (Figure 13). The explicitly-guarded barrier type is relevant only for certain configurations of mbarrier usage. A free statement ends the lifetime of a data or barrier variable. Currently, we forbid the user from inserting free statements manually; these are added automatically in a separate compiler pass.

**Window Statement:** A window statement  $x_{win} = x_{data}[w^*] \in \pi_w$  defines an alias to  $x_{data}$ . A window into  $x_{\text{win}}$  can be passed as an instruction argument which requires special window type  $\pi_w$ . Currently, we only use this feature to construct CUtensorMap objects [18] required for TMA instructions; we parameterize the CUtensorMap type with its swizzle mode and box shape.

## 4 COLLECTIVE ANALYSIS

Collective analysis is a static, forward dataflow analysis over a GPU IR procedure. Its results are consumed by (1) a memory analysis, (2) code generation, and (3) an abstract-machine interpreter. The analysis annotates every GPU lexical scope with a collective tiling  $\omega \in \Omega$ . By default, statements inherit their parent's tiling unchanged; a new tiling is derived only at: device entry (CudaDeviceFunction), thread loops (cuda\_threads), and warp-specialization blocks (CudaWarps). The purpose of this analysis is to statically reason about the mapping between work and the threads within clusters, so here we ignore cuda\_tasks loops, which distribute work across clusters. We uniquely identify a thread within a cluster by its natural thread index; a set of such indices comprises a thread collective  $\mu \in \mathbb{T}$ , where  $\mathbb{T} \triangleq \mathcal{P}(\mathbb{N})$ .

**Definition 4.1** (Natural thread index). The *natural thread index* for a CUDA thread is cluster\_ctarank \* blockDim.x + threadIdx.x. (Exo-GPU only parallelizes on the x dimension).

**Definition 4.2** (Collective tiling). A collective tiling  $\omega \in \Omega$  for an M-dimensional domain is an M-tuple of dimension descriptors

$$\omega = \langle \mathcal{D}_0, \dots, \mathcal{D}_{M-1} \rangle$$

with  $\mathcal{D}_m = (D_m, O_m)$ ,

where  $D_m \in \mathbb{N}$  is the extent of dimension m and  $O_m \in O^*$  is an ordered list of (possibly empty) dimension operators  $O: \mathbb{Y} \times \mathbb{N}^3$ . We write the thread pitch of dimension m as  $P_m \triangleq \prod_{i=m+1}^{M-1} D_i$  where  $P_{M-1} = 1$ .

The dimensions of a collective tiling  $\omega$  capture how a cluster's threads are partitioned into hierarchical collectives (cluster, block, warp). We support *reshape* to introduce ad-hoc additional hierarchy (e.g. pairs of warps). From there, each dimension's dimension operators summarize the control variables (identified by  $y \in \mathbb{Y}$ ) that iterate on that dimension. The thread pitch of the dimension describes the distance, in units of natural thread indices, between adjacent elements (e.g. a CTA dimension would have thread pitch blockDim).

During forward dataflow analysis, new collective tilings are derived for the three special statements mentioned above, while all other statements inherit their parent's tiling. It produces a child collective tiling through the following transformation:

$$derive_{\omega}: (\omega^{env}, \delta^{stmt}, y, lo, hi, tileCount) \rightarrow \omega'$$

where  $\omega^{\text{env}}$  is the parent scope's collective tiling and  $\delta^{\text{stmt}}$  is the collective type from the statement. The (optional) iterator y and bounds [lo, hi) describe a regular slice of linear thread space; tileCount  $\in \mathbb{N}$  is the number of tiles for that slice.

The cuda\_threads loop and CudaWarps block use derive $_{\omega}$  to create a new collective tiling  $\omega$  based on the one annotating the parent scope. The CudaDeviceFunction block derives  $\omega$  based on launch parameters:  $\omega$  is 1-D if clusterDim= 1 (domain  $D_0$ =blockDim), otherwise 2-D with  $(D_0, D_1)$ =(clusterDim, blockDim); all operator lists start empty.

The implementation of derive $_{\omega}$  proceeds in two steps:

- (1) Shape alignment. Make  $\omega^{\text{env}}$  and  $\delta^{\text{stmt}}$  compatible by reshaping via hierarchical splits so that their thread pitches  $P_m$  align.

- (2) Single-dimension refinement. After alignment, at most one dimension m is newly tiled; the derivation appends exactly one operator to  $O_m$ .

Once a tiling  $\omega$  is derived, it is compiled into a *thread mapping*:  $f_{\omega}: \Sigma \to \mathbb{T}$ , where  $\Sigma \triangleq (\mathbb{Y} \to \mathbb{Z})$  which maps a control environment  $\sigma \in \Sigma$  to a runtime thread collective  $\mu \in \mathbb{T}$ . Equivalently, let  $\mathcal{F} \triangleq \{f \mid f: \Sigma \to \mathbb{T}\}$  and  $f_{\omega} \in \mathcal{F}$ . During conversion, each Abstract Machine statement  $s^{\#}$  is annotated with its thread mapping  $f_{s^{\#}} \in \mathcal{F}$ . In Section 5.3 we write  $f_{s^{\#}}$  for the thread mapping associated with statement  $s^{\#}$ .

## 4.1 Distributed Memory Analysis

Distributed memory analysis is a static, program-wide consistency check that ensures every use of CUDA-scoped data and barrier variables is compatible with their memory definitions. Each memory type  $\pi_d$  specifies a collective type  $\delta_{\pi_d}$ . The analysis validates that allocation and use agree on which threads "own" which memory slices, indexing respects that ownership, and all uses induce the same mapping from logical indices to CUDA thread identifiers. Analysis runs in four steps:

- (1) **Desugaring instruction call.** To expose the implicit collective requirement encoded by each hardware instruction to the collective analysis in **step 2**, we rewrite instruction calls  $g(\cdots)$  into explicit loops. Each arguments to the instruction call are wrapped around with cuda\_threads, with their collective units specified by  $g.\tau_u^*$  in the instruction specification.

- (2) **Collective analysis.** Run collective analysis and annotate each scope with  $\omega \in \Omega$ .

- (3) **Triple collection.** For each data or barrier variable, record the *access triple* of all of use sites. We use  $\mathcal{T}_v$  to denote a set of those triples for a variable v; these sets for all the data and barrier variables are the sole inputs to **step 4**. Each triple  $(n^*, \omega, c^*)$  denotes: the subdivided dimensions  $n^*$ , the use-site tiling  $\omega$ , and observed index coordinates  $c^*$ . For each use site:

- **Data.** Compute  $n^*$  from the memory's collective type  $\delta_{\pi_d}$  and the use-site tiling  $\omega$ .

- Barriers. Treat all dimensions as subdivided (every axis participates in distribution).

- (4) **Triple analysis.** For each CUDA-scoped data variable v, we require: (i) consistency of the allocation w.r.t. the memory's  $\delta_{\pi_d}$ , (ii) consistency of data or barrier accesses across sites (by checking all triples in  $\mathcal{T}_v$ ), and (iii) all triples in  $\mathcal{T}_v$  must derive one and only one thread pitch tuple that summarizes how incrementing logical indices advances natural thread IDs.

As a result, distributed memory analysis rejects programs that (i) mismatch allocation and accesses with their memory declaration, (ii) inconsistently index the same data or barrier across sites, or (iii) rely on missing/extra CUDA-thread iterators. Passing guarantees that the program's memory behavior is coherent with its collective structure and declared memory types.

## 4.2 Code Generation to CUDA Code

Lowering cuda\_threads Loops: The correspondence between parallel loops and threads

lower(s);}

if (int y = f(blockIdx, threadIdx); g(y)) {

lower(s);}

has thus far been expressed in terms of thread mappings of type  $\Sigma \to \mathbb{T}$ , which infer a set of active threads from the control environment  $\sigma$ . However, the generated CUDA C++ implements the inverse of this mapping, inferring the value of a control variable y from the thread index instead. Each Exo-GPU loop of the form for y in cuda\_threads(lo, hi, unit= $\tau_u$ ) do s lowers to CUDA C++ as shown in the inset right. Here, f is a function of CUDA's built-in blockIdx and threadIdx variables, and g is a boolean condition on y that disables threads not assigned to execute any iteration of the body. Where possible, f is 0 and g is 1, to facilitate uniform branching.

**Warp Specialization:** When a device function uses multiple warp variables  $r_1, ..., r_W \in \mathbb{W}$ , we generate W-many CUDA C++ code paths from a single Exo-GPU device function, each specialized for (and executed by) the threads assigned to one warp variable. Each path uses PTX's setmaxnreg instruction to vary per-thread register counts, and omits all code paths guarded by a with CudaWarps block holding code not intended for the current warp. This allows the PTX assembler to statically verify that register-heavy instructions (e.g. wgmma) don't appear on low-register code paths.

**Persistent Kernels and cuda\_tasks Loops:** The generated CUDA C++ device functions implement a persistent kernel design that launches exactly the number of thread block clusters needed to saturate the device. Following the approach of CUTLASS grouped kernel schedulers [16], we implement a C++ task generator object that generates a series of device task coordinates for thread block clusters to execute. The current implementation orders tasks lexicographically and assigns them round-robin to thread block clusters for execution. While we leave it as future work to

| $\tau_v: \text{VL} \; \coloneqq \; \begin{array}{l} \text{fully\_ordered} \mid \text{temporally\_ordered} \\ \mid \text{unordered} \mid \text{atomic\_only} \mid \text{invisible} \end{array}$ | visibility levels                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| $e^{\#} : \operatorname{Expr}^{\#} ::= e_{d}^{\#} \mid e_{z}^{\#}  \text{where } e_{d}^{\#} \triangleq x[w^{*}]  e_{z}^{\#} \triangleq z[w^{*}]$                                               | barrier and data accesses                  |

| $s^{\#}: Stmt^{\#} \coloneqq s_1^{\#}; s_2^{\#}$                                                                                                                                               | sequencing                                 |

| $\mid$ for $y$ in $loop(c_{\mathrm{lo}}, c_{\mathrm{hi}})$ do $s^{\#}$                                                                                                                         | loop                                       |

| $\mid$ if $b$ then $s^{\#}$                                                                                                                                                                    | guard                                      |

| IncTaskID                                                                                                                                                                                      | increment the task ID                      |

| $\mid$ Alloc $(e^{\#})$                                                                                                                                                                        | Updates SyncEnv for Alloc                  |

| $\mid$ RecordRead $(	au_v, t, e^{\#}, 	au_q, 	au_q^{*}, e_{	exttt{z}}^{\#})$                                                                                                                   | Updates SyncEnv with Read                  |

| RecordMutate $(\tau_v, t, e^{\#}, \tau_q, \tau_q^*, e_z^{\#})$                                                                                                                                 | Updates SyncEnv with Mutate                |

| $\mid$ ClearReads $(e^{\#})$                                                                                                                                                                   | Remove state added by RecordRead           |

| $\mid$ ClearMutates $(e^{\#})$                                                                                                                                                                 | Remove state added by RecordMutate         |

| Fence $(t, 	au_q^*, 	au_q^*, 	au_q^*)$                                                                                                                                                         | Non-split barriers                         |

| Arrive $(t, \tau_{\boldsymbol{q}}^*, e_{\boldsymbol{z}}^{\#*})$                                                                                                                                | Arrive                                     |

| Await $(e_z^{\scriptscriptstyle \#},	au_{m{q}}^{\scriptscriptstyle \#},	au_{m{q}}^{\scriptscriptstyle \#},n)$                                                                                  | Await                                      |

| CheckReads $(	au_v, t, e^\#, 	au_q^*)$                                                                                                                                                         | Checks visibility of Reads in SyncEnv      |

| CheckMutates $(	au_v,t,e^{^{\#^1}},	au_{_{m{G}}}^*)$                                                                                                                                           | Checks visibility of Mutates in SyncEnv    |

| $\mid$ CheckBarrier $(e_{ m z}^{\#})$                                                                                                                                                          | Checks the consistency of arrive and await |

| $p^{\#}: \operatorname{Proc}^{\#} := \operatorname{proc} y^{*} \atop \operatorname{do} s^{\#}$                                                                                                 | arguments are control-only                 |

Fig. 4. Syntax of Abstract Machine IR (AMIR). Variables, types, and expressions (c, b, w) use the same definition as GPU IR. Visibility levels are denoted by the  $type \tau_v \in VL$  and range over the five constructors listed above.

provide a mechanism for programmers to customize this ordering, such customization would be unconstrained by frontend's quasi-affine indexing restrictions since cuda\_tasks loops impose no semantic ordering, thereby enabling techniques like Morton swizzling.

Shared Memory Allocations: Device functions generated by Exo-GPU use only dynamic shared memory for SMEM allocation. The Exo-GPU compiler deduces the required SMEM allocation size and statically assigns offsets into this allocation for each SMEM-backed variable. Variables with non-overlapping lifetimes may share the same memory locations; to ensure safe aliasing, we prohibit any thread in the cluster from passing an SMEM free statement until all reads and writes to the freed variable have retired, as enforced by the Abstract Machine (Section 5). This is necessary because freed SMEM may be immediately reused by any thread in the cluster. We note that the compiler's aliasing may be suboptimal, and the cluster-wide safety requirement may be overly conservative (e.g., for CTA-local variables). Providing programmers explicit control over SMEM lifetime and aliasing is left as future work.

#### 5 ABSTRACT MACHINE

To guarantee sequential—parallel equivalence, Exo-GPU performs synchronization checking via Abstract Machine interpretation. This section introduces the AMIR grammar (Section 5.1), the translation from GPU IR (Section 5.2), and the AMIR execution semantics (Section 5.3). We translate GPU IR into AMIR solely for validation: the frontend language remains simple, while synchronization reasoning is factored into explicit AMIR operations that are orthogonal to value computation.

#### 5.1 Abstract Machine Grammar

Figure 4 defines AMIR grammar. It follows GPU IR for control c, booleans b, window coordinates w, and all variable/type definitions (Figures 1, 2). AMIR defines only windowed access expressions, written  $e_d^\# \triangleq x[w^*]$  (data access) and  $e_z^\# \triangleq z[w^*]$  (barrier access). AMIR introduces visibility levels  $\tau_v \in \text{VL}$ , which are totally ordered: invisible < atomic\_only < unordered < temporally\_ordered < fully\_ordered.

| GPU IR                                                               | Abstract Machine IR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $s_1; s_2$                                                           | $T_s(s_1); T_s(s_2)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| for $y$ in $seq(c_{lo}, c_{hi})$ do $s$                              | for $y$ in $loop(c_{lo}, c_{hi})$ do $T_s(s)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| for $y$ in cuda_tasks $(c_{ m lo},c_{ m hi})$ do $s$                 | for $y$ in $loop(c_lo, c_hi)$ do (IncTaskID; $T_s(s)$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| for $y$ in cuda_threads $(c_{ m lo}, c_{ m hi}, 	au_{\it u})$ do $s$ | for $y$ in $loop(c_{lo}, c_{hi})$ do $T_s(s)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $x[c^*] \diamond e  where \diamond \in \{=, +=\}$                    | $\begin{aligned} ;_{e_1^\# \in T_{\mathrm{ex}}(e)} & \left( CheckMutates(\tau_v^{\mathrm{pre}}, false, e_1^\#, \{T_{\mathrm{qin}}(e_1^\#)\}) \right); \\ & RecordRead(\tau_v^{\mathrm{post}}, false, e_1^\#, T_{\mathrm{qin}}(e_1^\#), \emptyset, \emptyset) \right) \\ ;_{e_2^\# \in T_{\mathrm{ex}}(x[c^*])} & \left( CheckReads(\tau_v^{\mathrm{pre}}, false, e_2^\#, \{T_{\mathrm{qin}}(e_2^\#)\}) \right); \\ & CheckMutates(\tau_v^{\mathrm{pre}}, false, e_2^\#, \{T_{\mathrm{qin}}(e_2^\#)\}) \right); \\ & ClearReads(e_2^\#); \\ & ClearMutates(e_2^\#); \\ & RecordMutate(\tau_v^{\mathrm{post}}, false, e_2^\#, T_{\mathrm{qin}}(e_2^\#), \emptyset, \emptyset) ); \right) \\ , where & \tau_v^{\mathrm{post}} = fully-ordered \text{ and} \\ & \tau_v^{\mathrm{pre}} = fully-ordered \text{ if } +=, else \text{ temporally-ordered} \end{aligned}$ |

| if $b$ then $s$                                                      | if $b$ then $T_s(s)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| with CudaDeviceFunction( $n,\ e_{ m w}^*$ ) do $s$                   | Fence(true, Qcs $\cup$ {cpu_in_order_qual}, Qcs, Tcs);<br>$T_s(s)$ ;<br>Fence(true, Qcs, Qcs, Tcs);<br>, where Qcs $\triangleq$ $T_{afull}$ (cuda_stream_sync), Tcs $\triangleq$ $T_{qtmp}$ (cuda_stream_sync)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| with CudaWarps $(n, n, r)$ do $s$                                    | if true then $T_s(s)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $g(c^*,e^*)$ » $e_z$                                                 | $;_{e^{\#} \in T_{\mathrm{ex}}(e_z)} \text{ RecordRead(fully-ordered, false}, e^{\#}, \emptyset, \emptyset, T_e(e_z)) \\ \vdots \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $x: 	au_{x}[c^{*}] 	ext{ } 	ext{@ } 	ext{$\pi_{	ext{d}}$}$           | $Alloc(x[c^*])$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $z:	au_z[c^*]$ @ $\pi_z$                                             | $Alloc(z[c^*])$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| free x                                                               | $;_{e^{\#} \in T_{\operatorname{smem}}(x[:^*])} \text{ (CheckReads}(\tau_v^{\operatorname{free}}, \operatorname{false}, e^{\#}, \{T_{\operatorname{qin}}(e^{\#})\})); \\ \text{ CheckMutates}(\tau_v^{\operatorname{free}}, \operatorname{false}, e^{\#}, \{T_{\operatorname{qin}}(e^{\#})\}));)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| free z                                                               | $\begin{aligned} &\text{CheckBarriers(} \ T_e(z[:^*]) \ ); \\ &\vdots_{e^\# \in T_{\operatorname{smem}}(z[:^*])} \ &(\text{CheckReads(} \tau_v^{\operatorname{free}}, \operatorname{false}, e^\#, \{T_{\operatorname{qin}}(e^\#)\})); \\ & \text{CheckMutates(} \tau_v^{\operatorname{free}}, \operatorname{false}, e^\#, \{T_{\operatorname{qin}}(e^\#)\})); ) \end{aligned}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Fence( $	au_s^{	ext{pre}}, 	au_s^{	ext{post}}$ )                     | Fence( $T_{tr}(\tau_s^{pre})$ , $T_{qfull}(\tau_s^{pre})$ , $T_{qfull}(\tau_s^{post})$ , $T_{qtmp}(\tau_s^{post})$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Arrive $(	au_{	extsf{S}}, n) * e_{	extsf{Z}}^*$                      | $\mathbf{\hat{s}}_{e^{\#} \in T_{\mathrm{ex}}(e_{\mathrm{z}}^{*})}$ RecordRead(fully-ordered, false, $e^{\#}$ , $T_{\mathrm{qarr}}(\tau_{s})$ , $\emptyset$ , $\emptyset$ ) Arrive( $T_{\mathrm{tr}}(\tau_{s})$ , $T_{\mathrm{qfull}}(\tau_{s})$ , $T_{e}(e_{\mathrm{z}}^{*})$ );                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $Await(e_{\mathtt{z}},\tau_{\mathtt{S}},n)$                          | $\label{eq:condition} \begin{split} & \vdots_{e^\# \in T_{\mathrm{ex}}(e_Z)} \; \; RecordRead(fully-ordered, false, e^\#, T_{\mathrm{qin}}(e^\#), \emptyset, \emptyset) \\ & Await(T_{\mathrm{e}}(e_{\mathrm{z}}), \; T_{\mathrm{qfull}}(\tau_s), \; T_{\mathrm{qtmp}}(\tau_s), \; n)  ; \end{split}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Fig. 5.  $T_s$ : Stmt  $\rightarrow$  Stmt<sup>#</sup> (statement conversion). All *conversion* functions use the  $T_{-}$  prefix (Figures 18-20).  $\tau_n^{\text{free}} = \text{temporally-ordered}$

AMIR has no hardware-instruction procedures (g in GPU IR) and no subprocedure calls. Procedures  $p^{\#}$  take control-only arguments. The statement (Figure 4) consists of: (i) structural statements—sequencing, loop, and guard (ii) recording statements that update the synchronization environment SyncEnv-Alloc, RecordRead, RecordMutate, Fence, Arrive, and Await; and (iii) checking statements that query SyncEnv and fail if the required visibility obligations are not met; otherwise they are no-ops: CheckBarrier, CheckReads, and CheckMutates.

## 5.2 Conversion from GPU IR to Abstract Machine IR

We describe how GPU IR expressions (Section 5.2.1), statements (Section 5.2.2), and instruction arguments (Section 5.2.3) are converted. Before conversion, we apply two trivial preprocessing steps to GPU IR: (i) Inline all window statements, and (ii) Inline all subprocedure calls that occur outside any CudaDeviceFunction block. Throughout this section (and in figures) we use the following notation. For a finite, ordered variables  $R = \langle r_0, \dots, r_{k-1} \rangle$  and a statement template  $S(\cdot)$ ,  $;_{i=0}^k S(x) \triangleq S(r_0)$ ;  $S(r_1)$ ;  $\cdots$ ;  $S(r_{k-1})$ . If  $R = \emptyset$ , the result is no-op. The intent is purely left-to-right sequential composition at AMIR conversion time. When unambiguous, we write  $f(A) = \{ f(a) \mid a \in A \}$  for the pointwise image of a set.

- 5.2.1 Expression Conversion. Figure 17 defines  $T_e: \mathrm{DExpr} \cup \mathrm{ZExpr} \to \mathcal{P}(\mathsf{Expr}^{\sharp})$ , which extracts the windowed AMIR accesses  $e^{\#} \in \{x[w^*], z[w^*]\}:$  scalars d contribute nothing  $(\emptyset)$ ; a bare name x or z yields the degenerate accesses  $x[\langle \rangle]$  or  $z[\langle \rangle]$ ; explicit indexings  $x[w^*]$  and  $z[w^*]$  are preserved; and for arithmetic  $e_1$  op  $e_2$  the sets union,  $T_e(e_1) \cup T_e(e_2)$ .  $T_e$  is set-valued (order and duplicates are irrelevant), leaves the value expression unchanged, and merely supplies the converted  $\mathsf{Expr}^{\#}$  used by RecordRead/RecordMutate and subsequent visibility checks.

- 5.2.2 Statement Conversion. Figure 5 gives a structural translation  $T_s$ : Stmt  $\rightarrow$  Stmt# from GPU IR to AMIR. Helper functions referenced by Figure 5 are defined in Figure 18. Sequencing and conditionals are preserved, while all loops are normalized to the abstract loop form. Warp/block scopes are dropped and replaced with a guard whose condition is true. Assignments  $x[c^*] \diamond e$  ( $\diamond \in \{=,+=\}$ ) are lowered to explicit read/write effects. We expand source and destination with  $T_e$  and remove sync-exempt expressions via  $T_{ex}$ . Sync-exempt memories are those whose accesses can be assumed safe without checking: CudaGridConstant, CudaClusterSync, and CudaCommitGroup. Shared memories are the following: CudaBasicSmem, CudaSmemAtomicity16B, CudaSmemLinear, Sm90\_SmemSwizzled(B), or CudaMbarrier.

Hardware instruction calls ignore control arguments and pair the instruction's parameter definition and the arguments via  $T_{\rm arg}$ . The entry and exit of CudaDeviceFunction is bracketed with fences with cuda\_stream\_sync, capturing both the CPU-to-GPU fence implied by the kernel launch, and the serialization of the CUDA kernel with respect to prior and subsequent CUDA kernels and API calls (Note that Exo-GPU currently uses only one CUDA stream). During the conversion, we record the scope of each statement using a global environment Scope : Stmt\*  $\rightarrow$  {CPU, CUDA}. Statements outside the CudaDeviceFunction block are CPU-scoped, while those inside are GPU-scoped. The scope mapping is used in Definition 5.2. Fence, Arrive, and Await translate a sync timeline ( $\tau_s$ ) into a qualitative timeline set ( $\tau_q^*$ ).  $T_{\rm tr}$  queries whether a sync timeline is transitive;  $T_{\rm qfull}$  and  $T_{\rm qtmp}$  materialize the full and temporal QualTL sets, respectively. Arrive selects its arrival qualitative timeline via  $T_{\rm qarr}$  to sync-check the barrier itself, thereby preventing use-after-free bugs.

- 5.2.3 Instruction Argument Conversion. Figure 19 expands the conversion  $T_{\text{arg}}(g.p_i, e_i, e_z)$  from a GPU IR instruction call argument to the AMIR statements. The auxiliary projections and predicates referenced in the figure— $T_{\text{ext}}$ ,  $T_{\text{atom}}$ ,  $T_{\text{init}}$ ,  $T_{\text{ooo}}$ , and  $T_{\text{cvg}}$ —are defined in Figure 20. For each non-sync exempt expression  $e^{\#} \in T_{\text{ex}}(e_i)$ , the conversion emits a sequence of checks and effect-recording operations which depends on two properties of the parameter  $g.p_i$ : its access mode (read-only vs. write-only/read-write) and whether it is atomic. The access mode of  $g.p_i$  is determined by a simple intraprocedural static analysis over instruction body (behavior) g.s: if  $g.p_i$  is only read (and never written or reduced), it is classified as read-only; if it is written but never read or reduced, it is write-only; otherwise it is read-write. The atomic case is selected exactly when  $T_{\text{atom}}(g.p_i) \neq \emptyset$ .

- *5.2.4 Program Conversion.* The GPU IR's program proc  $y^*$ ,  $(x : \tau_x)^*$ ; do s is translated into an AMIR program proc  $y^*$ ; do  $s^{\#}$  where only control arguments are retained. Non-control arguments

$$\frac{\langle c_1,\sigma\rangle \Downarrow_{\mathbb{Z}} n}{\langle n,\sigma\rangle \Downarrow_{\mathbb{Z}} n} \text{ C-Int} \qquad \frac{\sigma(y)=n}{\langle y,\sigma\rangle \Downarrow_{\mathbb{Z}} n} \text{ C-Read} \qquad \frac{\langle c_1,\sigma\rangle \Downarrow_{\mathbb{Z}} n_1 \qquad \langle c_2,\sigma\rangle \Downarrow_{\mathbb{Z}} n_2 \qquad \text{op} \in \{+,-,*,/\}}{\langle c_1 \text{ op} c_2,\sigma\rangle \Downarrow_{\mathbb{Z}} (n_1 \text{ op} n_2)} \text{ C-Aff}$$

$$\frac{\langle b_1,\sigma\rangle \Downarrow_{\text{Bool}} t_1 \qquad \langle b_2,\sigma\rangle \Downarrow_{\text{Bool}} t_2 \qquad \text{op} \in \{\text{and, or}\}}{\langle b_1 \text{ op} b_2,\sigma\rangle \Downarrow_{\text{Bool}} \widehat{\text{op}} (t_1,t_2)} \text{ B-Log}$$

$$\frac{\langle c_1,\sigma\rangle \Downarrow_{\mathbb{Z}} n_1 \qquad \langle c_2,\sigma\rangle \Downarrow_{\mathbb{Z}} n_2 \qquad \text{op} \in \{==,<,\leq\}}{\langle c_1 \text{ op} c_2,\sigma\rangle \Downarrow_{\text{Bool}} (n_1 \text{ op} n_2)} \text{ B-Rel} \qquad \frac{\langle c,\sigma\rangle \Downarrow_{\mathbb{Z}} i}{\langle c,\sigma\rangle \Downarrow_{\mathbb{Z}} i} \text{ W-Point}$$