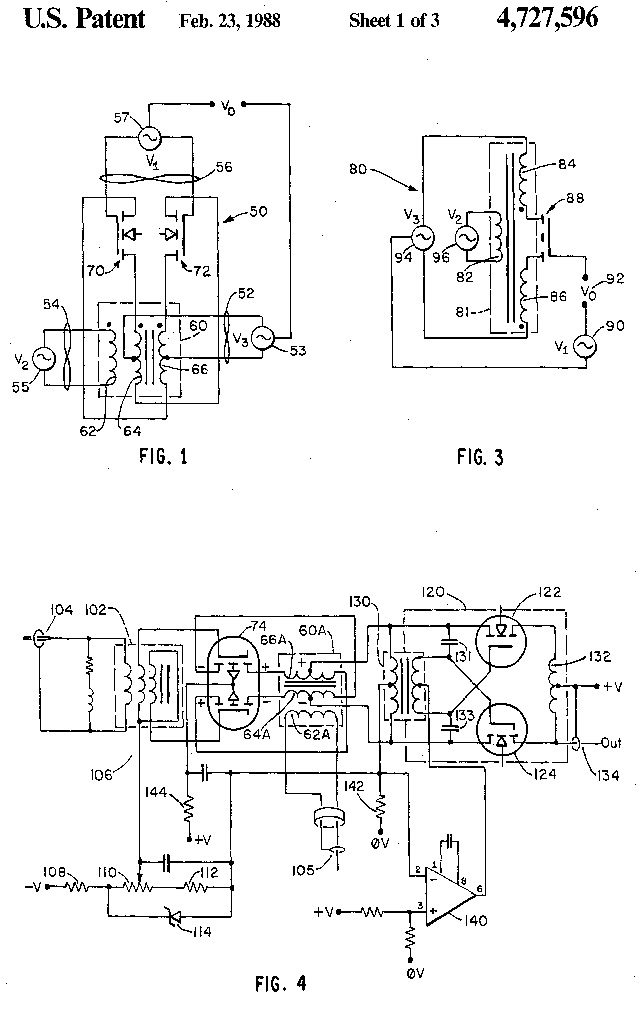

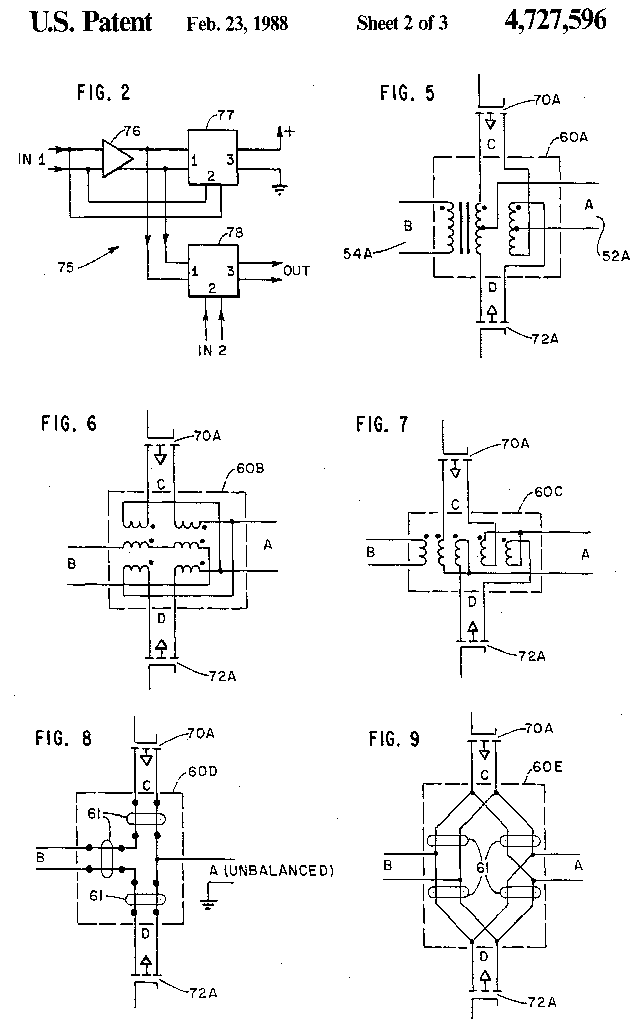

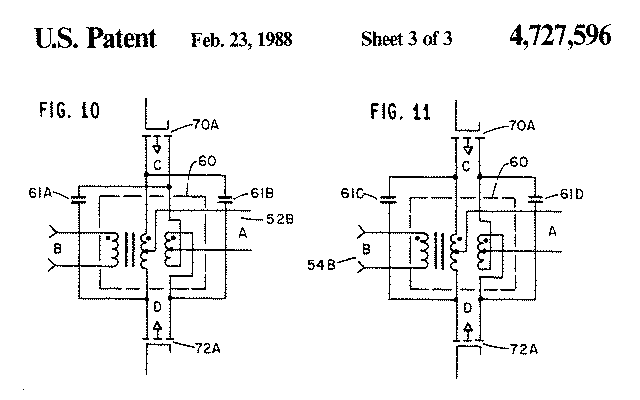

A high performance, double-balanced mixer comprising a novel transformer

and a pair of variable conductance semiconductor devices connected thereto

which provides an output signal being the product of two input signals.

Two transformer windings each include a center tap which together form one

port of the mixer. Each variable conductance devices provides a selected

conductivity path across the end of one of the center tapped windings to

the beginning of the other center tapped winding. A second port signal

provided oppositely modulates the variable conductance devices to provide

a decrease in conductivity across one path while increasing the

conductivity of the other path. The third winding of the transformer

provides a third port to the mixer. A singularly-balanced mixer embodiment

is shown. The mixer according to the present invention is operable to

provide vastly improved linearity for either of two inputs as well as low

noise and wide bandwidth operation.

Other References

|

Mixers for High Performance Radio, Professional Program Session Record 24,

Wescon 81, Electronic Show & Convention, Sep. 15-17, 1981, Brooks Hall &

Civic Auditorium, Hilton, Hotel San Francisco, CA, Program, pp. 1-4.

|

|

Symmetric MOSFET Mixers of High Dynamic Range, R. P. Rafuse, Session XI,

Circuit Techniques II, 1968 International Solid-State Circuits Conference,

pp. 122 & 123.

|

|

Modeling and Simulation of Insulated-Gate Field-Effect Transistor Switching

Circuits, H. Schichman and D. A. Hodges, IEEE J. Solid-State Circuits,

vol. SC-3, Sep. 1968, pp. 285-289.

|

|

Termination Insensitive Mixers, Peter Will, Adams Russel, Anzac Division,

one page.

|