Please visit the Adaptive and Secure Computing Systems (ASCS) Laboratory website for my current projects [Link]

Cognitive computing and the concept of self-aware adaptive computer architectures

Under this project we are

exploring the design of an architecture

that dynamically adapts and optimizes its execution behavior

according to a set of high-level application goals (e.g., performance

to power ratio, hard real-time constraints, reliability and security

awareness). It represents a new, non-Von Neumann model of

computation and provides a framework for future, cognitive,

probabilistic, and adaptive computer system architectures. Using

various machine learning and control theory techniques, it is able to:

reason about the trade-off between the precision of results and the

computational time or power consumption.

This new paradigm of probabilistic, approximate computing is

particularly appealing to many important and resource intensive

applications such as big data analytics, embedded systems, image and

video processing, and real-time signal or data processing, where under

some modalities, result accuracy can be traded-off for better

performance, hard real-time support, and energy efficiency.

Design space exploration methodologies and tools

We design Heracles, an open-source,

functional, parameterized, synthesizable multicore system toolkit. Such

a multi/many-core design platform is a powerful and versatile research

and teaching tool for architectural exploration and hardware-software

co-design. The Heracles toolkit comprises the soft hardware (HDL)

modules, application compiler, and graphical user interface. It is

designed with a high degree of modularity to support fast exploration

of future multicore processors of different topologies, routing

schemes, processing elements or cores, and memory system

organizations. The Heracles tool is

freely available under the open-source MIT license at: Heracles.

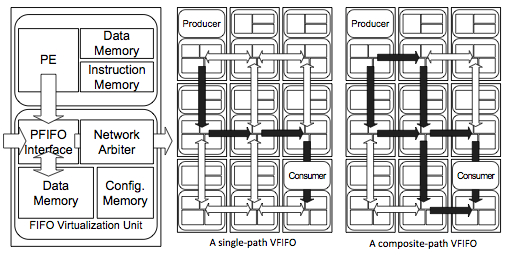

Reconfigurable and adaptive computer architectures

We develop

a high-level computation model with a grid of processing elements

(PEs), called Diastolic Arrays.

A diastolic array is a reconfigurable substrate that is meant to serve

as a co-processing platform in a larger self-adaptive system to speed

up applications or parts of applications that are throughput-sensitive

and latency tolerant. Diastolic arrays are coarser-grained than FPGAs

but finer-grained than multicores.

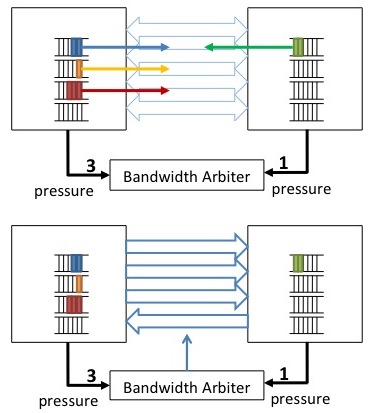

Adaptive Interconnect Network-on-Chip

My research in this

domain examines bandwidth-aware oblivious routing schemes for NoC

architectures. We introduce various non-minimal, oblivious routing

algorithms that globally allocate network bandwidth for a given

application when estimated bandwidths for data transfers are provided,

while ensuring deadlock freedom with no significant additional hardware.

We present methods that statically allocate channels to flows at each

link when oblivious routing is used, and ensure deadlock freedom for

arbitrary minimal routes when two or more virtual channels are

available. We propose on-chip bandwidth-adaptive networks to mitigate

the performance problems of oblivious routing and the complexity issues

of adaptive routing. In a bandwidth-adaptive network, the bisection

bandwidth of network can adapt to changing network conditions.

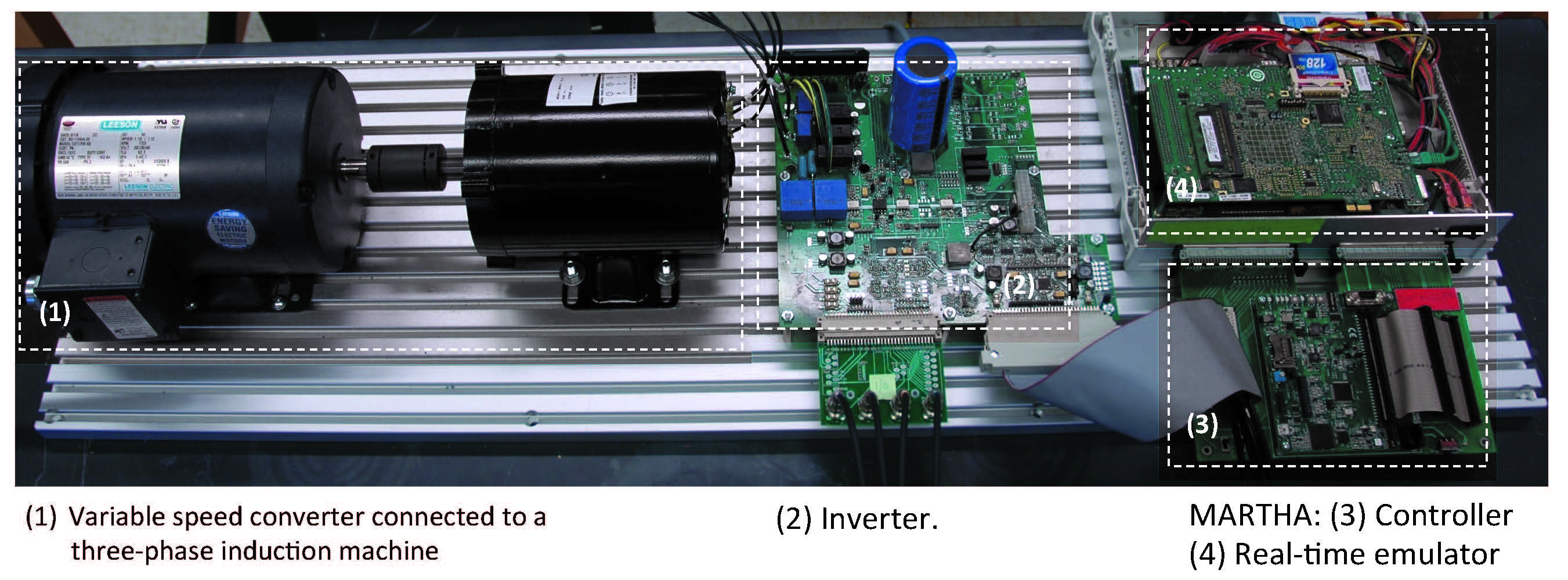

Resource-aware computer systems

We develop a

Multicore

Architecture for Real-Time Hybrid Applications (MARTHA) with time

predictable execution, low computational latency, and high performance

that meets the requirements for control, emulation and estimation of

next-generation power electronics and smart grid systems. Applications

are modeled as adaptive/switched hybrid automata (AHA/SHA). The MARTHA

architecture is resource and latency-aware. It has heterogeneous

processing units and full predictable execution capability.

Past Projects

Design Automation for Cyber-Physical Systems: Digital Emulation and Control of Power Electronics Systems

Institute for Soldier

Nanotechnologies

Institute for Soldier

Nanotechnologies

With Dr. Ivan Celanovic

Power electronics is one of the

key physical layers of the “smart grid” that enables highly efficient

and fully controllable flow of electric power, and promises to deliver

up to 30% electric energy savings across all aspects of the conversion

of primary energy into electricity. The current tools for prototyping

power electronics systems are largely based on analog modeling. This

method of simulation and testing is costly and inflexible because even

the smallest change in design requires rebuilding the analog system.

Pure software-based simulation tools are also not suitable because one

is unable to replicate real operational conditions that are critical to

the proper validation of the system under design. The goal of this work

is to raise the level of design tools for power electronics by

developing a new software/hardware design platform for comprehensive

controlling, testing and validation of power systems by means of

high-fidelity, real-time emulation of power electronics in Hardware

in-the-Loop (HiL) configurations. It permits proper validation of

operational scenarios by interfacing the platform with other physical

systems needed to model the environment. The validation includes the

ability to check system real-time responses and interfaces, to identify

failure modes, and to implement recovery states or redundancies in

critical circuits.

This work is now carried on by the MIT spin-off Typhoon HIL, Inc.